以太网在定制板上的 PROCESSOR-SDK-AM437X 上无法正常工作。

我们具有 在 MMC 卡上运行 PROCESSOR-SDK-AM437X Linux 的定制电路板。 对于 ethenet、我们将在下方进行起诉 DP83822HFRHBT PHY 支持,

为配置 kenel 它正在正常启动、但以太网 ping 功能不起作用

1) 1)附加的 定制板原理图

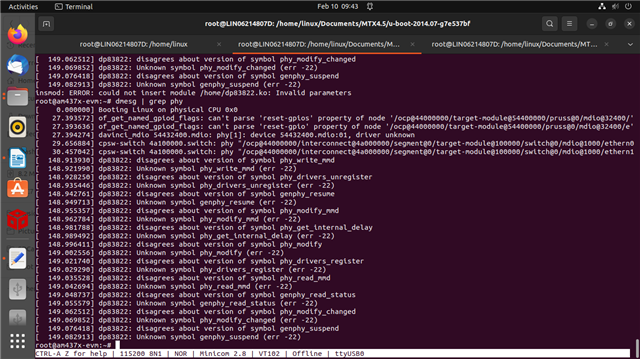

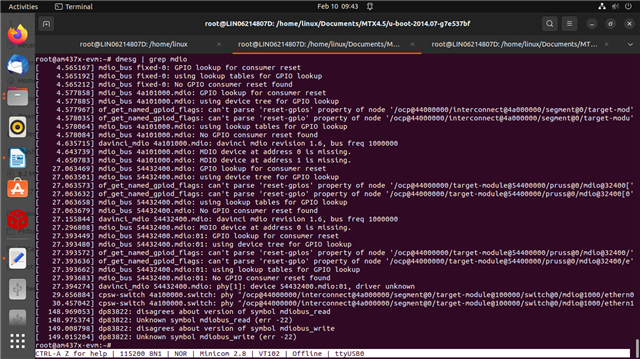

2)附有 cpsw,phy 日志的字幕,

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

以太网在定制板上的 PROCESSOR-SDK-AM437X 上无法正常工作。

我们具有 在 MMC 卡上运行 PROCESSOR-SDK-AM437X Linux 的定制电路板。 对于 ethenet、我们将在下方进行起诉 DP83822HFRHBT PHY 支持,

为配置 kenel 它正在正常启动、但以太网 ping 功能不起作用

1) 1)附加的 定制板原理图

2)附有 cpsw,phy 日志的字幕,

// SPDX-License-Identifier: GPL-2.0-only /* * Copyright (C) 2014 Texas Instruments Incorporated - https://www.ti.com/ */ /dts-v1/; #include "am4372.dtsi" #include <dt-bindings/pinctrl/am43xx.h> #include <dt-bindings/pwm/pwm.h> #include <dt-bindings/gpio/gpio.h> #include <dt-bindings/input/input.h> / { model = "TI AM437x ETH BOARD"; compatible = "ti,am437x-idk-evm","ti,am4372","ti,am43"; chosen { stdout-path = &uart0; }; aliases { ethernet2 = &pruss1_emac0; ethernet3 = &pruss1_emac1; }; v24_0d: fixed-regulator-v24_0d { compatible = "regulator-fixed"; regulator-name = "V24_0D"; regulator-min-microvolt = <24000000>; regulator-max-microvolt = <24000000>; regulator-always-on; regulator-boot-on; }; v3_3d: fixed-regulator-v3_3d { compatible = "regulator-fixed"; regulator-name = "V3_3D"; regulator-min-microvolt = <3300000>; regulator-max-microvolt = <3300000>; regulator-always-on; regulator-boot-on; vin-supply = <&v24_0d>; }; vdd_corereg: fixed-regulator-vdd_corereg { compatible = "regulator-fixed"; regulator-name = "VDD_COREREG"; regulator-min-microvolt = <1100000>; regulator-max-microvolt = <1100000>; regulator-always-on; regulator-boot-on; vin-supply = <&v24_0d>; }; vdd_core: fixed-regulator-vdd_core { compatible = "regulator-fixed"; regulator-name = "VDD_CORE"; regulator-min-microvolt = <1100000>; regulator-max-microvolt = <1100000>; regulator-always-on; regulator-boot-on; vin-supply = <&vdd_corereg>; }; v1_8dreg: fixed-regulator-v1_8dreg{ compatible = "regulator-fixed"; regulator-name = "V1_8DREG"; regulator-min-microvolt = <1800000>; regulator-max-microvolt = <1800000>; regulator-always-on; regulator-boot-on; vin-supply = <&v24_0d>; }; v1_8d: fixed-regulator-v1_8d{ compatible = "regulator-fixed"; regulator-name = "V1_8D"; regulator-min-microvolt = <1800000>; regulator-max-microvolt = <1800000>; regulator-always-on; regulator-boot-on; vin-supply = <&v1_8dreg>; }; v1_5dreg: fixed-regulator-v1_5dreg{ compatible = "regulator-fixed"; regulator-name = "V1_5DREG"; regulator-min-microvolt = <1500000>; regulator-max-microvolt = <1500000>; regulator-always-on; regulator-boot-on; vin-supply = <&v24_0d>; }; v1_5d: fixed-regulator-v1_5d{ compatible = "regulator-fixed"; regulator-name = "V1_5D"; regulator-min-microvolt = <1500000>; regulator-max-microvolt = <1500000>; regulator-always-on; regulator-boot-on; vin-supply = <&v1_5dreg>; }; gpio_keys: gpio_keys { compatible = "gpio-keys"; pinctrl-names = "default"; pinctrl-0 = <&gpio_keys_pins_default>; #address-cells = <1>; #size-cells = <0>; switch0 { label = "power-button"; linux,code = <KEY_POWER>; gpios = <&gpio4 2 GPIO_ACTIVE_LOW>; }; }; /* fixed 32k external oscillator clock */ clk_32k_rtc: clk_32k_rtc { #clock-cells = <0>; compatible = "fixed-clock"; clock-frequency = <32768>; }; leds-iio { status = "disabled"; compatible = "gpio-leds"; led-out0 { label = "out0"; gpios = <&tpic2810 0 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out1 { label = "out1"; gpios = <&tpic2810 1 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out2 { label = "out2"; gpios = <&tpic2810 2 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out3 { label = "out3"; gpios = <&tpic2810 3 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out4 { label = "out4"; gpios = <&tpic2810 4 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out5 { label = "out5"; gpios = <&tpic2810 5 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out6 { label = "out6"; gpios = <&tpic2810 6 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out7 { label = "out7"; gpios = <&tpic2810 7 GPIO_ACTIVE_HIGH>; default-state = "off"; }; }; /* Dual-MAC Ethernet application node on PRU-ICSS1 */ pruss1-eth { compatible = "ti,am4376-prueth"; ti,prus = <&pru1_0>, <&pru1_1>; sram = <&ocmcram>; interrupt-parent = <&pruss1_intc>; mii-rt = <&pruss1_mii_rt>; iep = <&pruss1_iep>; pinctrl-0 = <&pruss1_eth_default>; pinctrl-names = "default"; interrupts = <20 2 2>, <21 3 3>; interrupt-names = "rx_lre_hp", "rx_lre_lp"; pruss1_emac0: ethernet-mii0 { phy-handle = <&pruss1_eth0_phy>; phy-mode = "mii"; interrupts = <20 2 2>; interrupt-names = "rx"; ti,no-half-duplex; /* Filled in by bootloader */ local-mac-address = [00 00 00 00 00 00]; }; pruss1_emac1: ethernet-mii1 { phy-handle = <&pruss1_eth1_phy>; phy-mode = "mii"; interrupts = <21 3 3>; interrupt-names = "rx"; ti,no-half-duplex; /* Filled in by bootloader */ local-mac-address = [00 00 00 00 00 00]; }; }; }; &am43xx_pinmux { uart_0_pins_default: uart_0_pins_default { pinctrl-single,pins = < AM4372_IOPAD(0x170, PIN_INPUT | MUX_MODE0) // (K25) uart0_rxd.uart0_rxd AM4372_IOPAD(0x174, PIN_OUTPUT_PULLDOWN | MUX_MODE0) // (J24) uart0_txd.uart0_txd >; }; // Optional sleep pin settings. Must manually enter values in the below skeleton. uart_0_pins_sleep: uart_0_pins_sleep { pinctrl-single,pins = < AM4372_IOPAD(0x170, PIN_INPUT | MUX_MODE0) // (K25) uart0_rxd.uart0_rxd AM4372_IOPAD(0x174, PIN_OUTPUT_PULLDOWN | MUX_MODE0) // (J24) uart0_txd.uart0_txd >; }; gpio_keys_pins_default: gpio_keys_pins_default { pinctrl-single,pins = < AM4372_IOPAD(0x9b8, PIN_INPUT | MUX_MODE7) /* cam0_field.gpio4_2 */ >; }; i2c0_pins_default: i2c0_pins_default { pinctrl-single,pins = < AM4372_IOPAD(0x988, PIN_INPUT | SLEWCTRL_FAST | MUX_MODE0) /* i2c0_sda.i2c0_sda */ AM4372_IOPAD(0x98c, PIN_INPUT | SLEWCTRL_FAST | MUX_MODE0) /* i2c0_scl.i2c0_scl */ >; }; i2c0_pins_sleep: i2c0_pins_sleep { pinctrl-single,pins = < AM4372_IOPAD(0x988, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x98c, PIN_INPUT_PULLDOWN | MUX_MODE7) >; }; i2c2_pins_default: i2c2_pins_default { pinctrl-single,pins = < AM4372_IOPAD(0x9e8, PIN_INPUT | SLEWCTRL_FAST | MUX_MODE3) /* cam1_data1.i2c2_scl */ AM4372_IOPAD(0x9ec, PIN_INPUT | SLEWCTRL_FAST | MUX_MODE3) /* cam1_data0.i2c2_sda */ >; }; i2c2_pins_sleep: i2c2_pins_sleep { pinctrl-single,pins = < AM4372_IOPAD(0x9e8, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x9ec, PIN_INPUT_PULLDOWN | MUX_MODE7) >; }; mmc1_pins_default: pinmux_mmc1_pins_default { pinctrl-single,pins = < AM4372_IOPAD(0x900, PIN_INPUT | MUX_MODE0) /* mmc0_clk.mmc0_clk */ AM4372_IOPAD(0x904, PIN_INPUT | MUX_MODE0) /* mmc0_cmd.mmc0_cmd */ AM4372_IOPAD(0x9f0, PIN_INPUT | MUX_MODE0) /* mmc0_dat3.mmc0_dat3 */ AM4372_IOPAD(0x9f4, PIN_INPUT | MUX_MODE0) /* mmc0_dat2.mmc0_dat2 */ AM4372_IOPAD(0x9f8, PIN_INPUT | MUX_MODE0) /* mmc0_dat1.mmc0_dat1 */ AM4372_IOPAD(0x9fc, PIN_INPUT | MUX_MODE0) /* mmc0_dat0.mmc0_dat0 */ AM4372_IOPAD(0x960, PIN_INPUT | MUX_MODE7) /* spi0_cs1.gpio0_6 */ >; }; mmc1_pins_sleep: pinmux_mmc1_pins_sleep { pinctrl-single,pins = < AM4372_IOPAD(0x900, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x904, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x9f0, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x9f4, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x9f8, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x9fc, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x960, PIN_INPUT_PULLDOWN | MUX_MODE7) >; }; spi1_pins_default: spi1_pins_default { pinctrl-single,pins = < AM4372_IOPAD(0x908, PIN_INPUT | MUX_MODE2) /* mii1_col.spi1_sclk */ AM4372_IOPAD(0x910, PIN_INPUT | MUX_MODE2) /* mii1_rx_er.spi1_d1 */ AM4372_IOPAD(0x944, PIN_OUTPUT | MUX_MODE2) /* rmii1_ref_clk.spi1_cs0 */ AM4372_IOPAD(0x90c, PIN_OUTPUT | MUX_MODE7) /* mii1_crs.gpio3_1 */ >; }; spi1_pins_sleep: spi1_pins_sleep { pinctrl-single,pins = < AM4372_IOPAD(0x908, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x910, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x944, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x90c, PIN_INPUT_PULLDOWN | MUX_MODE7) >; }; ecap0_pins_default: backlight_pins_default { pinctrl-single,pins = < AM4372_IOPAD(0x964, PIN_OUTPUT | MUX_MODE0) /* ecap0_in_pwm0_out.ecap0_in_pwm0_out */ >; }; cpsw_default: cpsw_default { pinctrl-single,pins = < AM4372_IOPAD(0x92c, PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txclk.rgmii1_tclk */ AM4372_IOPAD(0x914, PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txen.rgmii1_tctl */ AM4372_IOPAD(0x928, PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txd0.rgmii1_td0 */ AM4372_IOPAD(0x924, PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txd1.rgmii1_td1 */ AM4372_IOPAD(0x920, PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txd0.rgmii1_td2 */ AM4372_IOPAD(0x91c, PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txd1.rgmii1_td3 */ AM4372_IOPAD(0x930, PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxclk.rmii1_rclk */ AM4372_IOPAD(0x918, PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxdv.rgmii1_rctl */ AM4372_IOPAD(0x940, PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxd0.rgmii1_rd0 */ AM4372_IOPAD(0x93c, PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxd1.rgmii1_rd1 */ AM4372_IOPAD(0x938, PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxd0.rgmii1_rd2 */ AM4372_IOPAD(0x934, PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxd1.rgmii1_rd3 */ >; }; cpsw_sleep: cpsw_sleep { pinctrl-single,pins = < AM4372_IOPAD(0x92c, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x914, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x928, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x924, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x920, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x91c, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x930, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x918, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x940, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x93c, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x938, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x934, PIN_INPUT_PULLDOWN | MUX_MODE7) >; }; davinci_mdio_default: davinci_mdio_default { pinctrl-single,pins = < /* MDIO */ AM4372_IOPAD(0x948, PIN_INPUT_PULLUP | SLEWCTRL_FAST | MUX_MODE0) /* mdio_data.mdio_data */ AM4372_IOPAD(0x94c, PIN_OUTPUT_PULLUP | MUX_MODE0) /* mdio_clk.mdio_clk */ >; }; davinci_mdio_sleep: davinci_mdio_sleep { pinctrl-single,pins = < /* MDIO reset value */ AM4372_IOPAD(0x948, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x94c, PIN_INPUT_PULLDOWN | MUX_MODE7) >; }; pruss1_mdio_default: pruss1-mdio-default { pinctrl-single,pins = < AM4372_IOPAD(0x88c, (PIN_OUTPUT | MUX_MODE5)) /* gpmc_clk.pr1_mdio_mdclk */ AM4372_IOPAD(0xa70, (PIN_INPUT | MUX_MODE8)) /* xdma_event_intr0.pr1_mdio_data */ AM4372_IOPAD(0xa00, (PIN_INPUT_PULLUP | MUX_MODE7)) /* cam1_data6.gpio4_20 */ >; }; pruss1_eth_default: pruss1-eth-default { pinctrl-single,pins = < AM4372_IOPAD(0x8a0, (PIN_INPUT | MUX_MODE2)) /* dss_data0.pr1_mii_mt0_clk */ AM4372_IOPAD(0x8b4, (PIN_OUTPUT | MUX_MODE2)) /* dss_data5.pr1_mii0_txd0 */ AM4372_IOPAD(0x8b0, (PIN_OUTPUT | MUX_MODE2)) /* dss_data4.pr1_mii0_txd1 */ AM4372_IOPAD(0x8ac, (PIN_OUTPUT | MUX_MODE2)) /* dss_data3.pr1_mii0_txd2 */ AM4372_IOPAD(0x8a8, (PIN_OUTPUT | MUX_MODE2)) /* dss_data2.pr1_mii0_txd3 */ AM4372_IOPAD(0x8cc, (PIN_INPUT | MUX_MODE5)) /* dss_data11.pr1_mii0_rxd0 */ AM4372_IOPAD(0x8c8, (PIN_INPUT | MUX_MODE5)) /* dss_data10.pr1_mii0_rxd1 */ AM4372_IOPAD(0x8c4, (PIN_INPUT | MUX_MODE5)) /* dss_data9.pr1_mii0_rxd2 */ AM4372_IOPAD(0x8c0, (PIN_INPUT | MUX_MODE5)) /* dss_data8.pr1_mii0_rxd3 */ AM4372_IOPAD(0x8a4, (PIN_OUTPUT | MUX_MODE2)) /* dss_data1.pr1_mii0_txen */ AM4372_IOPAD(0x8d8, (PIN_INPUT | MUX_MODE5)) /* dss_data14.pr1_mii_mr0_clk */ AM4372_IOPAD(0x8dc, (PIN_INPUT | MUX_MODE5)) /* dss_data15.pr1_mii0_rxdv */ AM4372_IOPAD(0x8d4, (PIN_INPUT | MUX_MODE5)) /* dss_data13.pr1_mii0_rxer */ AM4372_IOPAD(0x8d0, (PIN_INPUT | MUX_MODE5)) /* dss_data12.pr1_mii0_rxlink */ AM4372_IOPAD(0xa40, (PIN_INPUT | MUX_MODE5)) /* gpio5_10.pr1_mii0_crs */ AM4372_IOPAD(0xa38, (PIN_INPUT | MUX_MODE5)) /* gpio5_8.pr1_mii0_col */ AM4372_IOPAD(0x858, (PIN_INPUT | MUX_MODE5)) /* gpmc_a6.pr1_mii_mt1_clk */ AM4372_IOPAD(0x854, (PIN_OUTPUT | MUX_MODE5)) /* gpmc_a5.pr1_mii1_txd0 */ AM4372_IOPAD(0x850, (PIN_OUTPUT | MUX_MODE5)) /* gpmc_a4.pr1_mii1_txd1 */ AM4372_IOPAD(0x84c, (PIN_OUTPUT | MUX_MODE5)) /* gpmc_a3.pr1_mii1_txd2 */ AM4372_IOPAD(0x848, (PIN_OUTPUT | MUX_MODE5)) /* gpmc_a2.pr1_mii1_txd3 */ AM4372_IOPAD(0x86c, (PIN_INPUT | MUX_MODE5)) /* gpmc_a11.pr1_mii1_rxd0 */ AM4372_IOPAD(0x868, (PIN_INPUT | MUX_MODE5)) /* gpmc_a10.pr1_mii1_rxd1 */ AM4372_IOPAD(0x864, (PIN_INPUT | MUX_MODE5)) /* gpmc_a9.pr1_mii1_rxd2 */ AM4372_IOPAD(0x860, (PIN_INPUT | MUX_MODE5)) /* gpmc_a8.pr1_mii1_rxd3 */ AM4372_IOPAD(0x840, (PIN_OUTPUT | MUX_MODE5)) /* gpmc_a0.pr1_mii1_txen */ AM4372_IOPAD(0x85c, (PIN_INPUT | MUX_MODE5)) /* gpmc_a7.pr1_mii_mr1_clk */ AM4372_IOPAD(0x844, (PIN_INPUT | MUX_MODE5)) /* gpmc_a1.pr1_mii1_rxdv */ AM4372_IOPAD(0x874, (PIN_INPUT | MUX_MODE5)) /* gpmc_wpn.pr1_mii1_rxer */ AM4372_IOPAD(0xa4c, (PIN_INPUT | MUX_MODE5)) /* gpio5_13.pr1_mii1_rxlink */ AM4372_IOPAD(0xa44, (PIN_INPUT | MUX_MODE5)) /* gpio5_11.pr1_mii1_crs */ AM4372_IOPAD(0x878, (PIN_INPUT | MUX_MODE5)) /* gpmc_be1n.pr1_mii1_col */ >; }; qspi_pins_default: qspi_pins_default { pinctrl-single,pins = < AM4372_IOPAD(0x87c, PIN_OUTPUT_PULLUP | MUX_MODE3) /* gpmc_csn0.qspi_csn */ AM4372_IOPAD(0x888, PIN_OUTPUT | MUX_MODE2) /* gpmc_csn3.qspi_clk */ AM4372_IOPAD(0x890, PIN_INPUT_PULLUP | MUX_MODE3) /* gpmc_advn_ale.qspi_d0 */ AM4372_IOPAD(0x894, PIN_INPUT_PULLUP | MUX_MODE3) /* gpmc_oen_ren.qspi_d1 */ AM4372_IOPAD(0x898, PIN_INPUT_PULLUP | MUX_MODE3) /* gpmc_wen.qspi_d2 */ AM4372_IOPAD(0x89c, PIN_INPUT_PULLUP | MUX_MODE3) /* gpmc_be0n_cle.qspi_d3 */ >; }; qspi_pins_sleep: qspi_pins_sleep{ pinctrl-single,pins = < AM4372_IOPAD(0x87c, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x888, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x890, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x894, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x898, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x89c, PIN_INPUT_PULLDOWN | MUX_MODE7) >; }; }; &i2c0 { status = "okay"; pinctrl-names = "default", "sleep"; pinctrl-0 = <&i2c0_pins_default>; pinctrl-1 = <&i2c0_pins_sleep>; clock-frequency = <400000>; at24@50 { compatible = "atmel,24c256"; pagesize = <64>; reg = <0x50>; }; tps: tps62362@60 { compatible = "ti,tps62362"; reg = <0x60>; regulator-name = "VDD_MPU"; regulator-min-microvolt = <950000>; regulator-max-microvolt = <1330000>; regulator-boot-on; regulator-always-on; ti,vsel0-state-high; ti,vsel1-state-high; vin-supply = <&v3_3d>; }; }; &i2c2 { status = "okay"; pinctrl-names = "default", "sleep"; pinctrl-0 = <&i2c2_pins_default>; pinctrl-1 = <&i2c2_pins_sleep>; clock-frequency = <100000>; tpic2810: tpic2810@60 { compatible = "ti,tpic2810"; reg = <0x60>; gpio-controller; #gpio-cells = <2>; }; }; &spi1 { status = "okay"; pinctrl-names = "default", "sleep"; pinctrl-0 = <&spi1_pins_default>; pinctrl-1 = <&spi1_pins_sleep>; ti,pindir-d0-out-d1-in; sn65hvs882: sn65hvs882@0 { compatible = "pisosr-gpio"; gpio-controller; #gpio-cells = <2>; load-gpios = <&gpio3 1 GPIO_ACTIVE_LOW>; reg = <0>; spi-max-frequency = <1000000>; spi-cpol; }; }; &epwmss0 { status = "okay"; }; &ecap0 { status = "okay"; pinctrl-names = "default"; pinctrl-0 = <&ecap0_pins_default>; }; &gpio0 { status = "okay"; }; &gpio1 { status = "okay"; }; &gpio3 { status = "okay"; }; &gpio4 { status = "okay"; }; &gpio5 { status = "okay"; }; &uart0 { status = "okay"; pinctrl-names = "default", "sleep"; pinctrl-0 = <&uart_0_pins_default>; pinctrl-1 = <&uart_0_pins_sleep>; }; &mmc1 { status = "okay"; pinctrl-names = "default", "sleep"; pinctrl-0 = <&mmc1_pins_default>; pinctrl-1 = <&mmc1_pins_sleep>; vmmc-supply = <&v3_3d>; bus-width = <4>; cd-gpios = <&gpio0 6 GPIO_ACTIVE_LOW>; }; &qspi { status = "okay"; pinctrl-names = "default", "sleep"; pinctrl-0 = <&qspi_pins_default>; pinctrl-1 = <&qspi_pins_sleep>; spi-max-frequency = <48000000>; m25p80@0 { compatible = "mx66l51235l"; spi-max-frequency = <48000000>; reg = <0>; spi-cpol; spi-cpha; spi-tx-bus-width = <1>; spi-rx-bus-width = <4>; #address-cells = <1>; #size-cells = <1>; /* * MTD partition table. The ROM checks the first 512KiB for a * valid file to boot(XIP). */ partition@0 { label = "QSPI.U_BOOT"; reg = <0x00000000 0x000080000>; }; partition@1 { label = "QSPI.U_BOOT.backup"; reg = <0x00080000 0x00080000>; }; partition@2 { label = "QSPI.U-BOOT-SPL_OS"; reg = <0x00100000 0x00010000>; }; partition@3 { label = "QSPI.U_BOOT_ENV"; reg = <0x00110000 0x00010000>; }; partition@4 { label = "QSPI.U-BOOT-ENV.backup"; reg = <0x00120000 0x00010000>; }; partition@5 { label = "QSPI.KERNEL"; reg = <0x00130000 0x0800000>; }; partition@6 { label = "QSPI.FILESYSTEM"; reg = <0x00930000 0x36D0000>; }; }; }; &mac_sw { pinctrl-names = "default", "sleep"; pinctrl-0 = <&cpsw_default>; pinctrl-1 = <&cpsw_sleep>; status = "okay"; }; &davinci_mdio_sw { pinctrl-names = "default", "sleep"; pinctrl-0 = <&davinci_mdio_default>; pinctrl-1 = <&davinci_mdio_sleep>; ethphy0: ethernet-phy@0 { reg = <0>; reset-gpios=<&gpio3 22 GPIO_ACTIVE_LOW>; reset-assert-us=<10000>; reset-deassert-us=<10000>; }; ethphy1: ethernet-phy@1 { reg = <1>; }; }; &cpsw_port1 { phy-handle = <ðphy0>; phy-mode = "mii"; ti,dual-emac-pvid = <1>; }; &cpsw_port2 { phy-handle = <ðphy1>; phy-mode = "mii"; ti,dual-emac-pvid = <2>; }; &rtc { clocks = <&clk_32k_rtc>, <&clk_32768_ck>; clock-names = "ext-clk", "int-clk"; status = "okay"; }; &wdt { status = "okay"; }; &cpu { cpu0-supply = <&tps>; }; &cpu0_opp_table { /* * Supply voltage supervisor on board will not allow opp50 so * disable it and set opp100 as suspend OPP. */ opp50-300000000 { status = "disabled"; }; opp100-600000000 { opp-suspend; }; }; &pruss1_mdio { pinctrl-0 = <&pruss1_mdio_default>; pinctrl-names = "default"; status = "okay"; //reset-gpios = <&gpio4 20 GPIO_ACTIVE_LOW>; //reset-delay-us = <2>; /* PHY datasheet states 1uS min */ pruss1_eth0_phy: ethernet-phy@0 { reg = <0>; }; pruss1_eth1_phy: ethernet-phy@1 { reg = <1>; }; };你好、Rahul

感谢您的回复

请查看随附的截图:以太网无法正常工作、我们正在使用 DTS 文件

尊敬的 Mahesh:

我浏览了日志和 DTS 文件。 DTS 文件看起来正常、您会注意到错误22 (参数无效)、并且无法在 MDIO 总线 PHY 地址0和1上识别 PHY。

如果 PHY 在深入到驱动器侧之前正常工作、我们首先必须在硬件端进行调试、因为在 MDC/MDIO 总线中无法识别 PHY 地址。 如果驱动程序有问题、Linux 应在 PHY 被识别时将通用驱动程序分配给该驱动程序。

您能否尝试在 MII 时钟和 TX/RX 数据线中进行探测、以检查是否发现任何信号? 您还可以检查晶体是否正在向 PHY 提供时钟吗?

您能否同时填写随附的 xls 表格、进行原理图审阅?

谢谢。

拉胡尔

尊敬的 Mahesh:

您能否验证连接到设备树中 PHY 以及 MDC/MDIO 接口的 cpsw MII 端口/引脚?

此部分器件树看起来适用于 PHY 地址0和1:

此致、

拉胡尔

你好、Rahul

已使用定制板进行了验证

cpsw_default:cpsw_default{

PINCCTRL-SINGLE、PINS =<

AM4372_IOPAD (0x92c、PIN_OUTPUT_PULLDDOWN | MUX_MODE2)/* mii1_txclk.rgmii1_tclk */

AM4372_IOPAD (0x914、PIN_OUTPUT_PULLDDOWN | MUX_MODE2)/* mii1_txen.rgmi1_tctl */

AM4372_IOPAD (0x928、PIN_OUTPUT_PULLDDOWN | MUX_MODE2)/* mii1_txd0.rgmi1_td0 */

AM4372_IOPAD (0x924、PIN_OUTPUT_PULLDDOWN | MUX_MODE2)/* mii1_txd1.rgmi1_td1 */

AM4372_IOPAD (0x920、PIN_OUTPUT_PULLDOWN | MUX_MODE2)/* mii1_txd0.rgmi1_td2 */

AM4372_IOPAD (0x91c、PIN_OUTPUT_PULLDOWN | MUX_MODE2)/* mii1_txd1.rgmii1_td3 */

AM4372_IOPAD (0x930、PIN_INPUT_PULLDOW | MUX_MODE2)/* mii1_rxclk.rmii1_RCLK */

AM4372_IOPAD (0x918、PIN_INPUT_PULLDDOWN | MUX_MODE2)/* mii1_rxdv.rgmi1_rctl */

AM4372_IOPAD (0x940、PIN_INPUT_PULLDOW | MUX_MODE2)/* mii1_rxd0.rgmi1_rd0 */

AM4372_IOPAD (0x93c、PIN_INPUT_PULLDOW | MUX_MODE2)/* mii1_rxd1.rgmii1_rd1 */

AM4372_IOPAD (0x938、PIN_INPUT_PULLDOW | MUX_MODE2)/* mii1_rxd0.rgmii1_RD2 */

AM4372_IOPAD (0x934、PIN_INPUT_PULLDDOWN | MUX_MODE2)/* mii1_rxd1.rgmi1_rd3 */

>;

};

cpsw_sleep:cpsw_sleep{

PINCCTRL-SINGLE、PINS =<

AM4372_IOPAD (0x92c、PIN_INPUT_PULLDOWN | MUX_MODE7)

AM4372_IOPAD (0x914、PIN_INPUT_PULLDOWN | MUX_MODE7)

AM4372_IOPAD (0x928、PIN_INPUT_PULLDOW | MUX_MODE7)

AM4372_IOPAD (0x924、PIN_INPUT_PULLDOWN | MUX_MODE7)

AM4372_IOPAD (0x920、PIN_INPUT_PULLDOWN | MUX_MODE7)

AM4372_IOPAD (0x91c、PIN_INPUT_PULLDOWN | MUX_MODE7)

AM4372_IOPAD (0x930、PIN_INPUT_PULLDOWN | MUX_MODE7)

AM4372_IOPAD (0x918、PIN_INPUT_PULLDDOWN | MUX_MODE7)

AM4372_IOPAD (0x940、PIN_INPUT_PULLDOWN | MUX_MODE7)

AM4372_IOPAD (0x93c、PIN_INPUT_PULLDOWN | MUX_MODE7)

AM4372_IOPAD (0x938、PIN_INPUT_PULLDOWN | MUX_MODE7)

AM4372_IOPAD (0x934、PIN_INPUT_PULLUP | MUX_MODE7)

>;

};

它看起来不错

尊敬的 Rahul:

,请参见数据表

我们使用的是 pru-eth0和 pru-eth1 。

有些奇怪的读这

1)是否 需要 dps83822驱动程序,以及 cpsw 和 emac 驱动程序?

2)当前状态是 eth0和 eth1显示在操作系统中,需要对 PRU-ICCS 进行编程?

我附加了 dts 文件和 dmesg 日志

// SPDX-License-Identifier: GPL-2.0-only /* * Copyright (C) 2014 Texas Instruments Incorporated - https://www.ti.com/ */ /dts-v1/; #include "am4372.dtsi" #include <dt-bindings/pinctrl/am43xx.h> #include <dt-bindings/pwm/pwm.h> #include <dt-bindings/gpio/gpio.h> #include <dt-bindings/input/input.h> / { model = "TI AM437x ETH BOARD"; compatible = "ti,am437x-eth","ti,am4372","ti,am43"; chosen { stdout-path = &uart0; }; aliases { ethernet2 = &pruss1_emac0; ethernet3 = &pruss1_emac1; }; v24_0d: fixed-regulator-v24_0d { compatible = "regulator-fixed"; regulator-name = "V24_0D"; regulator-min-microvolt = <24000000>; regulator-max-microvolt = <24000000>; regulator-always-on; regulator-boot-on; }; v3_3d: fixed-regulator-v3_3d { compatible = "regulator-fixed"; regulator-name = "V3_3D"; regulator-min-microvolt = <3300000>; regulator-max-microvolt = <3300000>; regulator-always-on; regulator-boot-on; vin-supply = <&v24_0d>; }; vdd_corereg: fixed-regulator-vdd_corereg { compatible = "regulator-fixed"; regulator-name = "VDD_COREREG"; regulator-min-microvolt = <1100000>; regulator-max-microvolt = <1100000>; regulator-always-on; regulator-boot-on; vin-supply = <&v24_0d>; }; vdd_core: fixed-regulator-vdd_core { compatible = "regulator-fixed"; regulator-name = "VDD_CORE"; regulator-min-microvolt = <1100000>; regulator-max-microvolt = <1100000>; regulator-always-on; regulator-boot-on; vin-supply = <&vdd_corereg>; }; v1_8dreg: fixed-regulator-v1_8dreg{ compatible = "regulator-fixed"; regulator-name = "V1_8DREG"; regulator-min-microvolt = <1800000>; regulator-max-microvolt = <1800000>; regulator-always-on; regulator-boot-on; vin-supply = <&v24_0d>; }; v1_8d: fixed-regulator-v1_8d{ compatible = "regulator-fixed"; regulator-name = "V1_8D"; regulator-min-microvolt = <1800000>; regulator-max-microvolt = <1800000>; regulator-always-on; regulator-boot-on; vin-supply = <&v1_8dreg>; }; v1_5dreg: fixed-regulator-v1_5dreg{ compatible = "regulator-fixed"; regulator-name = "V1_5DREG"; regulator-min-microvolt = <1500000>; regulator-max-microvolt = <1500000>; regulator-always-on; regulator-boot-on; vin-supply = <&v24_0d>; }; v1_5d: fixed-regulator-v1_5d{ compatible = "regulator-fixed"; regulator-name = "V1_5D"; regulator-min-microvolt = <1500000>; regulator-max-microvolt = <1500000>; regulator-always-on; regulator-boot-on; vin-supply = <&v1_5dreg>; }; gpio_keys: gpio_keys { compatible = "gpio-keys"; pinctrl-names = "default"; pinctrl-0 = <&gpio_keys_pins_default>; #address-cells = <1>; #size-cells = <0>; switch0 { label = "power-button"; linux,code = <KEY_POWER>; gpios = <&gpio4 2 GPIO_ACTIVE_LOW>; }; }; /* fixed 32k external oscillator clock */ clk_32k_rtc: clk_32k_rtc { #clock-cells = <0>; compatible = "fixed-clock"; clock-frequency = <32768>; }; leds-iio { status = "disabled"; compatible = "gpio-leds"; led-out0 { label = "out0"; gpios = <&tpic2810 0 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out1 { label = "out1"; gpios = <&tpic2810 1 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out2 { label = "out2"; gpios = <&tpic2810 2 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out3 { label = "out3"; gpios = <&tpic2810 3 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out4 { label = "out4"; gpios = <&tpic2810 4 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out5 { label = "out5"; gpios = <&tpic2810 5 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out6 { label = "out6"; gpios = <&tpic2810 6 GPIO_ACTIVE_HIGH>; default-state = "off"; }; led-out7 { label = "out7"; gpios = <&tpic2810 7 GPIO_ACTIVE_HIGH>; default-state = "off"; }; }; /* Dual-MAC Ethernet application node on PRU-ICSS1 */ pruss1-eth { compatible = "ti,am4376-prueth"; ti,prus = <&pru1_0>, <&pru1_1>; sram = <&ocmcram>; interrupt-parent = <&pruss1_intc>; mii-rt = <&pruss1_mii_rt>; iep = <&pruss1_iep>; pinctrl-0 = <&pruss1_eth_default>; pinctrl-names = "default"; interrupts = <20 2 2>, <21 3 3>; interrupt-names = "rx_lre_hp", "rx_lre_lp"; pruss1_emac0: ethernet-mii0 { phy-handle = <&pruss1_eth0_phy>; phy-mode = "mii"; interrupts = <20 2 2>; interrupt-names = "rx"; ti,no-half-duplex; /* Filled in by bootloader */ local-mac-address = [00 00 00 00 00 00]; }; pruss1_emac1: ethernet-mii1 { phy-handle = <&pruss1_eth1_phy>; phy-mode = "mii"; interrupts = <21 3 3>; interrupt-names = "rx"; ti,no-half-duplex; /* Filled in by bootloader */ local-mac-address = [00 00 00 00 00 00]; }; }; }; &am43xx_pinmux { uart_0_pins_default: uart_0_pins_default { pinctrl-single,pins = < AM4372_IOPAD(0x170, PIN_INPUT | MUX_MODE0) // (K25) uart0_rxd.uart0_rxd AM4372_IOPAD(0x174, PIN_OUTPUT_PULLDOWN | MUX_MODE0) // (J24) uart0_txd.uart0_txd >; }; // Optional sleep pin settings. Must manually enter values in the below skeleton. uart_0_pins_sleep: uart_0_pins_sleep { pinctrl-single,pins = < AM4372_IOPAD(0x170, PIN_INPUT | MUX_MODE0) // (K25) uart0_rxd.uart0_rxd AM4372_IOPAD(0x174, PIN_OUTPUT_PULLDOWN | MUX_MODE0) // (J24) uart0_txd.uart0_txd >; }; gpio_keys_pins_default: gpio_keys_pins_default { pinctrl-single,pins = < AM4372_IOPAD(0x9b8, PIN_INPUT | MUX_MODE7) /* cam0_field.gpio4_2 */ >; }; i2c0_pins_default: i2c0_pins_default { pinctrl-single,pins = < AM4372_IOPAD(0x988, PIN_INPUT | SLEWCTRL_FAST | MUX_MODE0) /* i2c0_sda.i2c0_sda */ AM4372_IOPAD(0x98c, PIN_INPUT | SLEWCTRL_FAST | MUX_MODE0) /* i2c0_scl.i2c0_scl */ >; }; i2c0_pins_sleep: i2c0_pins_sleep { pinctrl-single,pins = < AM4372_IOPAD(0x988, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x98c, PIN_INPUT_PULLDOWN | MUX_MODE7) >; }; i2c2_pins_default: i2c2_pins_default { pinctrl-single,pins = < AM4372_IOPAD(0x9e8, PIN_INPUT | SLEWCTRL_FAST | MUX_MODE3) /* cam1_data1.i2c2_scl */ AM4372_IOPAD(0x9ec, PIN_INPUT | SLEWCTRL_FAST | MUX_MODE3) /* cam1_data0.i2c2_sda */ >; }; i2c2_pins_sleep: i2c2_pins_sleep { pinctrl-single,pins = < AM4372_IOPAD(0x9e8, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x9ec, PIN_INPUT_PULLDOWN | MUX_MODE7) >; }; mmc1_pins_default: pinmux_mmc1_pins_default { pinctrl-single,pins = < AM4372_IOPAD(0x900, PIN_INPUT | MUX_MODE0) /* mmc0_clk.mmc0_clk */ AM4372_IOPAD(0x904, PIN_INPUT | MUX_MODE0) /* mmc0_cmd.mmc0_cmd */ AM4372_IOPAD(0x9f0, PIN_INPUT | MUX_MODE0) /* mmc0_dat3.mmc0_dat3 */ AM4372_IOPAD(0x9f4, PIN_INPUT | MUX_MODE0) /* mmc0_dat2.mmc0_dat2 */ AM4372_IOPAD(0x9f8, PIN_INPUT | MUX_MODE0) /* mmc0_dat1.mmc0_dat1 */ AM4372_IOPAD(0x9fc, PIN_INPUT | MUX_MODE0) /* mmc0_dat0.mmc0_dat0 */ AM4372_IOPAD(0x960, PIN_INPUT | MUX_MODE7) /* spi0_cs1.gpio0_6 */ >; }; mmc1_pins_sleep: pinmux_mmc1_pins_sleep { pinctrl-single,pins = < AM4372_IOPAD(0x900, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x904, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x9f0, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x9f4, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x9f8, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x9fc, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x960, PIN_INPUT_PULLDOWN | MUX_MODE7) >; }; cpsw_default: cpsw_default { pinctrl-single,pins = < AM4372_IOPAD(0x92c, PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txclk.rgmii1_tclk */ AM4372_IOPAD(0x914, PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txen.rgmii1_tctl */ AM4372_IOPAD(0x928, PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txd0.rgmii1_td0 */ AM4372_IOPAD(0x924, PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txd1.rgmii1_td1 */ AM4372_IOPAD(0x920, PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txd0.rgmii1_td2 */ AM4372_IOPAD(0x91c, PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txd1.rgmii1_td3 */ AM4372_IOPAD(0x930, PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxclk.rmii1_rclk */ AM4372_IOPAD(0x918, PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxdv.rgmii1_rctl */ AM4372_IOPAD(0x940, PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxd0.rgmii1_rd0 */ AM4372_IOPAD(0x93c, PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxd1.rgmii1_rd1 */ AM4372_IOPAD(0x938, PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxd0.rgmii1_rd2 */ AM4372_IOPAD(0x934, PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxd1.rgmii1_rd3 */ >; }; cpsw_sleep: cpsw_sleep { pinctrl-single,pins = < AM4372_IOPAD(0x92c, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x914, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x928, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x924, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x920, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x91c, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x930, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x918, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x940, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x93c, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x938, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x934, PIN_INPUT_PULLDOWN | MUX_MODE7) >; }; davinci_mdio_default: davinci_mdio_default { pinctrl-single,pins = < /* MDIO */ AM4372_IOPAD(0x948, PIN_INPUT_PULLUP | SLEWCTRL_FAST | MUX_MODE0) /* mdio_data.mdio_data */ AM4372_IOPAD(0x94c, PIN_OUTPUT_PULLUP | MUX_MODE0) /* mdio_clk.mdio_clk */ >; }; davinci_mdio_sleep: davinci_mdio_sleep { pinctrl-single,pins = < /* MDIO reset value */ AM4372_IOPAD(0x948, PIN_INPUT_PULLDOWN | MUX_MODE7) AM4372_IOPAD(0x94c, PIN_INPUT_PULLDOWN | MUX_MODE7) >; }; nand_flash_x8: nand_flash_x8 { pinctrl-single,pins = < AM4372_IOPAD(0x800, PIN_INPUT | MUX_MODE0) /* gpmc_ad0.gpmc_ad0 */ AM4372_IOPAD(0x804, PIN_INPUT | MUX_MODE0) /* gpmc_ad1.gpmc_ad1 */ AM4372_IOPAD(0x808, PIN_INPUT | MUX_MODE0) /* gpmc_ad2.gpmc_ad2 */ AM4372_IOPAD(0x80c, PIN_INPUT | MUX_MODE0) /* gpmc_ad3.gpmc_ad3 */ AM4372_IOPAD(0x810, PIN_INPUT | MUX_MODE0) /* gpmc_ad4.gpmc_ad4 */ AM4372_IOPAD(0x814, PIN_INPUT | MUX_MODE0) /* gpmc_ad5.gpmc_ad5 */ AM4372_IOPAD(0x818, PIN_INPUT | MUX_MODE0) /* gpmc_ad6.gpmc_ad6 */ AM4372_IOPAD(0x81c, PIN_INPUT | MUX_MODE0) /* gpmc_ad7.gpmc_ad7 */ //AM4372_IOPAD(0x870, PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_wait0.gpmc_wait0 */ //AM4372_IOPAD(0x874, PIN_OUTPUT_PULLUP | MUX_MODE7) /* gpmc_wpn.gpmc_wpn */ AM4372_IOPAD (0x888,PIN_INPUT_PULLUP | MUX_MODE1) /* gpmc_wait0.gpmc_wait0 */ AM4372_IOPAD (0x82c,PIN_OUTPUT_PULLUP | MUX_MODE7) /* gpmc_wpn.gpmc_wpn */ AM4372_IOPAD(0x87c, PIN_OUTPUT | MUX_MODE0) /* gpmc_csn0.gpmc_csn0 */ AM4372_IOPAD(0x890, PIN_OUTPUT | MUX_MODE0) /* gpmc_advn_ale.gpmc_advn_ale */ AM4372_IOPAD(0x894, PIN_OUTPUT | MUX_MODE0) /* gpmc_oen_ren.gpmc_oen_ren */ AM4372_IOPAD(0x898, PIN_OUTPUT | MUX_MODE0) /* gpmc_wen.gpmc_wen */ AM4372_IOPAD(0x89c, PIN_OUTPUT | MUX_MODE0) /* gpmc_be0n_cle.gpmc_be0n_cle */ >; }; pruss1_mdio_default: pruss1-mdio-default { pinctrl-single,pins = < AM4372_IOPAD(0x88c, (PIN_OUTPUT | MUX_MODE5)) /* gpmc_clk.pr1_mdio_mdclk */ AM4372_IOPAD(0xa70, (PIN_INPUT | MUX_MODE8)) /* xdma_event_intr0.pr1_mdio_data */ AM4372_IOPAD(0xa00, (PIN_INPUT_PULLUP | MUX_MODE7)) /* cam1_data6.gpio4_20 */ >; }; pruss1_eth_default: pruss1-eth-default { pinctrl-single,pins = < AM4372_IOPAD(0x8a0, (PIN_INPUT | MUX_MODE2)) /* dss_data0.pr1_mii_mt0_clk */ AM4372_IOPAD(0x8b4, (PIN_OUTPUT | MUX_MODE2)) /* dss_data5.pr1_mii0_txd0 */ AM4372_IOPAD(0x8b0, (PIN_OUTPUT | MUX_MODE2)) /* dss_data4.pr1_mii0_txd1 */ AM4372_IOPAD(0x8ac, (PIN_OUTPUT | MUX_MODE2)) /* dss_data3.pr1_mii0_txd2 */ AM4372_IOPAD(0x8a8, (PIN_OUTPUT | MUX_MODE2)) /* dss_data2.pr1_mii0_txd3 */ AM4372_IOPAD(0x8cc, (PIN_INPUT | MUX_MODE5)) /* dss_data11.pr1_mii0_rxd0 */ AM4372_IOPAD(0x8c8, (PIN_INPUT | MUX_MODE5)) /* dss_data10.pr1_mii0_rxd1 */ AM4372_IOPAD(0x8c4, (PIN_INPUT | MUX_MODE5)) /* dss_data9.pr1_mii0_rxd2 */ AM4372_IOPAD(0x8c0, (PIN_INPUT | MUX_MODE5)) /* dss_data8.pr1_mii0_rxd3 */ AM4372_IOPAD(0x8a4, (PIN_OUTPUT | MUX_MODE2)) /* dss_data1.pr1_mii0_txen */ AM4372_IOPAD(0x8d8, (PIN_INPUT | MUX_MODE5)) /* dss_data14.pr1_mii_mr0_clk */ AM4372_IOPAD(0x8dc, (PIN_INPUT | MUX_MODE5)) /* dss_data15.pr1_mii0_rxdv */ AM4372_IOPAD(0x8d4, (PIN_INPUT | MUX_MODE5)) /* dss_data13.pr1_mii0_rxer */ AM4372_IOPAD(0x8d0, (PIN_INPUT | MUX_MODE5)) /* dss_data12.pr1_mii0_rxlink */ AM4372_IOPAD(0xa40, (PIN_INPUT | MUX_MODE5)) /* gpio5_10.pr1_mii0_crs */ AM4372_IOPAD(0xa38, (PIN_INPUT | MUX_MODE5)) /* gpio5_8.pr1_mii0_col */ AM4372_IOPAD(0x858, (PIN_INPUT | MUX_MODE5)) /* gpmc_a6.pr1_mii_mt1_clk */ AM4372_IOPAD(0x854, (PIN_OUTPUT | MUX_MODE5)) /* gpmc_a5.pr1_mii1_txd0 */ AM4372_IOPAD(0x850, (PIN_OUTPUT | MUX_MODE5)) /* gpmc_a4.pr1_mii1_txd1 */ AM4372_IOPAD(0x84c, (PIN_OUTPUT | MUX_MODE5)) /* gpmc_a3.pr1_mii1_txd2 */ AM4372_IOPAD(0x848, (PIN_OUTPUT | MUX_MODE5)) /* gpmc_a2.pr1_mii1_txd3 */ AM4372_IOPAD(0x86c, (PIN_INPUT | MUX_MODE5)) /* gpmc_a11.pr1_mii1_rxd0 */ AM4372_IOPAD(0x868, (PIN_INPUT | MUX_MODE5)) /* gpmc_a10.pr1_mii1_rxd1 */ AM4372_IOPAD(0x864, (PIN_INPUT | MUX_MODE5)) /* gpmc_a9.pr1_mii1_rxd2 */ AM4372_IOPAD(0x860, (PIN_INPUT | MUX_MODE5)) /* gpmc_a8.pr1_mii1_rxd3 */ AM4372_IOPAD(0x840, (PIN_OUTPUT | MUX_MODE5)) /* gpmc_a0.pr1_mii1_txen */ AM4372_IOPAD(0x85c, (PIN_INPUT | MUX_MODE5)) /* gpmc_a7.pr1_mii_mr1_clk */ AM4372_IOPAD(0x844, (PIN_INPUT | MUX_MODE5)) /* gpmc_a1.pr1_mii1_rxdv */ AM4372_IOPAD(0x874, (PIN_INPUT | MUX_MODE5)) /* gpmc_wpn.pr1_mii1_rxer */ AM4372_IOPAD(0xa4c, (PIN_INPUT | MUX_MODE5)) /* gpio5_13.pr1_mii1_rxlink */ AM4372_IOPAD(0xa44, (PIN_INPUT | MUX_MODE5)) /* gpio5_11.pr1_mii1_crs */ AM4372_IOPAD(0x878, (PIN_INPUT | MUX_MODE5)) /* gpmc_be1n.pr1_mii1_col */ >; }; }; &i2c0 { status = "okay"; pinctrl-names = "default", "sleep"; pinctrl-0 = <&i2c0_pins_default>; pinctrl-1 = <&i2c0_pins_sleep>; clock-frequency = <400000>; at24@50 { compatible = "atmel,24c256"; pagesize = <64>; reg = <0x50>; }; tps: tps62362@60 { compatible = "ti,tps62362"; reg = <0x60>; regulator-name = "VDD_MPU"; regulator-min-microvolt = <950000>; regulator-max-microvolt = <1330000>; regulator-boot-on; regulator-always-on; ti,vsel0-state-high; ti,vsel1-state-high; vin-supply = <&v3_3d>; }; }; &i2c2 { status = "okay"; pinctrl-names = "default", "sleep"; pinctrl-0 = <&i2c2_pins_default>; pinctrl-1 = <&i2c2_pins_sleep>; clock-frequency = <100000>; tpic2810: tpic2810@60 { compatible = "ti,tpic2810"; reg = <0x60>; gpio-controller; #gpio-cells = <2>; }; }; &gpmc { /* * When enabling GPMC, disable eMMC and set * SelEMMCorNAND to output-low */ status = "okay"; pinctrl-names = "default"; pinctrl-0 = <&nand_flash_x8>; ranges = <0 0 0x08000000 0x01000000>; /* CS0 space. Min partition = 16MB */ nand@0,0 { compatible = "ti,omap2-nand"; reg = <0 0 4>; /* device IO registers */ interrupt-parent = <&gpmc>; interrupts = <0 IRQ_TYPE_NONE>, /* fifoevent */ <1 IRQ_TYPE_NONE>; /* termcount */ rb-gpios = <&gpmc 0 GPIO_ACTIVE_HIGH>; /* gpmc_wait0 */ ti,nand-xfer-type = "prefetch-dma"; ti,nand-ecc-opt = "bch16"; nand-bus-width = <8>; gpmc,device-width = <1>; gpmc,sync-clk-ps = <0>; gpmc,cs-on-ns = <0>; gpmc,cs-rd-off-ns = <40>; gpmc,cs-wr-off-ns = <40>; gpmc,adv-on-ns = <0>; gpmc,adv-rd-off-ns = <25>; gpmc,adv-wr-off-ns = <25>; gpmc,we-on-ns = <0>; gpmc,we-off-ns = <20>; gpmc,oe-on-ns = <3>; gpmc,oe-off-ns = <30>; gpmc,access-ns = <30>; gpmc,rd-cycle-ns = <40>; gpmc,wr-cycle-ns = <40>; gpmc,bus-turnaround-ns = <0>; gpmc,cycle2cycle-delay-ns = <0>; gpmc,clk-activation-ns = <0>; gpmc,wr-access-ns = <40>; gpmc,wr-data-mux-bus-ns = <0>; /* MTD partition table */ /* All SPL-* partitions are sized to minimal length * which can be independently programmable. For * NAND flash this is equal to size of erase-block */ #address-cells = <1>; #size-cells = <1>; partition@0 { label = "NAND.SPL"; reg = <0x00000000 0x00040000>; }; partition@1 { label = "NAND.SPL.backup1"; reg = <0x00040000 0x00040000>; }; partition@2 { label = "NAND.SPL.backup2"; reg = <0x00080000 0x00040000>; }; partition@3 { label = "NAND.SPL.backup3"; reg = <0x000c0000 0x00040000>; }; partition@4 { label = "NAND.u-boot-spl-os"; reg = <0x00100000 0x00080000>; }; partition@5 { label = "NAND.u-boot"; reg = <0x00180000 0x00100000>; }; partition@6 { label = "NAND.u-boot-env"; reg = <0x00280000 0x00040000>; }; partition@7 { label = "NAND.u-boot-env.backup1"; reg = <0x002c0000 0x00040000>; }; partition@8 { label = "NAND.kernel"; reg = <0x00300000 0x00700000>; }; partition@9 { label = "NAND.file-system"; reg = <0x00a00000 0x1f600000>; }; }; }; &gpio0 { status = "okay"; }; &gpio1 { status = "okay"; }; &gpio3 { status = "okay"; }; &gpio4 { status = "okay"; }; &gpio5 { status = "okay"; }; &uart0 { status = "okay"; pinctrl-names = "default", "sleep"; pinctrl-0 = <&uart_0_pins_default>; pinctrl-1 = <&uart_0_pins_sleep>; }; &mmc1 { status = "okay"; pinctrl-names = "default", "sleep"; pinctrl-0 = <&mmc1_pins_default>; pinctrl-1 = <&mmc1_pins_sleep>; vmmc-supply = <&v3_3d>; bus-width = <4>; cd-gpios = <&gpio0 6 GPIO_ACTIVE_LOW>; }; &rtc { clocks = <&clk_32k_rtc>, <&clk_32768_ck>; clock-names = "ext-clk", "int-clk"; status = "okay"; }; &wdt { status = "okay"; }; &cpu { cpu0-supply = <&tps>; }; &cpu0_opp_table { /* * Supply voltage supervisor on board will not allow opp50 so * disable it and set opp100 as suspend OPP. */ opp50-300000000 { status = "disabled"; }; opp100-600000000 { opp-suspend; }; }; &mac_sw { pinctrl-names = "default", "sleep"; pinctrl-0 = <&cpsw_default>; pinctrl-1 = <&cpsw_sleep>; status = "okay"; }; &davinci_mdio_sw { pinctrl-names = "default", "sleep"; pinctrl-0 = <&davinci_mdio_default>; pinctrl-1 = <&davinci_mdio_sleep>; ethphy0: ethernet-phy@0 { status = "ok"; reg = <0>; compatible = "ti,dp83222", "ethernet-phy-ieee802.3-c22"; ti,rx-internal-delay = <0x8>; ti,tx-internal-delay = <0xa>; ti,fifo-depth = <0x01>; }; ethphy1: ethernet-phy@1 { status = "ok"; reg = <1>; compatible = "ti,dp83222", "ethernet-phy-ieee802.3-c22"; ti,rx-internal-delay = <0x8>; ti,tx-internal-delay = <0xa>; ti,fifo-depth = <0x01>; }; }; &cpsw_port1 { phy-handle = <ðphy0>; phy-mode = "mii"; ti,dual-emac-pvid = <1>; }; &cpsw_port2 { phy-handle = <ðphy1>; phy-mode = "mii"; ti,dual-emac-pvid = <1>; }; &pruss1_mdio { pinctrl-0 = <&pruss1_mdio_default>; pinctrl-names = "default"; status = "okay"; reset-gpios = <&gpio4 20 GPIO_ACTIVE_LOW>; reset-delay-us = <2>; /* PHY datasheet states 1uS min */ pruss1_eth0_phy: ethernet-phy@0 { reg = <0>; }; pruss1_eth1_phy: ethernet-phy@1 { reg = <1>; }; };对于此次更新、请告知我任何进一步的信息

oot@am437x-evm:~# dmesg | grep phy

root@am437x-evm:~# dmesg | grep cpsw

[ 4.411215] cpsw-switch 4a100000.switch: initialized cpsw ale version 1.4

[ 4.418119] cpsw-switch 4a100000.switch: ALE Table size 1024

[ 4.423967] cpsw-switch 4a100000.switch: cpts: overflow check period 500 (jiffies)

[ 4.431641] cpsw-switch 4a100000.switch: CPTS: ref_clk_freq:250000000 calc_mult:2147483648 calc_shift:29 error:0 nsec/sec

[ 4.442791] cpsw-switch 4a100000.switch: Detected MACID = 88:01:f9:35:d5:a0

[ 4.449885] cpsw-switch 4a100000.switch: Detected MACID = 88:01:f9:35:d5:a2

[ 4.460238] cpsw-switch 4a100000.switch: initialized (regs 0x4a100000, pool size 256) hw_ver:0019010F 1.15 (0)

[ 46.310592] cpsw-switch 4a100000.switch: starting ndev. mode: dual_mac

[ 46.416432] cpsw-switch 4a100000.switch: phy "/ocp@44000000/interconnect@4a000000/segment@0/target-module@100000/switch@0/mdio@1000/ethern1

[ 46.753422] cpsw-switch 4a100000.switch: starting ndev. mode: dual_mac

[ 46.820256] cpsw-switch 4a100000.switch: phy "/ocp@44000000/interconnect@4a000000/segment@0/target-module@100000/switch@0/mdio@1000/ethern0

root@am437x-evm:~# dmesg | grep mdio

[ 4.324925] mdio_bus fixed-0: GPIO lookup for consumer reset

[ 4.324953] mdio_bus fixed-0: using lookup tables for GPIO lookup

[ 4.324972] mdio_bus fixed-0: No GPIO consumer reset found

[ 4.337334] mdio_bus 4a101000.mdio: GPIO lookup for consumer reset

[ 4.337363] mdio_bus 4a101000.mdio: using device tree for GPIO lookup

[ 4.337466] of_get_named_gpiod_flags: can't parse 'reset-gpios' property of node '/ocp@44000000/interconnect@4a000000/segment@0/target-mod'

[ 4.337537] of_get_named_gpiod_flags: can't parse 'reset-gpio' property of node '/ocp@44000000/interconnect@4a000000/segment@0/target-modu'

[ 4.337565] mdio_bus 4a101000.mdio: using lookup tables for GPIO lookup

[ 4.337585] mdio_bus 4a101000.mdio: No GPIO consumer reset found

[ 4.387956] davinci_mdio 4a101000.mdio: davinci mdio revision 1.6, bus freq 1000000

[ 4.395984] mdio_bus 4a101000.mdio: MDIO device at address 0 is missing.

[ 4.403043] mdio_bus 4a101000.mdio: MDIO device at address 1 is missing.

[ 24.411511] mdio_bus 54432400.mdio: GPIO lookup for consumer reset

[ 24.411545] mdio_bus 54432400.mdio: using device tree for GPIO lookup

[ 24.411647] of_get_named_gpiod_flags: parsed 'reset-gpios' property of node '/ocp@44000000/target-module@54400000/pruss@0/mdio@32400[0]' -)

[ 24.468104] davinci_mdio 54432400.mdio: davinci mdio revision 1.6, bus freq 1000000

[ 24.568387] mdio_bus 54432400.mdio: MDIO device at address 0 is missing.

[ 24.675653] mdio_bus 54432400.mdio:01: GPIO lookup for consumer reset

[ 24.675683] mdio_bus 54432400.mdio:01: using device tree for GPIO lookup

[ 24.675776] of_get_named_gpiod_flags: can't parse 'reset-gpios' property of node '/ocp@44000000/target-module@54400000/pruss@0/mdio@32400/'

[ 24.675840] of_get_named_gpiod_flags: can't parse 'reset-gpio' property of node '/ocp@44000000/target-module@54400000/pruss@0/mdio@32400/e'

[ 24.675866] mdio_bus 54432400.mdio:01: using lookup tables for GPIO lookup

[ 24.675887] mdio_bus 54432400.mdio:01: No GPIO consumer reset found

[ 24.676462] davinci_mdio 54432400.mdio: phy[1]: device 54432400.mdio:01, driver unknown

[ 46.416432] cpsw-switch 4a100000.switch: phy "/ocp@44000000/interconnect@4a000000/segment@0/target-module@100000/switch@0/mdio@1000/ethern1

[ 46.820256] cpsw-switch 4a100000.switch: phy "/ocp@44000000/interconnect@4a000000/segment@0/target-module@100000/switch@0/mdio@1000/ethern0

root@am437x-evm:~# dmesg | grep

BusyBox v1.31.1 (2022-06-02 20:26:25 UTC) multi-call binary.

Usage: grep [-HhnlLoqvsriwFE] [-m N] [-A/B/C N] PATTERN/-e PATTERN.../-f FILE [FILE]...

root@am437x-evm:~# dmesg | grep phy

[ 0.000000] Booting Linux on physical CPU 0x0

[ 8.598354] no physical memory specified

[ 24.675776] of_get_named_gpiod_flags: can't parse 'reset-gpios' property of node '/ocp@44000000/target-module@54400000/pruss@0/mdio@32400/'

[ 24.675840] of_get_named_gpiod_flags: can't parse 'reset-gpio' property of node '/ocp@44000000/target-module@54400000/pruss@0/mdio@32400/e'

[ 24.676462] davinci_mdio 54432400.mdio: phy[1]: device 54432400.mdio:01, driver unknown

[ 46.416432] cpsw-switch 4a100000.switch: phy "/ocp@44000000/interconnect@4a000000/segment@0/target-module@100000/switch@0/mdio@1000/ethern1

[ 46.820256] cpsw-switch 4a100000.switch: phy "/ocp@44000000/interconnect@4a000000/segment@0/target-module@100000/switch@0/mdio@1000/ethern0

root@am437x-evm:~# ifconfig -a

eth0: flags=4163<UP,BROADCAST,RUNNING,MULTICAST> mtu 1500 metric 1

inet 192.168.58.4 netmask 255.255.255.0 broadcast 192.168.58.255

inet6 fe80::8a01:f9ff:fe35:d5a0 prefixlen 64 scopeid 0x20<link>

ether 88:01:f9:35:d5:a0 txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 49 bytes 7586 (7.4 KiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

eth1: flags=4163<UP,BROADCAST,RUNNING,MULTICAST> mtu 1500 metric 1

inet 192.168.58.6 netmask 255.255.255.0 broadcast 192.168.58.255

inet6 fe80::8a01:f9ff:fe35:d5a2 prefixlen 64 scopeid 0x20<link>

ether 88:01:f9:35:d5:a2 txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 54 bytes 8847 (8.6 KiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

lo: flags=73<UP,LOOPBACK,RUNNING> mtu 65536 metric 1

inet 127.0.0.1 netmask 255.0.0.0

inet6 ::1 prefixlen 128 scopeid 0x10<host>

loop txqueuelen 1000 (Local Loopback)

RX packets 173 bytes 13420 (13.1 KiB)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 173 bytes 13420 (13.1 KiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

sit0: flags=128<NOARP> mtu 1480 metric 1

unspec 00-00-00-00-66-65-33-35-00-00-00-00-00-00-00-00 txqueuelen 1000 (UNSPEC)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

root@am437x-evm:~#

CTRL-A Z for help | 115200 8N1 | NOR | Minicom 2.8 | VT102 | Offline | ttyUSB0

大家好

我测试了 AM437x-idk-evm 分支电路板,其中3个以太网1用于 cpsw 以太网,2个用于 PRU-ICSS。 当我在这个板上测试它时、所有端口都可以正常工作。以太网也是 ping。

我用与 PRU 相同的配置修改了定制板 AM437X-ETH.DTS 、但不同的是我们没有使用 CPSW 端口。我们使用的是 DPS83822 phy。

以下是我们的问题

10 DPS83822驱动程序未进行检测

2)由于 AM437x-eth.dts (定制板级配置文件)中有问题、因此无法显示 eth0、eth1。

有关已修改 DTS 文件的帮助是正确的、请找到两个 DTS 文件并进行比较。Differences 我已在 DTS 中删除 Davinci_mDIO 和 cpsw

e2e.ti.com/.../am437x_2D00_eth.txte2e.ti.com/.../5023.am437x_2D00_idk_2D00_evm.txt

请说明我们在 DTS 文件中完成了正确的配置