默认情况下、第二个 PCIe 插槽未配置为 SoC 端的 PCIe 根复合体模式、这意味着如果我们要连接 NVMe SSD 卡等端点设备、则链路不会建立。

将 NVMe SSD 卡连接到第二个 PCIe 插槽 J17 (连接到 PCIe 的2个通道)时、引导日志报告"Failed to init phy"(无法初始化物理层)。 PCIe 的链路仅在 J14中的第一个 PCIe 插槽上初始化、该插槽连接到 PCIe 的4个通道。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

默认情况下、第二个 PCIe 插槽未配置为 SoC 端的 PCIe 根复合体模式、这意味着如果我们要连接 NVMe SSD 卡等端点设备、则链路不会建立。

将 NVMe SSD 卡连接到第二个 PCIe 插槽 J17 (连接到 PCIe 的2个通道)时、引导日志报告"Failed to init phy"(无法初始化物理层)。 PCIe 的链路仅在 J14中的第一个 PCIe 插槽上初始化、该插槽连接到 PCIe 的4个通道。

这是 [FAQ] TDA4VM:TDA4VM/DRA829V 的扩展: 将 PCIe 参考时钟从外部布线、其中包含需要从外部布线 PCIe 参考时钟的图片和示例。

使用 J784S4的8.6 SDK 版本时、无需对器件树进行软件更改、即可启用适用于 PCIe RC 模式的第二个 PCIe 插槽、也无需在该模式下将 SSD 卡连接到 PCIe 插槽以用作第二个存储设备。

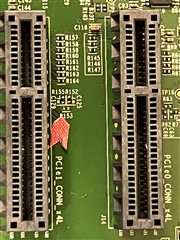

但是、只需要修改硬件、才能使两个 PCIe 插槽以相同的方式工作。 如下面的原理图所示、对于第二个 PCIe 插槽、R155和 R152为"DNI"或"不安装"、因此默认情况下 CLKGEN_PCIE1_2L_REFCLK_P、N (外部时钟)未连接到 CON_PCIE1_2L_REFCLK_P 和 N (PCIe 连接器)。

请参阅以下图像、了解进行更改后电阻器在电路板上的物理外观:

这些硬件更改导致两个 PCIe 卡、如 NVMe SSD 卡、可用作存储。 附件是两个同时进行读/写操作的 SSD 卡的视频、这些 SSD 卡连接到顶部的两个 PCIe 插槽 J14和 J17。

e2e.ti.com/.../IMG_5F00_1084.zip

可参考 每个 J7x 平台的原理图文件 www.ti.com/.../sprr458获取类似信息、以供参考。 这些资源通常可以在 EVM 的产品页面上找到 https://www.ti.com/tool/J784S4XEVM。

可以在用户指南中找到其他参考、其中引用了需要外部时钟的第二个 PCIe 插槽以及需要修改电路板的原因:

注意:请确保 SSD 卡是 NVMe SSD 卡、并且已格式化 和 为 ext4fs (Linux 文件系统)分区。