主题中讨论的其他器件:TDA4VM、 TDA4VH

您好、TI PCIe 专家、

我的行业客户正在使用 TDA4VH SDK8.6、并且需要 SDK 中的 RT 补丁用于行业实时应用。 客户正在 RC 模式下使用我们的处理器 TDA4VM/VH PCIe、并 在 EP 模式下连接到第三方 PCIe NIC (Realtek_RTL8111H)。 有2个与 PCIe 相关的问题阻止了他们的进度。 经过一些测试和搜索、也有一些其他的客户在 TDA4VH 中遇到了同样的问题。

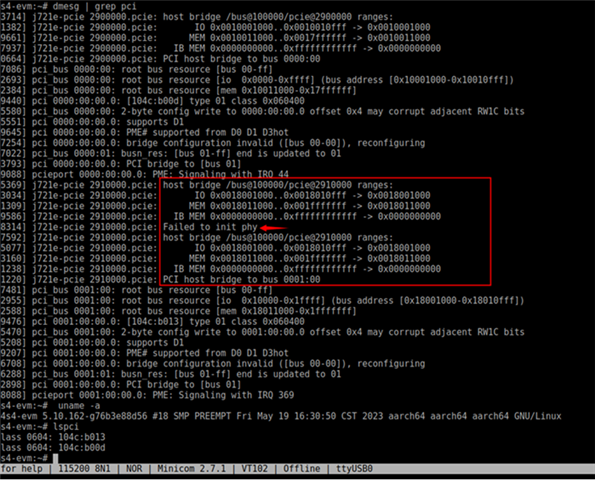

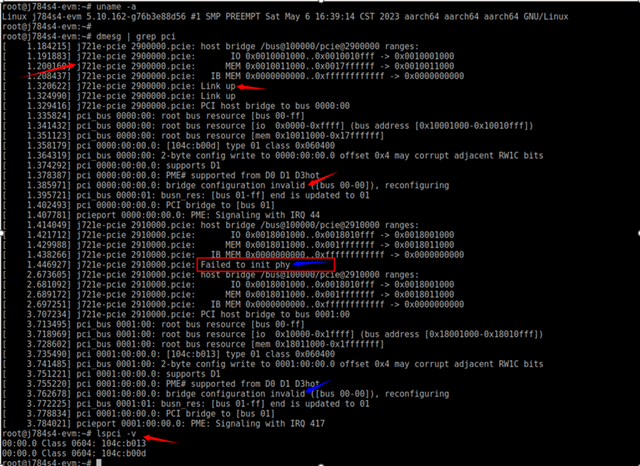

对于问题1 (没有 RT 补丁)、PCIE0的根复合体可以运行、但 PCIE1 (RC1)将具有 phy init 错误、并且无法以相同的设置建立链路。 TDA4VM 中不存在此问题。

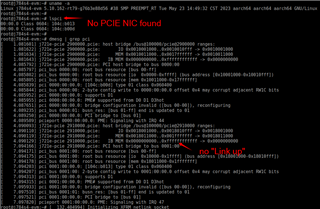

对于问题2 (使用 RT 补丁)、在相同的软件和硬件环境下、仅添加 RT 补丁、 在 TDA4VM 和 TDA4VH 中、PCIE0和 PCIE1都将出现内核崩溃问题。

感谢您对上述2个问题的帮助!

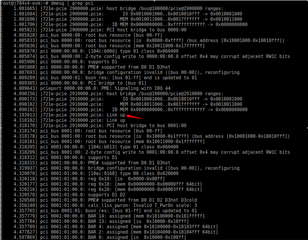

以下是问题2的错误日志。

[ 1.026490] j721e-PCIe 2900000.PCIe:主机桥/bus@100000/PCIe@2900000范围:

[ 1.026511] j721e-PCIe 2900000。PCIe: IO 0x0010001000……0x0010010fff -> 0x001000

[ 1.026522] j721e-PCIe 2900000.PCIe: MEM 0x0010011000..0x0017ffff -> 0x0010011000

[ 1.026532] j721e-PCIe 2900000.PCIe: IB MEM 0x0000000000..0xFFffffff -> 0x0000000000

[ 1.137304] j721e-pcie 29000.pcie:链路接通

[ 1.137309] j721e-pcie 29000.pcie:链路接通

[1.137375] j721e-pcie 2900000.pcie:PCI 主机桥接至总线0000:00

[ 1.137379] PCI_BUS 0000:00:根总线资源[总线00-ff]

[ 1.137384] PCI_BUS 0000:根总线资源[IO 0x0000-0FFF](总线地址[0x10001000-0x10010fff])

[ 1.137388] PCI_BUS 0000:00:根总线资源[mem 0x10011000-0x17ffff]

[ 1.137418] PCI 0000:00:00.0:[104C:b00d]类型01类0x060400

[ 1.137423] PCI_BUS 0000:00:2字节 CONFIG 写入0000:00:00.0偏移量0x4可能会损坏相邻的 RW1C 位

[ 1.137509] PCI 0000:00:00.0:支持 D1

[1.137512] PCI 0000:00:00.0:D0 D1 D3hot 支持 PME#

[ 1.137530] PCI 0000:00:00.0:寄存器0x224:[MEM 0x00000000-0x003fff 64位]

[ 1.137534] PCI 0000:00:00.0:VF (n) BAR0空间:[MEM 0x00000000-0x00ffff 64位](包含4个 VF 的 BAR0)

[ 1.139524] PCI 0000:00:00.0:桥配置无效([bus 00-00]),重新配置

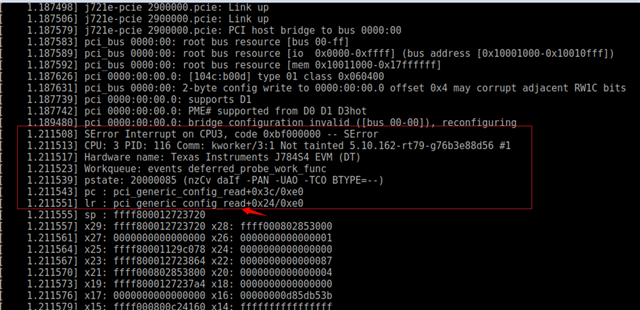

[ 1.161305] CPU1上的 SError 中断、代码0xbf000000 -- SError

[1.161311] CPU:1 PID:66 Comm:kworker/1:2 not dament 5.10.162-rt79-g02a1d48fd7 #3

[ 1.161314]硬件名称:德州仪器(TI) K3 J721E SoC (DT)

[ 1.161320 ] j721e-pcie 29000.pcie:link down!

[1.161321] workqueue:事件 defended_probe_work_func

[1.161334] pstate:20000085 (nzCv daIf -pan -uao -TCO BTYPE=-)

[1.161338] PC : PCI_GENERAL_CONFIG_READ+0x3c/0xe0

[1.161346] lr : PCI_GENERAL_CONFIG_READ+0x24/0xe0

[1.161349] sp : ff800011883720

[1.161350] x29:ff800011883720 x28:ff000801be6800

[ 1.161354] x27:000000000000 x26:0000000000000001

[1.161357] x25:ff800011256bf8 x24:000000000000

[ 1.161360] x23:ff800011883864 x22:0000000000000087

[1.161363] x21:ff000801be7000 x20:000000000004

[1.161366] x19:ff8000118837a4 x18:000000000000

[ 1.161368] x17:00000000f6ae94a3 x16:00000000e360973d

[1.161372] x15:ff000800d9b260 x14:ffffffffffffffffffffffffffffffffffffffff

[1.161374] x13:ff000801ab9a1c x12:ff000801ab929a

[1.161377] x11:01010101010101 x10:7f7f7f7f7f7f7f7f7f7f7f7f7f

[1.16 1380] x9:00000000b00d104c x8:0000000080b5111d

[1.161383] x7 : 000000000000ea60 x6 : ff800011883864

[ 1.161386] x5:ff000801be6800 x4:00000000000b

[ 1.161388] x3 : 0000000000000001 x2 : ff800013c00008

[ 1.161391] x1 : 0000000000000000 x0 : ff8000116b5000

[ 1.161394]内核紧急-未同步:

[1.161395] 异步错误中断

[1.161397] CPU: 1 PID: 66 Comm: kwork/1:2 not dament 5.10.162-rt79-g02a1d48fd7 #3

[ 1.161400]硬件名称:德州仪器(TI) K3 J721E SoC (DT)

[ 1.161406] workqueue:事件 defended_probe_work_func

[1.161410] 呼叫跟踪:

[ 1.161411] dump_backtrace+0x0/0x1a0

[ 1.161420] show_stack+0x18/0x68

[ 1.161424] dump_stack+0xd0/0x12c

[1.161430] 恐慌+0xcc/0x360

[ 1.161434] NMI_PANE+0x94/0x98

[ 1.161439] arm64_serror_pania+0x78/0x84

[ 1.161442] do_serror+0x38/0x98

[ 1.161447] el1_error+0x90/0x110

[ 1.16 1449] pci_generic_config_read+0x3c/0xe0

[ 1.161453] cdns_ti_pci_config_read+0x18/0x38

[ 1.161459] PCI_BUS_READ_CONFIG_DWORD+0x80/0xd8

[ 1.161462] PCI_BUS_GENERAL_READ_DEV_VENTER_id+0x34/0x1b0

[ 1.161465] PCI_BUS_READ_DEV_VENTOR_id+0x4c/0x70

[ 1.161468] PCI_SCAN_SINGLE_DEVICE+0x7c/0xf8

[ 1.161470] PCI_SCAN_SLOT+0x40/0x120

[ 1.161472] PCI_SCAN_CHILD_BUS_EXTEND+0x54/0x298

[ 1.161475] PCI_SCAN_BRIDGE_EXTEND+0x29c/0x580

[ 1.161477] PCI_SCAN_CHILD_BUS_EXTEND+0x1e4/0x298

[ 1.161480] PCI_SCAN_ROOT_BUS_BRIDGE+0x64/0xd8

[ 1.161482] PCI_HOST_PROBE+0x18/0xc8

[ 1.161485] cdns_pci_host_setup+0x51c/0x8f8

[ 1.161489] j721e_pci_prob+0x494/0x820

[ 1.161492] platform_drv_probed+0x54/0xa8

[ 1.161498] reallet_prob+0xec/0x3e0

[ 1.16 1501] driver_probe_device+0x58/0xb8

[ 1.161504] _device_attach_driver+0xb8/0xe0

[ 1.16 1507] bus_for_each_drv+0x78/0xc8

[ 1.161510] __DEVICE_ATIAT+0xf8/0x188

[ 1.161513] DEVICE_INITIAL_PROBE+0x14/0x20

[ 1.161516] BUS_PROBE_DEVICE+0x9C/0xa8

[ 1.161519] Defered_probe_work_func+0x88/0xc0

[ 1.161522] proce_one_work+0x1a0/0x328

[1.161527] worker_thread+0x1f8/0x420

[1.161531] kthread+0x174/0x198

[ 1.161534] ret_from_fork+0x10/0x34

此致、

凯文