您好!

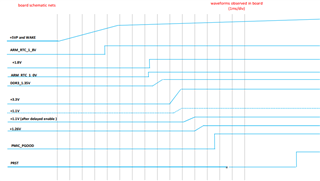

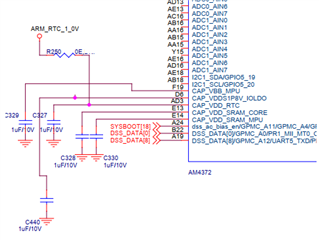

我们 基于 AM4372的 PCB、其设计遵循秒中所述的正常上电顺序。 5.12.1.2进行说明。

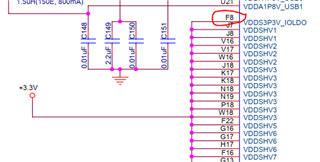

在电路板中、引脚#F8 (VDDS3P3V_IOLDO)连接至3.3V 电源、但引脚#D6 (CAP_VDDS1P8V_IOLDO)未连接至 VDDS 或 VDDS_CLOCKOUT 或电路板中的任何其他负载。

VDDS、VDDS_CLOCKOUT 由单独的1.8V 电源供电

我们使用 LTC366-1作为 PMIC。

是否可以将 VDDS3P3V_IOLDO 连接到3.3V、但 在正常上电序列中从单独的电源为 VDDS 和 VDDS_CLOCKOUT 供电?

此致、

约瑟夫·托马斯