尊敬的 TI 支持团队:

我是新的软件开发人员、目前正在从事使用定制电路板上的 DP83TG720 PHY 的项目。

我已经按照 这里的常见问题解答进行了介绍、但我不使用叠加器件树、而是尝试将内容合并到 k3-j721e-common-proc-board.dts 中、我认为它更容易、并且可以使用我的定制电路板进行调整。

这是我更新的 k3-j721e-common-proc-board.dts。

// SPDX-License-Identifier: GPL-2.0 /* * Copyright (C) 2019 Texas Instruments Incorporated - https://www.ti.com/ */ /dts-v1/; #include "k3-j721e-som-p0.dtsi" #include <dt-bindings/gpio/gpio.h> #include <dt-bindings/input/input.h> #include <dt-bindings/net/ti-dp83867.h> #include <dt-bindings/phy/phy-cadence.h> / { chosen { stdout-path = "serial2:115200n8"; bootargs = "console=ttyS2,115200n8 earlycon=ns16550a,mmio32,0x02800000"; }; evm_12v0: fixedregulator-evm12v0 { /* main supply */ compatible = "regulator-fixed"; regulator-name = "evm_12v0"; regulator-min-microvolt = <12000000>; regulator-max-microvolt = <12000000>; regulator-always-on; regulator-boot-on; }; vsys_3v3: fixedregulator-vsys3v3 { /* Output of LMS140 */ compatible = "regulator-fixed"; regulator-name = "vsys_3v3"; regulator-min-microvolt = <3300000>; regulator-max-microvolt = <3300000>; vin-supply = <&evm_12v0>; regulator-always-on; regulator-boot-on; }; vsys_5v0: fixedregulator-vsys5v0 { /* Output of LM5140 */ compatible = "regulator-fixed"; regulator-name = "vsys_5v0"; regulator-min-microvolt = <5000000>; regulator-max-microvolt = <5000000>; vin-supply = <&evm_12v0>; regulator-always-on; regulator-boot-on; }; vdd_mmc1: fixedregulator-sd { compatible = "regulator-fixed"; regulator-name = "vdd_mmc1"; regulator-min-microvolt = <3300000>; regulator-max-microvolt = <3300000>; regulator-boot-on; enable-active-high; vin-supply = <&vsys_3v3>; gpio = <&exp2 2 GPIO_ACTIVE_HIGH>; }; transceiver1: can-phy0 { compatible = "nxp,tja1462"; #phy-cells = <0>; max-bitrate = <5000000>; pinctrl-names = "default"; pinctrl-0 = <&mygpio0_pins_default>;// Sub_Can_STB standby-gpios = <&main_gpio0 6 GPIO_ACTIVE_HIGH>; }; transceiver2: can-phy1 { compatible = "nxp,tja1462"; #phy-cells = <0>; max-bitrate = <5000000>; pinctrl-names = "default"; pinctrl-0 = <&main_i2c1_exp4_pins_default>; standby-gpios = <&main_gpio1 11 GPIO_ACTIVE_HIGH>; // -U2 - SenSor_Can_STB }; }; &main_pmx0 { mygpio0_pins_default: mygpio0_pins_default { pinctrl-single,pins = < J721E_IOPAD(0x18, PIN_OUTPUT, 7) /* (AD20) PRG1_PRU0_GPO5.GPIO0_6 0011 C018h*/ >; }; main_mmc1_pins_default: main-mmc1-pins-default { pinctrl-single,pins = < J721E_IOPAD(0x254, PIN_INPUT, 0) /* (R29) MMC1_CMD */ J721E_IOPAD(0x250, PIN_INPUT, 0) /* (P25) MMC1_CLK */ J721E_IOPAD(0x2ac, PIN_INPUT, 0) /* (P25) MMC1_CLKLB */ J721E_IOPAD(0x24c, PIN_INPUT, 0) /* (R24) MMC1_DAT0 */ J721E_IOPAD(0x248, PIN_INPUT, 0) /* (P24) MMC1_DAT1 */ J721E_IOPAD(0x244, PIN_INPUT, 0) /* (R25) MMC1_DAT2 */ J721E_IOPAD(0x240, PIN_INPUT, 0) /* (R26) MMC1_DAT3 */ J721E_IOPAD(0x258, PIN_INPUT, 0) /* (P23) MMC1_SDCD */ J721E_IOPAD(0x25c, PIN_INPUT, 0) /* (R28) MMC1_SDWP */ >; }; main_i2c1_exp4_pins_default: main-i2c1-exp4-pins-default { pinctrl-single,pins = < J721E_IOPAD(0x230, PIN_OUTPUT, 7) /* (U2) ECAP0_IN_APWM_OUT.GPIO1_11 0x0011c230*/ >; }; main_i2c0_pins_default: main-i2c0-pins-default { pinctrl-single,pins = < J721E_IOPAD(0x220, PIN_INPUT_PULLUP, 0) /* (AC5) I2C0_SCL */ J721E_IOPAD(0x224, PIN_INPUT_PULLUP, 0) /* (AA5) I2C0_SDA */ >; }; main_i2c1_pins_default: main-i2c1-pins-default { pinctrl-single,pins = < J721E_IOPAD(0x228, PIN_INPUT_PULLUP, 0) /* (Y6) I2C1_SCL */ J721E_IOPAD(0x22c, PIN_INPUT_PULLUP, 0) /* (AA6) I2C1_SDA */ >; }; main_spi1_pins_default: main_spi1_pins_default { pinctrl-single,pins = < J721E_IOPAD(0x1dc, PIN_INPUT, 0) /* (Y1) SPI1_CLK */ J721E_IOPAD(0x1e0, PIN_INPUT, 0) /* (Y5) SPI1_D0 */ J721E_IOPAD(0x1e4, PIN_INPUT, 0) /* (Y2) SPI1_D1 */ J721E_IOPAD(0x1d4, PIN_INPUT, 0) /* (Y3) SPI1_CS0 */ >; }; sub_can_pins_default: sub_can_pins_default { pinctrl-single,pins = < J721E_IOPAD(0x1f0, PIN_INPUT, 3) /* (AC2) UART0_CTSn.MCAN2_RX Register 0x0011c1f0 value = 0x00050003*/ J721E_IOPAD(0x1f4, PIN_OUTPUT, 3) /* (AB1) UART0_RTSn.MCAN2_TX Register 0x0011c1f4 value = 0x00010003*/ >; }; sensor_can_pins_default: sensor_can_pins_default { pinctrl-single,pins = < J721E_IOPAD(0x208, PIN_INPUT, 0) /* (W5) MCAN0_RX Register 0x0011 E208h value = 0x00050000*/ J721E_IOPAD(0x20c, PIN_OUTPUT, 0) /* (W6) MCAN0_TX Register 0x0011 E20ch value = 0x00010000*/ >; }; mdio_pins_default: mdio-pins-default { pinctrl-single,pins = < J721E_IOPAD(0x1bc, PIN_OUTPUT, 0) /* (V24) MDIO0_MDC */ J721E_IOPAD(0x1b8, PIN_INPUT, 0) /* (V26) MDIO0_MDIO */ >; }; radar_eth_eth3_pins_default: radar_eth_eth3_pins_default { pinctrl-single,pins = < J721E_IOPAD(0x4, PIN_INPUT, 4) /* (AC23) PRG1_PRU0_GPO0.RGMII1_RD0 */ J721E_IOPAD(0x8, PIN_INPUT, 4) /* (AG22) PRG1_PRU0_GPO1.RGMII1_RD1 */ J721E_IOPAD(0xc, PIN_INPUT, 4) /* (AF22) PRG1_PRU0_GPO2.RGMII1_RD2 */ J721E_IOPAD(0x10, PIN_INPUT, 4) /* (AJ23) PRG1_PRU0_GPO3.RGMII1_RD3 */ J721E_IOPAD(0x1c, PIN_INPUT, 4) /* (AD22) PRG1_PRU0_GPO6.RGMII1_RXC */ J721E_IOPAD(0x14, PIN_INPUT, 4) /* (AH23) PRG1_PRU0_GPO4.RGMII1_RX_CTL */ J721E_IOPAD(0x30, PIN_OUTPUT, 4) /* (AF24) PRG1_PRU0_GPO11.RGMII1_TD0 */ J721E_IOPAD(0x34, PIN_OUTPUT, 4) /* (AJ24) PRG1_PRU0_GPO12.RGMII1_TD1 */ J721E_IOPAD(0x38, PIN_OUTPUT, 4) /* (AG24) PRG1_PRU0_GPO13.RGMII1_TD2 */ J721E_IOPAD(0x3c, PIN_OUTPUT, 4) /* (AD24) PRG1_PRU0_GPO14.RGMII1_TD3 */ J721E_IOPAD(0x44, PIN_OUTPUT, 4) /* (AE24) PRG1_PRU0_GPO16.RGMII1_TXC */ J721E_IOPAD(0x40, PIN_OUTPUT, 4) /* (AC24) PRG1_PRU0_GPO15.RGMII1_TX_CTL */ J721E_IOPAD(0x20, PIN_INPUT, 7) /* (AE20) PRG1_PRU0_GPO7.GPIO0_8 CTRL.nRST */ J721E_IOPAD(0x2c, PIN_INPUT, 7) /* (AD21) PRG1_PRU0_GPO10.GPIO0_11 CTRL.WAKE */ >; }; lidar_eth_eth4_pins_default: lidar_eth_eth4_pins_default { pinctrl-single,pins = < J721E_IOPAD(0x58, PIN_INPUT, 4) /* (AE22) PRG1_PRU1_GPO0.RGMII2_RD0 */ J721E_IOPAD(0x5c, PIN_INPUT, 4) /* (AG23) PRG1_PRU1_GPO1.RGMII2_RD1 */ J721E_IOPAD(0x60, PIN_INPUT, 4) /* (AF23) PRG1_PRU1_GPO2.RGMII2_RD2 */ J721E_IOPAD(0x64, PIN_INPUT, 4) /* (AD23) PRG1_PRU1_GPO3.RGMII2_RD3 */ J721E_IOPAD(0x70, PIN_INPUT, 4) /* (AE23) PRG1_PRU1_GPO6.RGMII2_RXC */ J721E_IOPAD(0x68, PIN_INPUT, 4) /* (AH24) PRG1_PRU1_GPO4.RGMII2_RX_CTL */ J721E_IOPAD(0x84, PIN_OUTPUT, 4) /* (AJ25) PRG1_PRU1_GPO11.RGMII2_TD0 */ J721E_IOPAD(0x88, PIN_OUTPUT, 4) /* (AH25) PRG1_PRU1_GPO12.RGMII2_TD1 */ J721E_IOPAD(0x8c, PIN_OUTPUT, 4) /* (AG25) PRG1_PRU1_GPO13.RGMII2_TD2 */ J721E_IOPAD(0x90, PIN_OUTPUT, 4) /* (AH26) PRG1_PRU1_GPO14.RGMII2_TD3 */ J721E_IOPAD(0x98, PIN_OUTPUT, 4) /* (AJ26) PRG1_PRU1_GPO16.RGMII2_TXC */ J721E_IOPAD(0x94, PIN_OUTPUT, 4) /* (AJ27) PRG1_PRU1_GPO15.RGMII2_TX_CTL */ J721E_IOPAD(0x24, PIN_INPUT, 7) /* (AJ20) PRG1_PRU0_GPO8.GPIO0_9 CTRL.nRST */ J721E_IOPAD(0x74, PIN_INPUT, 7) /* (AC21) PRG1_PRU1_GPO7.GPIO0_28 CTRL.WAKE */ >; }; zonal_eth_eth1_pins_default: zonal_eth_eth1_pins_default { pinctrl-single,pins = < J721E_IOPAD(0xb0, PIN_INPUT, 4) /* (AF28) PRG0_PRU0_GPO0.RGMII3_RD0 */ J721E_IOPAD(0xb4, PIN_INPUT, 4) /* (AE28) PRG0_PRU0_GPO1.RGMII3_RD1 */ J721E_IOPAD(0xb8, PIN_INPUT, 4) /* (AE27) PRG0_PRU0_GPO2.RGMII3_RD2 */ J721E_IOPAD(0xbc, PIN_INPUT, 4) /* (AD26) PRG0_PRU0_GPO3.RGMII3_RD3 */ J721E_IOPAD(0xc8, PIN_INPUT, 4) /* (AE26) PRG0_PRU0_GPO6.RGMII3_RXC */ J721E_IOPAD(0xc0, PIN_INPUT, 4) /* (AD25) PRG0_PRU0_GPO4.RGMII3_RX_CTL */ J721E_IOPAD(0xdc, PIN_OUTPUT, 4) /* (AJ28) PRG0_PRU0_GPO11.RGMII3_TD0 */ J721E_IOPAD(0xe0, PIN_OUTPUT, 4) /* (AH27) PRG0_PRU0_GPO12.RGMII3_TD1 */ J721E_IOPAD(0xe4, PIN_OUTPUT, 4) /* (AH29) PRG0_PRU0_GPO13.RGMII3_TD2 */ J721E_IOPAD(0xe8, PIN_OUTPUT, 4) /* (AG28) PRG0_PRU0_GPO14.RGMII3_TD3 */ J721E_IOPAD(0xf0, PIN_OUTPUT, 4) /* (AH28) PRG0_PRU0_GPO16.RGMII3_TXC */ J721E_IOPAD(0xec, PIN_OUTPUT, 4) /* (AG27) PRG0_PRU0_GPO15.RGMII3_TX_CTL */ J721E_IOPAD(0xf8, PIN_INPUT, 7) /* (AB29) PRG0_PRU0_GPO18.GPIO0_61 CTRL.EN */ >; }; zonal_eth_eth2_pins_default: zonal_eth_eth2_pins_default { pinctrl-single,pins = < J721E_IOPAD(0x100, PIN_INPUT, 4) /* (AE29) PRG0_PRU1_GPO0.RGMII4_RD0 */ J721E_IOPAD(0x104, PIN_INPUT, 4) /* (AD28) PRG0_PRU1_GPO1.RGMII4_RD1 */ J721E_IOPAD(0x108, PIN_INPUT, 4) /* (AD27) PRG0_PRU1_GPO2.RGMII4_RD2 */ J721E_IOPAD(0x10c, PIN_INPUT, 4) /* (AC25) PRG0_PRU1_GPO3.RGMII4_RD3 */ J721E_IOPAD(0x118, PIN_INPUT, 4) /* (AC26) PRG0_PRU1_GPO6.RGMII4_RXC */ J721E_IOPAD(0x110, PIN_INPUT, 4) /* (AD29) PRG0_PRU1_GPO4.RGMII4_RX_CTL */ J721E_IOPAD(0x12c, PIN_OUTPUT, 4) /* (AG26) PRG0_PRU1_GPO11.RGMII4_TD0 */ J721E_IOPAD(0x130, PIN_OUTPUT, 4) /* (AF27) PRG0_PRU1_GPO12.RGMII4_TD1 */ J721E_IOPAD(0x134, PIN_OUTPUT, 4) /* (AF26) PRG0_PRU1_GPO13.RGMII4_TD2 */ J721E_IOPAD(0x138, PIN_OUTPUT, 4) /* (AE25) PRG0_PRU1_GPO14.RGMII4_TD3 */ J721E_IOPAD(0x140, PIN_OUTPUT, 4) /* (AG29) PRG0_PRU1_GPO16.RGMII4_TXC */ J721E_IOPAD(0x13c, PIN_OUTPUT, 4) /* (AF29) PRG0_PRU1_GPO15.RGMII4_TX_CTL */ J721E_IOPAD(0x264, PIN_INPUT, 7) /* (T29) MMC2_DAT2.GPIO1_24 CTRL.nRST */ J721E_IOPAD(0x260, PIN_INPUT, 7) /* (T28) MMC2_DAT3.GPIO1_23 CTRL.WAKE */ >; }; output_eth_eth5_pins_default: output_eth_eth5_pins_default { pinctrl-single,pins = < J721E_IOPAD(0x184, PIN_INPUT, 0) /* (T23) RGMII5_RD0 */ J721E_IOPAD(0x180, PIN_INPUT, 0) /* (R23) RGMII5_RD1 */ J721E_IOPAD(0x17c, PIN_INPUT, 0) /* (U24) RGMII5_RD2 */ J721E_IOPAD(0x178, PIN_INPUT, 0) /* (U27) RGMII5_RD3 */ J721E_IOPAD(0x174, PIN_INPUT, 0) /* (U25) RGMII5_RXC */ J721E_IOPAD(0x15c, PIN_INPUT, 0) /* (U26) RGMII5_RX_CTL */ J721E_IOPAD(0x16c, PIN_OUTPUT, 0) /* (U28) RGMII5_TD0 */ J721E_IOPAD(0x168, PIN_OUTPUT, 0) /* (V27) RGMII5_TD1 */ J721E_IOPAD(0x164, PIN_OUTPUT, 0) /* (V29) RGMII5_TD2 */ J721E_IOPAD(0x160, PIN_OUTPUT, 0) /* (V28) RGMII5_TD3 */ J721E_IOPAD(0x170, PIN_OUTPUT, 0) /* (U29) RGMII5_TXC */ J721E_IOPAD(0x158, PIN_OUTPUT, 0) /* (U23) RGMII5_TX_CTL */ J721E_IOPAD(0x28, PIN_INPUT, 7) /* (AG20) PRG1_PRU0_GPO9.GPIO0_10 CTRL.nRST */ J721E_IOPAD(0x144, PIN_INPUT, 7) /* (Y25) PRG0_PRU1_GPO17.GPIO0_80 CTRL.WAKE */ >; }; }; &wkup_pmx0 { lan865x_pins_default: lan865x_pins_default { pinctrl-single,pins = < /* J721E_WKUP_IOPAD(0xbc, PIN_OUTPUT, 7) (F27) WKUP_GPIO0_3 */ J721E_WKUP_IOPAD(0x7c, PIN_INPUT, 7) /* (D24) MCU_RGMII1_RD2.WKUP_GPIO0_47 */ >; }; zonal_eth_eth1_wkup_pins_default: zonal_eth_eth1_wkup_pins_default { pinctrl-single,pins = < J721E_WKUP_IOPAD(0xbc, PIN_INPUT, 7) /* (F27) WKUP_GPIO0_3 */ J721E_WKUP_IOPAD(0xdc, PIN_INPUT, 7) /* (H27) WKUP_GPIO0_11 */ >; }; }; &wkup_uart0 { /* Wakeup UART is used by System firmware */ status = "reserved"; }; &main_uart0 { power-domains = <&k3_pds 146 TI_SCI_PD_SHARED>; }; &main_uart3 { /* UART not brought out */ status = "disabled"; }; &main_uart5 { /* UART not brought out */ status = "disabled"; }; &main_uart6 { /* UART not brought out */ status = "disabled"; }; &main_uart7 { /* UART not brought out */ status = "disabled"; }; &main_uart8 { /* UART not brought out */ status = "disabled"; }; &main_uart9 { /* UART not brought out */ status = "disabled"; }; &main_gpio2 { status = "disabled"; }; &main_gpio3 { status = "disabled"; }; &main_gpio4 { status = "disabled"; }; &main_gpio5 { status = "disabled"; }; &main_gpio6 { status = "disabled"; }; &main_gpio7 { status = "disabled"; }; &wkup_gpio1 { status = "disabled"; }; &main_sdhci0 { /* eMMC */ non-removable; ti,driver-strength-ohm = <50>; disable-wp; }; &main_sdhci1 { /* SD/MMC */ vmmc-supply = <&vsys_3v3>; vqmmc-supply = <&vsys_3v3>; pinctrl-names = "default"; pinctrl-0 = <&main_mmc1_pins_default>; ti,driver-strength-ohm = <50>; disable-wp; }; &main_sdhci2 { /* Unused */ status = "disabled"; }; &main_i2c0 { pinctrl-names = "default"; pinctrl-0 = <&main_i2c0_pins_default>; clock-frequency = <400000>; exp1: gpio@20 { compatible = "ti,tca6416"; reg = <0x20>; gpio-controller; #gpio-cells = <2>; }; exp2: gpio@22 { compatible = "ti,tca6424"; reg = <0x22>; gpio-controller; #gpio-cells = <2>; p08-hog { /* P10 - PM_I2C_CTRL_OE */ gpio-hog; gpios = <8 GPIO_ACTIVE_HIGH>; output-high; line-name = "CTRL_PM_I2C_OE"; }; p09-hog { /* P11 - MCASP/TRACE_MUX_S0 */ gpio-hog; gpios = <9 GPIO_ACTIVE_HIGH>; output-low; line-name = "MCASP/TRACE_MUX_S0"; }; p10-hog { /* P12 - MCASP/TRACE_MUX_S1 */ gpio-hog; gpios = <10 GPIO_ACTIVE_HIGH>; output-high; line-name = "MCASP/TRACE_MUX_S1"; }; }; }; &main_i2c1 { pinctrl-names = "default"; pinctrl-0 = <&main_i2c1_pins_default>; clock-frequency = <400000>; gmsl96789: gmsl96789@40 { compatible = "ti,max96789"; reg = <0x40>; }; }; &main_spi1 { pinctrl-names = "default"; pinctrl-0 = <&main_spi1_pins_default>; status = "okay"; eth6: lan865x@0 { compatible = "microchip,lan865x"; reg = <0>; /* CE0 */ local-mac-address = [04 05 06 01 02 03]; spi-max-frequency = <15000000>; pinctrl-names = "default"; pinctrl-0 = <&lan865x_pins_default>; /* Need to change reset-pin */ /* reset-pin-gpios = <&wkup_gpio0 3 GPIO_ACTIVE_LOW>; */ irq-pin-gpios = <&wkup_gpio0 47 GPIO_ACTIVE_LOW>; /* PLCA settings */ plca-enable = /bits/ 8 <1>; /* 1 - PLCA enable, 0 - CSMA/CD enable */ plca-node-id = /bits/ 8 <0>; /* PLCA node id range: 0 to 254 */ plca-node-count = /bits/ 8 <8>; /* PLCA node count range: 1 to 255 */ tx-cut-through-mode = /bits/ 8 <1>; /* 1 - tx cut through mode enable, 0 - Store and forward mode enable */ status = "disabled"; }; }; &cmn_refclk1 { clock-frequency = <100000000>; }; &wiz0_pll1_refclk { assigned-clocks = <&wiz0_pll1_refclk>; assigned-clock-parents = <&cmn_refclk1>; }; &wiz0_refclk_dig { assigned-clocks = <&wiz0_refclk_dig>; assigned-clock-parents = <&cmn_refclk1>; }; &wiz1_pll1_refclk { assigned-clocks = <&wiz1_pll1_refclk>; assigned-clock-parents = <&cmn_refclk1>; }; &wiz1_refclk_dig { assigned-clocks = <&wiz1_refclk_dig>; assigned-clock-parents = <&cmn_refclk1>; }; &wiz2_pll1_refclk { assigned-clocks = <&wiz2_pll1_refclk>; assigned-clock-parents = <&cmn_refclk1>; }; &wiz2_refclk_dig { assigned-clocks = <&wiz2_refclk_dig>; assigned-clock-parents = <&cmn_refclk1>; }; &cmn_refclk1 { clock-frequency = <100000000>; }; &serdes0 { assigned-clocks = <&serdes0 CDNS_SIERRA_PLL_CMNLC>, <&serdes0 CDNS_SIERRA_PLL_CMNLC1>; assigned-clock-parents = <&wiz0_pll1_refclk>, <&wiz0_pll1_refclk>; serdes0_pcie_link: phy@0 { reg = <0>; cdns,num-lanes = <1>; #phy-cells = <0>; cdns,phy-type = <PHY_TYPE_PCIE>; resets = <&serdes_wiz0 1>; }; serdes0_qsgmii_link: phy@1 { reg = <1>; cdns,num-lanes = <1>; #phy-cells = <0>; cdns,phy-type = <PHY_TYPE_QSGMII>; resets = <&serdes_wiz0 2>; }; }; &serdes1 { assigned-clocks = <&serdes1 CDNS_SIERRA_PLL_CMNLC>; assigned-clock-parents = <&wiz1_pll1_refclk>; serdes1_pcie_link: phy@0 { reg = <0>; cdns,num-lanes = <2>; #phy-cells = <0>; cdns,phy-type = <PHY_TYPE_PCIE>; resets = <&serdes_wiz1 1>, <&serdes_wiz1 2>; }; }; &serdes2 { assigned-clocks = <&serdes2 CDNS_SIERRA_PLL_CMNLC>; assigned-clock-parents = <&wiz2_pll1_refclk>; serdes2_pcie_link: phy@0 { reg = <0>; cdns,num-lanes = <2>; #phy-cells = <0>; cdns,phy-type = <PHY_TYPE_PCIE>; resets = <&serdes_wiz2 1>, <&serdes_wiz2 2>; }; }; #if 0 &cpsw0 { /* * Disable cpsw0 since cpsw9g_virt_mac is the default Ethernet * controller. cpsw0 is enabled with overlay for native * Ethernet driver support. */ status = "disabled"; }; #endif &cpsw0 { status = "okay"; pinctrl-names = "default"; pinctrl-0 = <&mdio_pins_default &radar_eth_eth3_pins_default &lidar_eth_eth4_pins_default &zonal_eth_eth1_pins_default &zonal_eth_eth2_pins_default &output_eth_eth5_pins_default>; }; &cpsw0_port1 { phy-handle = <&cpsw9g_phy5>; phy-mode = "rgmii-rxid"; mac-address = [00 00 00 00 00 01]; phys = <&cpsw0_phy_gmii_sel 1>; }; &cpsw0_port2 { phy-handle = <&cpsw9g_phy8>; phy-mode = "rgmii-rxid"; mac-address = [00 00 00 00 00 02]; phys = <&cpsw0_phy_gmii_sel 2>; }; &cpsw0_port3 { phy-handle = <&cpsw9g_phy0>; phy-mode = "rgmii-rxid"; mac-address = [00 00 00 00 00 03]; phys = <&cpsw0_phy_gmii_sel 3>; }; &cpsw0_port4 { phy-handle = <&cpsw9g_phy4>; phy-mode = "rgmii-rxid"; mac-address = [00 00 00 00 00 04]; phys = <&cpsw0_phy_gmii_sel 4>; }; &cpsw0_port5 { phy-handle = <&cpsw9g_phy10>; phy-mode = "rgmii-rxid"; mac-address = [00 00 00 00 00 05]; phys = <&cpsw0_phy_gmii_sel 5>; }; &cpsw0_port6 { status = "disabled"; }; &cpsw0_port7 { status = "disabled"; }; &cpsw0_port8 { status = "disabled"; }; &cpsw9g_mdio { bus_freq = <1000000>; #address-cells = <1>; #size-cells = <0>; cpsw9g_phy0: ethernet-phy@0 { reg = <0>; ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>; ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>; ti,min-output-impedance; pinctrl-names = "default"; //pinctrl-0 = <&zonal_eth_eth1_pins_default // &zonal_eth_eth1_wkup_pins_default>; gpios = <&wkup_gpio0 3 GPIO_ACTIVE_LOW &wkup_gpio0 11 GPIO_ACTIVE_HIGH &main_gpio0 61 GPIO_ACTIVE_HIGH>; }; cpsw9g_phy4: ethernet-phy@4 { reg = <4>; ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>; ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>; ti,min-output-impedance; pinctrl-names = "default"; // pinctrl-0 = <&zonal_eth_eth2_pins_default>; gpios = <&main_gpio1 24 GPIO_ACTIVE_LOW &main_gpio1 23 GPIO_ACTIVE_HIGH>; }; cpsw9g_phy5: ethernet-phy@5 { reg = <5>; ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>; ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>; ti,min-output-impedance; pinctrl-names = "default"; // pinctrl-0 = <&radar_eth_eth3_pins_default>; gpios = <&main_gpio0 8 GPIO_ACTIVE_LOW &main_gpio0 11 GPIO_ACTIVE_HIGH>; }; cpsw9g_phy8: ethernet-phy@8 { reg = <8>; ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>; ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>; ti,min-output-impedance; pinctrl-names = "default"; // pinctrl-0 = <&lidar_eth_eth4_pins_default>; gpios = <&main_gpio0 9 GPIO_ACTIVE_LOW &main_gpio0 28 GPIO_ACTIVE_HIGH>; }; cpsw9g_phy10: ethernet-phy@10 { reg = <8>; ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>; ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>; ti,min-output-impedance; pinctrl-names = "default"; // pinctrl-0 = <&output_eth_eth5_pins_default>; gpios = <&main_gpio0 10 GPIO_ACTIVE_LOW &main_gpio0 80 GPIO_ACTIVE_HIGH>; }; }; &pcie0_rc { reset-gpios = <&exp1 6 GPIO_ACTIVE_HIGH>; phys = <&serdes0_pcie_link>; phy-names = "pcie-phy"; num-lanes = <1>; status = "disabled"; }; &pcie1_rc { reset-gpios = <&exp1 2 GPIO_ACTIVE_HIGH>; phys = <&serdes1_pcie_link>; phy-names = "pcie-phy"; num-lanes = <2>; status = "disabled"; }; &pcie2_rc { reset-gpios = <&exp2 20 GPIO_ACTIVE_HIGH>; phys = <&serdes2_pcie_link>; phy-names = "pcie-phy"; num-lanes = <2>; status = "disabled"; }; &pcie0_ep { phys = <&serdes0_pcie_link>; phy-names = "pcie-phy"; num-lanes = <1>; status = "disabled"; }; &pcie1_ep { phys = <&serdes1_pcie_link>; phy-names = "pcie-phy"; num-lanes = <2>; status = "disabled"; }; &pcie2_ep { phys = <&serdes2_pcie_link>; phy-names = "pcie-phy"; num-lanes = <2>; status = "disabled"; }; &pcie3_rc { status = "disabled"; }; &pcie3_ep { status = "disabled"; }; /* uart2 assigned to cpsw9g eth-switch fw running on remote CPU core */ &main_uart2 { status = "disabled"; }; &main_mcan0 { status = "okay"; pinctrl-names = "default"; pinctrl-0 = <&sensor_can_pins_default>; phys = <&transceiver1>; }; &main_mcan1 { status = "disabled"; }; &main_mcan2 { status = "okay"; pinctrl-names = "default"; pinctrl-0 = <&sub_can_pins_default>; phys = <&transceiver2>; }; &main_mcan3 { status = "disabled"; }; &main_mcan4 { status = "disabled"; }; &main_mcan5 { status = "disabled"; }; &main_mcan6 { status = "disabled"; }; &main_mcan7 { status = "disabled"; }; &main_mcan8 { status = "disabled"; }; &main_mcan9 { status = "disabled"; }; &main_mcan10 { status = "disabled"; }; &main_mcan11 { status = "disabled"; }; &main_mcan12 { status = "disabled"; }; &main_mcan13 { status = "disabled"; }; &csi0_port0 { status = "disabled"; }; &csi0_port1 { status = "disabled"; }; &csi0_port2 { status = "disabled"; }; &csi0_port3 { status = "disabled"; }; &csi0_port4 { status = "disabled"; }; &main_spi4 { status = "disabled"; }; &mcu_spi0 { status = "disabled"; }; &mcu_spi1 { status = "disabled"; }; &mcu_spi2 { status = "disabled"; }; &main_ehrpwm0 { status = "disabled"; }; &main_ehrpwm1 { status = "disabled"; }; &main_ehrpwm2 { status = "disabled"; }; &main_ehrpwm3 { status = "disabled"; }; &main_ehrpwm4 { status = "disabled"; }; &main_ehrpwm5 { status = "disabled"; }; &wkup_i2c0 { status = "okay"; pinctrl-names = "default"; pinctrl-0 = <&wkup_i2c0_pins_default>; clock-frequency = <400000>; tps659413: tps659413@48 { reg = <0x48>; compatible = "ti,tps659413"; }; tps659411: tps659411@4C { reg = <0x4C>; compatible = "ti,tps659411"; }; }; &mcu_i2c0 { pinctrl-names = "default"; pinctrl-0 = <&mcu_i2c0_pins_default>; clock-frequency = <400000>; tps659413_wd: tps659413_wd@12 { reg = <0x12>; compatible = "ti,tps659413_wd"; }; }; &main_r5fss0_core0 { firmware-name = "pdk-ipc/ipc_echo_test_mcu2_0_release_strip.xer5f"; };

中的修改总结为:

#在 &main_pmx0中:我添加了我的5个 PHY 的 pinmux 控制

# wkup_pmx0: pinmux 控制,但使用唤醒 GPIO

#按照 k3-j721e-gesi-exp-board.dts 定义&cpsw0和&cpsw0_port*

#为 asliases 我添加到 k3-j721e.dtsi

DP83TG720 驱动程序。 我在此处获得: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1213956/tda4vm-cpswng-native-ethernet-on-linux/4585015#4585015

然后尝试引导内核时执行该操作。 我已经看到驾驶员受到了探测。

这是我的完整启动日志

U-Boot SPL 2021.01-g7996ed51f1 (Jun 20 2023 - 07:58:29 +0000) Model: Texas Instruments K3 J721E SoC Board: rev SYSFW ABI: 3.1 (firmware rev 0x0008 '8.5.2--v08.05.02 (Chill Capybar') Trying to boot from MMC2 Starting ATF on ARM64 core... NOTICE: BL31: v2.7(release):v2.7.0-359-g1309c6c805-dirty NOTICE: BL31: Built : 07:46:16, Dec 18 2022 I/TC: I/TC: OP-TEE version: 3.19.0 (gcc version 9.2.1 20191025 (GNU Toolchain for the A-profile Architecture 9.2-2019.12 (arm-9.10))) #1 Sun Dec 18 07:46:21 UTC 2022 aarch64 I/TC: WARNING: This OP-TEE configuration might be insecure! I/TC: WARNING: Please check optee.readthedocs.io/.../porting_guidelines.html I/TC: Primary CPU initializing I/TC: SYSFW ABI: 3.1 (firmware rev 0x0008 '8.5.2--v08.05.02 (Chill Capybar') I/TC: HUK Initialized I/TC: Activated SA2UL device I/TC: Fixing SA2UL firewall owner for GP device I/TC: Enabled firewalls for SA2UL TRNG device I/TC: SA2UL TRNG initialized I/TC: SA2UL Drivers initialized I/TC: Primary CPU switching to normal world boot U-Boot SPL 2021.01-dirty (Jun 26 2023 - 09:54:17 +0700) Model: Texas Instruments K3 J721E SoC Board: rev SYSFW ABI: 3.1 (firmware rev 0x0008 '8.5.2--v08.05.02 (Chill Capybar') Trying to boot from MMC2 U-Boot 2021.01-dirty (Jun 26 2023 - 09:54:17 +0700) SoC: J721E SR1.1 GP Model: Texas Instruments K3 J721E SoC Board: rev DRAM: 4 GiB Flash: 0 Bytes MMC: sdhci@4f80000: 0, sdhci@4fb0000: 1 Loading Environment from FAT... OK In: serial@2800000 Out: serial@2800000 Err: serial@2800000 am65_cpsw_nuss ethernet@46000000: K3 CPSW: nuss_ver: 0x6BA00101 cpsw_ver: 0x6BA80100 ale_ver: 0x00293904 Ports:1 mdio_freq:1000000 Unidentified board claims in eeprom header cdns,sierra serdes@5000000: PHY not found 0x7364 vs 0x0 Sierra init failed:-22 Net: Could not get PHY for ethernet@46000000port@1: addr 0 am65_cpsw_nuss_port ethernet@46000000port@1: phy_connect() failed No ethernet found. Hit any key to stop autoboot: 0 => boot switch to partitions #0, OK mmc1 is current device SD/MMC found on device 1 Failed to load 'boot.scr' 483 bytes read in 9 ms (51.8 KiB/s) Loaded env from uEnv.txt Importing environment from mmc1 ... Running uenvcmd ... 1 bytes read in 8 ms (0 Bytes/s) Already setup. i2c_write: error waiting for data ACK (status=0x116) pca953x gpio@20: Error reading output register GPIO: 'gpio@22_17' not found Command 'gpio' failed: Error -121 i2c_write: error waiting for data ACK (status=0x116) pca953x gpio@20: Error reading output register GPIO: 'gpio@22_16' not found Command 'gpio' failed: Error -121 k3_r5f_rproc r5f@41000000: Core 1 is already in use. No rproc commands work k3_r5f_rproc r5f@41400000: Core 2 is already in use. No rproc commands work 1375608 bytes read in 66 ms (19.9 MiB/s) Load Remote Processor 2 with data@addr=0x82000000 1375608 bytes: Success! 302028 bytes read in 23 ms (12.5 MiB/s) Load Remote Processor 3 with data@addr=0x82000000 302028 bytes: Success! Failed to load '/lib/firmware/j7-main-r5f1_0-fw' Failed to load '/lib/firmware/j7-main-r5f1_1-fw' 1325844 bytes read in 66 ms (19.2 MiB/s) Load Remote Processor 6 with data@addr=0x82000000 1325844 bytes: Success! 1325844 bytes read in 65 ms (19.5 MiB/s) Load Remote Processor 7 with data@addr=0x82000000 1325844 bytes: Success! 12849160 bytes read in 212 ms (57.8 MiB/s) Load Remote Processor 8 with data@addr=0x82000000 12849160 bytes: Success! 18682368 bytes read in 777 ms (22.9 MiB/s) 106139 bytes read in 12 ms (8.4 MiB/s) 11545 bytes read in 11 ms (1 MiB/s) ## Flattened Device Tree blob at 88000000 Booting using the fdt blob at 0x88000000 Loading Device Tree to 000000008fee3000, end 000000008fffffff ... OK Starting kernel ... [ 0.000000] Booting Linux on physical CPU 0x0000000000 [0x411fd080] [ 0.000000] Linux version 5.10.153-g891b3adc38c8-dirty (jkts@ubuntu) (aarch64-none-linux-gnu-gcc (GNU Toolchain for the A-profile Architecture 9.2-2019.12 (arm-9.10)) 9.2.1 20191025, GNU ld (GNU Toolchain for the A-profile Architecture 9.2-2019.12 (arm-9.10)) 2.33.1.20191209) #9 SMP PREEMPT Thu Jun 29 21:17:34 +07 2023 [ 0.000000] Machine model: Texas Instruments K3 J721E SoC [ 0.000000] earlycon: ns16550a0 at MMIO32 0x0000000002800000 (options '') [ 0.000000] printk: bootconsole [ns16550a0] enabled [ 0.000000] efi: UEFI not found. [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a0000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-dma-memory@a0000000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a0100000, size 15 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-memory@a0100000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a1000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-dma-memory@a1000000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a1100000, size 15 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-memory@a1100000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a2000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-dma-memory@a2000000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a2100000, size 31 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-memory@a2100000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a4000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-dma-memory@a4000000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a4100000, size 31 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-memory@a4100000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a6000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-dma-memory@a6000000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a6100000, size 15 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-memory@a6100000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a7000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-dma-memory@a7000000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a7100000, size 15 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-memory@a7100000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a8000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-c66-dma-memory@a8000000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a8100000, size 15 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-c66-memory@a8100000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a9000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-c66-dma-memory@a9000000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a9100000, size 15 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-c66-memory@a9100000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000ac000000, size 96 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-dma-memory@ac000000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000b2000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-c71-dma-memory@b2000000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000b2100000, size 95 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-c71-memory@b2100000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: initialized node vision_apps_shared-memories, compatible id dma-heap-carveout [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000d8000000, size 192 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-core-heap-memory-lo@d8000000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000e4000000, size 8 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-virtual-eth-queues@e4000000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000e4800000, size 24 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-virtual-eth-buffers@e4800000, compatible id shared-dma-pool [ 0.000000] Reserved memory: created DMA memory pool at 0x0000000880000000, size 624 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-core-heap-memory-hi@880000000, compatible id shared-dma-pool [ 0.000000] Zone ranges: [ 0.000000] DMA [mem 0x0000000080000000-0x00000000ffffffff] [ 0.000000] DMA32 empty [ 0.000000] Normal [mem 0x0000000100000000-0x00000008ffffffff] [ 0.000000] Movable zone start for each node [ 0.000000] Early memory node ranges [ 0.000000] node 0: [mem 0x0000000080000000-0x000000009e7fffff] [ 0.000000] node 0: [mem 0x000000009e800000-0x00000000b7ffffff] [ 0.000000] node 0: [mem 0x00000000b8000000-0x00000000d7ffffff] [ 0.000000] node 0: [mem 0x00000000d8000000-0x00000000e5ffffff] [ 0.000000] node 0: [mem 0x00000000e6000000-0x00000000ffffffff] [ 0.000000] node 0: [mem 0x0000000880000000-0x00000008a6ffffff] [ 0.000000] node 0: [mem 0x00000008a7000000-0x00000008ffffffff] [ 0.000000] Initmem setup node 0 [mem 0x0000000080000000-0x00000008ffffffff] [ 0.000000] cma: Reserved 400 MiB at 0x00000000e7000000 [ 0.000000] psci: probing for conduit method from DT. [ 0.000000] psci: PSCIv1.1 detected in firmware. [ 0.000000] psci: Using standard PSCI v0.2 function IDs [ 0.000000] psci: Trusted OS migration not required [ 0.000000] psci: SMC Calling Convention v1.2 [ 0.000000] percpu: Embedded 22 pages/cpu s50008 r8192 d31912 u90112 [ 0.000000] Detected PIPT I-cache on CPU0 [ 0.000000] CPU features: detected: GIC system register CPU interface [ 0.000000] CPU features: detected: EL2 vector hardening [ 0.000000] CPU features: detected: ARM errata 1165522, 1319367, or 1530923 [ 0.000000] CPU features: detected: Spectre-BHB [ 0.000000] CPU features: detected: ARM erratum 1742098 [ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 1032192 [ 0.000000] Kernel command line: console=ttyS2,115200n8 earlycon=ns16550a,mmio32,0x02800000 mtdparts=47040000.spi.0:512k(ospi.tiboot3),2m(ospi.tispl),4m(ospi.u-boot),256k(ospi.env),1m(ospi.sysfw),256k(ospi.env.backup),57088k@8m(ospi.rootfs),256k(ospi.phypattern);47034000.hyperbus:512k(hbmc.tiboot3),2m(hbmc.tispl),4m(hbmc.u-boot),256k(hbmc.env),1m(hbmc.sysfw),-@8m(hbmc.rootfs) root=PARTUUID=c025843b-02 rw rootfstype=ext4 rootwait [ 0.000000] Dentry cache hash table entries: 524288 (order: 10, 4194304 bytes, linear) [ 0.000000] Inode-cache hash table entries: 262144 (order: 9, 2097152 bytes, linear) [ 0.000000] mem auto-init: stack:off, heap alloc:off, heap free:off [ 0.000000] software IO TLB: mapped [mem 0x000000009a800000-0x000000009e800000] (64MB) [ 0.000000] Memory: 1811476K/4194304K available (10944K kernel code, 1156K rwdata, 4232K rodata, 1792K init, 457K bss, 1973228K reserved, 409600K cma-reserved) [ 0.000000] SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=2, Nodes=1 [ 0.000000] rcu: Preemptible hierarchical RCU implementation. [ 0.000000] rcu: RCU event tracing is enabled. [ 0.000000] rcu: RCU restricting CPUs from NR_CPUS=256 to nr_cpu_ids=2. [ 0.000000] Trampoline variant of Tasks RCU enabled. [ 0.000000] rcu: RCU calculated value of scheduler-enlistment delay is 25 jiffies. [ 0.000000] rcu: Adjusting geometry for rcu_fanout_leaf=16, nr_cpu_ids=2 [ 0.000000] NR_IRQS: 64, nr_irqs: 64, preallocated irqs: 0 [ 0.000000] GICv3: GIC: Using split EOI/Deactivate mode [ 0.000000] GICv3: 960 SPIs implemented [ 0.000000] GICv3: 0 Extended SPIs implemented [ 0.000000] GICv3: Distributor has no Range Selector support [ 0.000000] GICv3: 16 PPIs implemented [ 0.000000] GICv3: CPU0: found redistributor 0 region 0:0x0000000001900000 [ 0.000000] ITS [mem 0x01820000-0x0182ffff] [ 0.000000] GIC: enabling workaround for ITS: Socionext Synquacer pre-ITS [ 0.000000] ITS@0x0000000001820000: Devices Table too large, reduce ids 20->19 [ 0.000000] ITS@0x0000000001820000: allocated 524288 Devices @8a7800000 (flat, esz 8, psz 64K, shr 0) [ 0.000000] ITS: using cache flushing for cmd queue [ 0.000000] GICv3: using LPI property table @0x00000008a7030000 [ 0.000000] GIC: using cache flushing for LPI property table [ 0.000000] GICv3: CPU0: using allocated LPI pending table @0x00000008a7040000 [ 0.000000] arch_timer: cp15 timer(s) running at 200.00MHz (phys). [ 0.000000] clocksource: arch_sys_counter: mask: 0xffffffffffffff max_cycles: 0x2e2049d3e8, max_idle_ns: 440795210634 ns [ 0.000002] sched_clock: 56 bits at 200MHz, resolution 5ns, wraps every 4398046511102ns [ 0.008396] Console: colour dummy device 80x25 [ 0.012962] Calibrating delay loop (skipped), value calculated using timer frequency.. 400.00 BogoMIPS (lpj=800000) [ 0.023634] pid_max: default: 32768 minimum: 301 [ 0.028390] LSM: Security Framework initializing [ 0.033150] Mount-cache hash table entries: 8192 (order: 4, 65536 bytes, linear) [ 0.040731] Mountpoint-cache hash table entries: 8192 (order: 4, 65536 bytes, linear) [ 0.049539] rcu: Hierarchical SRCU implementation. [ 0.054600] Platform MSI: msi-controller@1820000 domain created [ 0.060844] PCI/MSI: /bus@100000/interrupt-controller@1800000/msi-controller@1820000 domain created [ 0.070145] EFI services will not be available. [ 0.074886] smp: Bringing up secondary CPUs ... I/TC: Secondary CPU 1 initializing I/TC: Secondary CPU 1 switching to normal world boot [ 0.088135] Detected PIPT I-cache on CPU1 [ 0.088160] GICv3: CPU1: found redistributor 1 region 0:0x0000000001920000 [ 0.088171] GICv3: CPU1: using allocated LPI pending table @0x00000008a7050000 [ 0.088207] CPU1: Booted secondary processor 0x0000000001 [0x411fd080] [ 0.088257] smp: Brought up 1 node, 2 CPUs [ 0.117602] SMP: Total of 2 processors activated. [ 0.122407] CPU features: detected: 32-bit EL0 Support [ 0.127661] CPU features: detected: CRC32 instructions [ 0.141783] CPU: All CPU(s) started at EL2 [ 0.145979] alternatives: patching kernel code [ 0.151024] devtmpfs: initialized [ 0.159990] KASLR disabled due to lack of seed [ 0.164636] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 7645041785100000 ns [ 0.174600] futex hash table entries: 512 (order: 3, 32768 bytes, linear) [ 0.187777] pinctrl core: initialized pinctrl subsystem [ 0.193452] DMI not present or invalid. [ 0.197702] NET: Registered protocol family 16 [ 0.202949] DMA: preallocated 512 KiB GFP_KERNEL pool for atomic allocations [ 0.210278] DMA: preallocated 512 KiB GFP_KERNEL|GFP_DMA pool for atomic allocations [ 0.218351] DMA: preallocated 512 KiB GFP_KERNEL|GFP_DMA32 pool for atomic allocations [ 0.226658] thermal_sys: Registered thermal governor 'step_wise' [ 0.226660] thermal_sys: Registered thermal governor 'power_allocator' [ 0.233248] hw-breakpoint: found 6 breakpoint and 4 watchpoint registers. [ 0.246879] ASID allocator initialised with 65536 entries [ 0.269659] HugeTLB registered 1.00 GiB page size, pre-allocated 0 pages [ 0.276519] HugeTLB registered 32.0 MiB page size, pre-allocated 0 pages [ 0.283366] HugeTLB registered 2.00 MiB page size, pre-allocated 0 pages [ 0.290211] HugeTLB registered 64.0 KiB page size, pre-allocated 0 pages [ 0.297692] cryptd: max_cpu_qlen set to 1000 [ 0.303816] k3-chipinfo 43000014.chipid: Family:J721E rev:SR2.0 JTAGID[0x1bb6402f] Detected [ 0.312644] vsys_3v3: supplied by evm_12v0 [ 0.317004] vsys_5v0: supplied by evm_12v0 [ 0.321699] iommu: Default domain type: Translated [ 0.326870] SCSI subsystem initialized [ 0.331007] mc: Linux media interface: v0.10 [ 0.335384] videodev: Linux video capture interface: v2.00 [ 0.341021] pps_core: LinuxPPS API ver. 1 registered [ 0.346092] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it> [ 0.355429] PTP clock support registered [ 0.359451] EDAC MC: Ver: 3.0.0 [ 0.363246] FPGA manager framework [ 0.366753] Advanced Linux Sound Architecture Driver Initialized. [ 0.373354] clocksource: Switched to clocksource arch_sys_counter [ 0.379682] VFS: Disk quotas dquot_6.6.0 [ 0.383716] VFS: Dquot-cache hash table entries: 512 (order 0, 4096 bytes) [ 0.393328] Carveout Heap: Exported 512 MiB at 0x00000000b8000000 [ 0.399620] NET: Registered protocol family 2 [ 0.404365] IP idents hash table entries: 65536 (order: 7, 524288 bytes, linear) [ 0.412956] tcp_listen_portaddr_hash hash table entries: 2048 (order: 3, 32768 bytes, linear) [ 0.421713] TCP established hash table entries: 32768 (order: 6, 262144 bytes, linear) [ 0.429916] TCP bind hash table entries: 32768 (order: 7, 524288 bytes, linear) [ 0.437736] TCP: Hash tables configured (established 32768 bind 32768) [ 0.444538] UDP hash table entries: 2048 (order: 4, 65536 bytes, linear) [ 0.451432] UDP-Lite hash table entries: 2048 (order: 4, 65536 bytes, linear) [ 0.458841] NET: Registered protocol family 1 [ 0.463560] RPC: Registered named UNIX socket transport module. [ 0.469615] RPC: Registered udp transport module. [ 0.474431] RPC: Registered tcp transport module. [ 0.479235] RPC: Registered tcp NFSv4.1 backchannel transport module. [ 0.485819] PCI: CLS 0 bytes, default 64 [ 0.490214] hw perfevents: enabled with armv8_cortex_a72 PMU driver, 7 counters available [ 0.500653] Initialise system trusted keyrings [ 0.505293] workingset: timestamp_bits=46 max_order=20 bucket_order=0 [ 0.513503] squashfs: version 4.0 (2009/01/31) Phillip Lougher [ 0.519698] NFS: Registering the id_resolver key type [ 0.524895] Key type id_resolver registered [ 0.529170] Key type id_legacy registered [ 0.533287] nfs4filelayout_init: NFSv4 File Layout Driver Registering... [ 0.540135] nfs4flexfilelayout_init: NFSv4 Flexfile Layout Driver Registering... [ 0.547784] 9p: Installing v9fs 9p2000 file system support [ 0.572947] Key type asymmetric registered [ 0.577133] Asymmetric key parser 'x509' registered [ 0.582135] Block layer SCSI generic (bsg) driver version 0.4 loaded (major 243) [ 0.589694] io scheduler mq-deadline registered [ 0.594319] io scheduler kyber registered [ 0.599984] pinctrl-single 4301c000.pinctrl: 94 pins, size 376 [ 0.606170] pinctrl-single 11c000.pinctrl: 173 pins, size 692 [ 0.614873] k3-ringacc 2b800000.ringacc: Failed to get MSI domain [ 0.621143] k3-ringacc 3c000000.ringacc: Failed to get MSI domain [ 0.627490] ti-pat 31010000.pat: Found PAT Rev 1.0 with 16384 pages [ 0.633906] debugfs: Directory '31010000.pat' with parent 'regmap' already present! [ 0.641902] ti-pat 31011000.pat: Found PAT Rev 1.0 with 16384 pages [ 0.648321] debugfs: Directory '31011000.pat' with parent 'regmap' already present! [ 0.656267] ti-pat 31012000.pat: Found PAT Rev 1.0 with 16384 pages [ 0.662686] debugfs: Directory '31012000.pat' with parent 'regmap' already present! [ 0.670619] ti-pat 31013000.pat: Found PAT Rev 1.0 with 2048 pages [ 0.676942] debugfs: Directory '31013000.pat' with parent 'regmap' already present! [ 0.684889] ti-pat 31014000.pat: Found PAT Rev 1.0 with 2048 pages [ 0.691217] debugfs: Directory '31014000.pat' with parent 'regmap' already present! [ 0.700889] Serial: 8250/16550 driver, 10 ports, IRQ sharing enabled [ 0.709097] arm-smmu-v3 36600000.iommu: ias 48-bit, oas 48-bit (features 0x00001faf) [ 0.717411] arm-smmu-v3 36600000.iommu: allocated 65536 entries for cmdq [ 0.724519] arm-smmu-v3 36600000.iommu: allocated 32768 entries for evtq [ 0.733230] arm-smmu-v3 36600000.iommu: msi_domain absent - falling back to wired irqs [ 0.741852] gmsl96789:INIT [ 0.749050] brd: module loaded [ 0.755634] loop: module loaded [ 0.759499] megasas: 07.714.04.00-rc1 [ 0.765303] tun: Universal TUN/TAP device driver, 1.6 [ 0.770763] igbvf: Intel(R) Gigabit Virtual Function Network Driver [ 0.777169] igbvf: Copyright (c) 2009 - 2012 Intel Corporation. [ 0.783241] sky2: driver version 1.30 [ 0.787701] VFIO - User Level meta-driver version: 0.3 [ 0.793489] i2c /dev entries driver [ 0.797302] tps659413:INIT [ 0.800081] tps659413_wd:INIT [ 0.803119] tps659411:INIT [ 0.806522] sdhci: Secure Digital Host Controller Interface driver [ 0.812839] sdhci: Copyright(c) Pierre Ossman [ 0.817491] sdhci-pltfm: SDHCI platform and OF driver helper [ 0.823867] ledtrig-cpu: registered to indicate activity on CPUs [ 0.830203] SMCCC: SOC_ID: ARCH_SOC_ID not implemented, skipping .... [ 0.837585] optee: probing for conduit method. [ 0.842139] optee: revision 3.19 (afacf356) [ 0.842279] optee: dynamic shared memory is enabled [ 0.851746] optee: initialized driver [ 0.856952] NET: Registered protocol family 17 [ 0.861580] 9pnet: Installing 9P2000 support [ 0.865981] Key type dns_resolver registered [ 0.870439] Loading compiled-in X.509 certificates [ 0.880108] k3-ringacc 2b800000.ringacc: Failed to get MSI domain [ 0.886451] k3-ringacc 3c000000.ringacc: Failed to get MSI domain [ 0.895626] ti-sci 44083000.dmsc: ABI: 3.1 (firmware rev 0x0008 '8.5.2--v08.05.02 (Chill Capybar') [ 0.961055] davinci-mcasp 2b00000.mcasp: invalid tdm slots: 0 [ 0.966953] davinci-mcasp 2b00000.mcasp: IRQ common not found [ 0.973381] davinci-mcasp 2b10000.mcasp: invalid tdm slots: 0 [ 0.979273] davinci-mcasp 2b10000.mcasp: IRQ common not found [ 0.985583] davinci-mcasp 2b20000.mcasp: invalid tdm slots: 0 [ 0.991471] davinci-mcasp 2b20000.mcasp: IRQ common not found [ 0.997753] davinci-mcasp 2b30000.mcasp: invalid tdm slots: 0 [ 1.003648] davinci-mcasp 2b30000.mcasp: IRQ common not found [ 1.009916] davinci-mcasp 2b40000.mcasp: invalid tdm slots: 0 [ 1.015808] davinci-mcasp 2b40000.mcasp: IRQ common not found [ 1.022095] davinci-mcasp 2b50000.mcasp: invalid tdm slots: 0 [ 1.027993] davinci-mcasp 2b50000.mcasp: IRQ common not found [ 1.034253] davinci-mcasp 2b60000.mcasp: invalid tdm slots: 0 [ 1.040154] davinci-mcasp 2b60000.mcasp: IRQ common not found [ 1.046416] davinci-mcasp 2b70000.mcasp: invalid tdm slots: 0 [ 1.052311] davinci-mcasp 2b70000.mcasp: IRQ common not found [ 1.058560] davinci-mcasp 2b80000.mcasp: invalid tdm slots: 0 [ 1.064456] davinci-mcasp 2b80000.mcasp: IRQ common not found [ 1.070701] davinci-mcasp 2b90000.mcasp: invalid tdm slots: 0 [ 1.076597] davinci-mcasp 2b90000.mcasp: IRQ common not found [ 1.082841] davinci-mcasp 2ba0000.mcasp: invalid tdm slots: 0 [ 1.088734] davinci-mcasp 2ba0000.mcasp: IRQ common not found [ 1.094989] davinci-mcasp 2bb0000.mcasp: invalid tdm slots: 0 [ 1.100886] davinci-mcasp 2bb0000.mcasp: IRQ common not found [ 1.108273] tps659413_wd:tps659413_wd_probe: IN [ 1.112977] tps659413_wd:tps659413_wd_probe: OUT [ 1.117727] omap_i2c 40b00000.i2c: bus 1 rev0.12 at 400 kHz [ 1.123895] omap_i2c 40b10000.i2c: bus 6 rev0.12 at 100 kHz [ 1.130107] tps659413:tps659413_probe: IN [ 1.134284] tps659413:tps659413_probe: OUT [ 1.138566] tps659411:tps659411_probe: IN [ 1.142714] tps659411:tps659411_probe: OUT [ 1.146925] omap_i2c 42120000.i2c: bus 0 rev0.12 at 400 kHz [ 1.153170] pca953x 2-0020: supply vcc not found, using dummy regulator [ 1.159997] pca953x 2-0020: using no AI [ 1.185397] pca953x 2-0020: failed writing register [ 1.190438] pca953x: probe of 2-0020 failed with error -121 [ 1.196258] pca953x 2-0022: supply vcc not found, using dummy regulator [ 1.203062] pca953x 2-0022: using AI [ 1.206768] pca953x 2-0022: failed writing register [ 1.211791] pca953x: probe of 2-0022 failed with error -121 [ 1.217531] omap_i2c 2000000.i2c: bus 2 rev0.12 at 400 kHz [ 1.223580] omap_i2c 2020000.i2c: bus 4 rev0.12 at 100 kHz [ 1.229561] omap_i2c 2030000.i2c: bus 5 rev0.12 at 100 kHz [ 1.235504] omap_i2c 2040000.i2c: bus 7 rev0.12 at 100 kHz [ 1.241456] omap_i2c 2050000.i2c: bus 8 rev0.12 at 100 kHz [ 1.247888] ti-sci-intr bus@100000:bus@28380000:interrupt-controller2: Interrupt Router 137 domain created [ 1.257871] ti-sci-intr bus@100000:interrupt-controller0: Interrupt Router 131 domain created [ 1.266678] ti-sci-intr bus@100000:main-navss:interrupt-controller1: Interrupt Router 213 domain created [ 1.276544] ti-sci-inta 33d00000.interrupt-controller: Interrupt Aggregator domain 209 created [ 1.288947] cdns-sierra-phy: probe of 5000000.serdes failed with error -22 [ 1.306715] k3-ringacc 2b800000.ringacc: Ring Accelerator probed rings:286, gp-rings[96,20] sci-dev-id:235 [ 1.316602] k3-ringacc 2b800000.ringacc: dma-ring-reset-quirk: disabled [ 1.323360] k3-ringacc 2b800000.ringacc: RA Proxy rev. 66346100, num_proxies:64 [ 1.332457] k3-ringacc 3c000000.ringacc: Ring Accelerator probed rings:1024, gp-rings[440,150] sci-dev-id:211 [ 1.342616] k3-ringacc 3c000000.ringacc: dma-ring-reset-quirk: disabled [ 1.349379] k3-ringacc 3c000000.ringacc: RA Proxy rev. 66346100, num_proxies:64 [ 1.357369] 40a00000.serial: ttyS1 at MMIO 0x40a00000 (irq = 15, base_baud = 6000000) is a 8250 [ 1.366759] 2800000.serial: ttyS2 at MMIO 0x2800000 (irq = 26, base_baud = 3000000) is a 8250 [ 1.375504] printk: console [ttyS2] enabled [ 1.375504] printk: console [ttyS2] enabled [ 1.383941] printk: bootconsole [ns16550a0] disabled [ 1.383941] printk: bootconsole [ns16550a0] disabled [ 1.394383] 2810000.serial: ttyS3 at MMIO 0x2810000 (irq = 27, base_baud = 3000000) is a 8250 [ 1.403323] 2840000.serial: ttyS6 at MMIO 0x2840000 (irq = 28, base_baud = 3000000) is a 8250 [ 1.412659] cdns-ufshcd 4e84000.ufs: ufshcd_populate_vreg: Unable to find vdd-hba-supply regulator, assuming enabled [ 1.423167] cdns-ufshcd 4e84000.ufs: ufshcd_populate_vreg: Unable to find vcc-supply regulator, assuming enabled [ 1.433321] cdns-ufshcd 4e84000.ufs: ufshcd_populate_vreg: Unable to find vccq-supply regulator, assuming enabled [ 1.443559] cdns-ufshcd 4e84000.ufs: ufshcd_populate_vreg: Unable to find vccq2-supply regulator, assuming enabled [ 1.454736] scsi host0: ufshcd [ 1.463533] am65_cpsw_nuss_probe - node: ethernet-ports - ethernet-ports [ 1.463768] davinci_mdio 46000f00.mdio: Configuring MDIO in manual mode [ 1.517357] davinci_mdio 46000f00.mdio: davinci mdio revision 9.7, bus freq 1000000 [ 1.525000] davinci_mdio 46000f00.mdio: no live phy, scanning all [ 1.539742] am65-cpsw-nuss 46000000.ethernet: initializing am65 cpsw nuss version 0x6BA00101, cpsw version 0x6BA80100 Ports: 2 quirks:00000000 [ 1.552533] am65-cpsw-nuss 46000000.ethernet: /bus@100000/bus@28380000/ethernet@46000000/ethernet-ports/port@1 read phy-mode err -22 [ 1.564696] am65-cpsw-nuss: probe of 46000000.ethernet failed with error -22 [ 1.572191] am65_cpsw_nuss_probe - node: ethernet-ports - ethernet-ports [ 1.572446] davinci_mdio c000f00.mdio: Configuring MDIO in manual mode [ 1.625358] davinci_mdio c000f00.mdio: davinci mdio revision 9.7, bus freq 1000000 [ 1.633240] mdio_bus c000f00.mdio: MDIO device at address 0 is missing. [ 1.640442] dp83720_probe [ 1.864890] dp83720_probe [ 1.876677] cdns-ufshcd 4e84000.ufs: link startup failed 1 [ 1.882153] cdns-ufshcd 4e84000.ufs: UFS Host state=0 [ 1.887195] cdns-ufshcd 4e84000.ufs: outstanding reqs=0x0 tasks=0x0 [ 1.893447] cdns-ufshcd 4e84000.ufs: saved_err=0x0, saved_uic_err=0x0 [ 1.899878] cdns-ufshcd 4e84000.ufs: Device power mode=1, UIC link state=0 [ 1.906743] cdns-ufshcd 4e84000.ufs: PM in progress=0, sys. suspended=0 [ 1.913356] cdns-ufshcd 4e84000.ufs: Auto BKOPS=0, Host self-block=0 [ 1.919694] cdns-ufshcd 4e84000.ufs: Clk gate=1 [ 1.924212] cdns-ufshcd 4e84000.ufs: last_hibern8_exit_tstamp at 0 us, hibern8_exit_cnt=0 [ 1.932370] cdns-ufshcd 4e84000.ufs: last intr at 1786214 us, last intr status=0x404 [ 1.940095] cdns-ufshcd 4e84000.ufs: error handling flags=0x0, req. abort count=0 [ 1.947560] cdns-ufshcd 4e84000.ufs: hba->ufs_version=0x210, Host capabilities=0x1587031f, caps=0x0 [ 1.956584] cdns-ufshcd 4e84000.ufs: quirks=0x0, dev. quirks=0x0 [ 1.962574] cdns-ufshcd 4e84000.ufs: clk: core_clk, rate: 250000000 [ 1.968825] cdns-ufshcd 4e84000.ufs: clk: phy_clk, rate: 19200000 [ 1.974902] cdns-ufshcd 4e84000.ufs: clk: ref_clk, rate: 19200000 [ 1.980981] cdns-ufshcd 4e84000.ufs: ufshcd_print_pwr_info:[RX, TX]: gear=[0, 0], lane[0, 0], pwr[INVALID MODE, INVALID MODE], rate = 0 [ 1.993140] host_regs: 00000000: 1587031f 00000000 00000210 00000000 [ 1.999479] host_regs: 00000010: 00000000 00000000 00000000 00000000 [ 2.005816] host_regs: 00000020: 00000000 00000470 00000000 00000000 [ 2.012155] host_regs: 00000030: 00000008 00000001 00000000 00000000 [ 2.018491] host_regs: 00000040: 00000000 00000000 00000000 00000000 [ 2.024830] host_regs: 00000050: 00000000 00000000 00000000 00000000 [ 2.031167] host_regs: 00000060: 00000000 00000000 00000000 00000000 [ 2.037505] host_regs: 00000070: 00000000 00000000 00000000 00000000 [ 2.043843] host_regs: 00000080: 00000000 00000000 00000000 00000000 [ 2.050180] host_regs: 00000090: 00000000 00000000 00000000 00000000 [ 2.056518] cdns-ufshcd 4e84000.ufs: No record of pa_err [ 2.061817] cdns-ufshcd 4e84000.ufs: No record of dl_err [ 2.067115] cdns-ufshcd 4e84000.ufs: No record of nl_err [ 2.072413] cdns-ufshcd 4e84000.ufs: No record of tl_err [ 2.077710] cdns-ufshcd 4e84000.ufs: No record of dme_err [ 2.083093] cdns-ufshcd 4e84000.ufs: No record of auto_hibern8_err [ 2.089257] cdns-ufshcd 4e84000.ufs: No record of fatal_err [ 2.092634] dp83720_probe [ 2.094816] cdns-ufshcd 4e84000.ufs: link_startup_fail[0] = 0x1 at 1787327 us [ 2.094818] cdns-ufshcd 4e84000.ufs: No record of resume_fail [ 2.094820] cdns-ufshcd 4e84000.ufs: No record of suspend_fail [ 2.094822] cdns-ufshcd 4e84000.ufs: No record of dev_reset [ 2.094830] cdns-ufshcd 4e84000.ufs: No record of host_reset [ 2.127902] cdns-ufshcd 4e84000.ufs: No record of task_abort [ 2.319370] davinci_mdio: probe of c000f00.mdio failed with error -16 [ 2.325856] am65-cpsw-nuss c000000.ethernet: initializing am65 cpsw nuss version 0x6BA01901, cpsw version 0x6BA80101 Ports: 9 quirks:00000000 [ 2.338709] am65-cpsw-nuss c000000.ethernet: initialized cpsw ale version 1.4 [ 2.345828] am65-cpsw-nuss c000000.ethernet: ALE Table size 512 [ 2.352118] am65-cpsw-nuss c000000.ethernet: CPTS ver 0x4e8a010a, freq:200000000, add_val:4 pps:0 [ 2.363665] am65-cpts 310d0000.cpts: CPTS ver 0x4e8a010a, freq:200000000, add_val:4 pps:0 [ 2.473378] davinci-mcasp 2b00000.mcasp: invalid tdm slots: 0 [ 2.479132] davinci-mcasp 2b00000.mcasp: IRQ common not found [ 2.479195] mmc0: CQHCI version 5.10 [ 2.485462] mmc1: CQHCI version 5.10 [ 2.492664] davinci-mcasp 2b10000.mcasp: invalid tdm slots: 0 [ 2.498435] davinci-mcasp 2b10000.mcasp: IRQ common not found [ 2.504662] davinci-mcasp 2b20000.mcasp: invalid tdm slots: 0 [ 2.510422] davinci-mcasp 2b20000.mcasp: IRQ common not found [ 2.516623] davinci-mcasp 2b30000.mcasp: invalid tdm slots: 0 [ 2.522376] davinci-mcasp 2b30000.mcasp: IRQ common not found [ 2.528526] davinci-mcasp 2b40000.mcasp: invalid tdm slots: 0 [ 2.528732] mmc0: SDHCI controller on 4f80000.mmc [4f80000.mmc] using ADMA 64-bit [ 2.534281] davinci-mcasp 2b40000.mcasp: IRQ common not found [ 2.548051] davinci-mcasp 2b50000.mcasp: invalid tdm slots: 0 [ 2.553817] davinci-mcasp 2b50000.mcasp: IRQ common not found [ 2.560080] davinci-mcasp 2b60000.mcasp: invalid tdm slots: 0 [ 2.565883] davinci-mcasp 2b60000.mcasp: IRQ common not found [ 2.572138] davinci-mcasp 2b70000.mcasp: invalid tdm slots: 0 [ 2.577941] davinci-mcasp 2b70000.mcasp: IRQ common not found [ 2.584127] davinci-mcasp 2b80000.mcasp: invalid tdm slots: 0 [ 2.589929] davinci-mcasp 2b80000.mcasp: IRQ common not found [ 2.596128] davinci-mcasp 2b90000.mcasp: invalid tdm slots: 0 [ 2.601881] davinci-mcasp 2b90000.mcasp: IRQ common not found [ 2.608019] davinci-mcasp 2ba0000.mcasp: invalid tdm slots: 0 [ 2.613774] davinci-mcasp 2ba0000.mcasp: IRQ common not found [ 2.619898] davinci-mcasp 2bb0000.mcasp: invalid tdm slots: 0 [ 2.625649] davinci-mcasp 2bb0000.mcasp: IRQ common not found [ 2.638002] omap-mailbox 31f80000.mailbox: omap mailbox rev 0x66fc7100 [ 2.644929] omap-mailbox 31f81000.mailbox: omap mailbox rev 0x66fc7100 [ 2.651838] omap-mailbox 31f82000.mailbox: omap mailbox rev 0x66fc7100 [ 2.658672] omap-mailbox 31f83000.mailbox: omap mailbox rev 0x66fc7100 [ 2.665530] omap-mailbox 31f84000.mailbox: omap mailbox rev 0x66fc7100 [ 2.672830] ti-udma 285c0000.dma-controller: Channels: 26 (tchan: 13, rchan: 13, gp-rflow: 8) [ 2.683838] ti-udma 31150000.dma-controller: Channels: 122 (tchan: 61, rchan: 61, gp-rflow: 16) [ 2.697496] spi-nor spi7.0: unrecognized JEDEC id bytes: ff df ff ff ff ff [ 2.704368] spi-nor: probe of spi7.0 failed with error -2 [ 2.712220] davinci-mcasp 2b00000.mcasp: invalid tdm slots: 0 [ 2.717967] davinci-mcasp 2b00000.mcasp: IRQ common not found [ 2.730278] davinci-mcasp 2b10000.mcasp: invalid tdm slots: 0 [ 2.736087] davinci-mcasp 2b10000.mcasp: IRQ common not found [ 2.748463] davinci-mcasp 2b20000.mcasp: invalid tdm slots: 0 [ 2.754268] davinci-mcasp 2b20000.mcasp: IRQ common not found [ 2.766700] davinci-mcasp 2b30000.mcasp: invalid tdm slots: 0 [ 2.772444] davinci-mcasp 2b30000.mcasp: IRQ common not found [ 2.784706] davinci-mcasp 2b40000.mcasp: invalid tdm slots: 0 [ 2.790463] davinci-mcasp 2b40000.mcasp: IRQ common not found [ 2.802690] davinci-mcasp 2b50000.mcasp: invalid tdm slots: 0 [ 2.808503] davinci-mcasp 2b50000.mcasp: IRQ common not found [ 2.820791] davinci-mcasp 2b60000.mcasp: invalid tdm slots: 0 [ 2.826605] davinci-mcasp 2b60000.mcasp: IRQ common not found [ 2.839071] davinci-mcasp 2b70000.mcasp: invalid tdm slots: 0 [ 2.844869] davinci-mcasp 2b70000.mcasp: IRQ common not found [ 2.857182] davinci-mcasp 2b80000.mcasp: invalid tdm slots: 0 [ 2.862932] davinci-mcasp 2b80000.mcasp: IRQ common not found [ 2.875204] davinci-mcasp 2b90000.mcasp: invalid tdm slots: 0 [ 2.880958] davinci-mcasp 2b90000.mcasp: IRQ common not found [ 2.893168] davinci-mcasp 2ba0000.mcasp: invalid tdm slots: 0 [ 2.898920] davinci-mcasp 2ba0000.mcasp: IRQ common not found [ 2.911211] davinci-mcasp 2bb0000.mcasp: invalid tdm slots: 0 [ 2.916952] davinci-mcasp 2bb0000.mcasp: IRQ common not found [ 2.929409] debugfs: Directory 'pd:27' with parent 'pm_genpd' already present! [ 2.936696] debugfs: Directory 'pd:26' with parent 'pm_genpd' already present! [ 2.945078] debugfs: Directory 'pd:242' with parent 'pm_genpd' already present! [ 2.952392] debugfs: Directory 'pd:241' with parent 'pm_genpd' already present! [ 2.959702] debugfs: Directory 'pd:240' with parent 'pm_genpd' already present! [ 2.967014] debugfs: Directory 'pd:239' with parent 'pm_genpd' already present! [ 2.992201] ALSA device list: [ 2.995168] No soundcards found. [ 3.540240] mmc1: SDHCI controller on 4fb0000.mmc [4fb0000.mmc] using ADMA 64-bit [ 3.548331] Waiting for root device PARTUUID=c025843b-02... [ 3.582679] mmc1: new high speed SDHC card at address aaaa [ 3.588525] mmcblk1: mmc1:aaaa SB16G 14.8 GiB [ 3.596661] mmcblk1: p1 p2 [ 3.632438] EXT4-fs (mmcblk1p2): mounted filesystem with ordered data mode. Opts: (null) [ 3.640551] VFS: Mounted root (ext4 filesystem) on device 179:2. [ 3.650083] devtmpfs: mounted [ 3.653987] Freeing unused kernel memory: 1792K [ 3.658605] Run /sbin/init as init process [ 3.973104] systemd[1]: System time before build time, advancing clock. [ 4.013554] systemd[1]: systemd 244.5+ running in system mode. (+PAM -AUDIT -SELINUX +IMA -APPARMOR -SMACK +SYSVINIT +UTMP -LIBCRYPTSETUP -GCRYPT -GNUTLS +ACL +XZ -LZ4 -SECCOMP +BLKID -ELFUTILS +KMOD -IDN2 -IDN -PCRE2 default-hierarchy=hybrid) [ 4.035273] systemd[1]: Detected architecture arm64. Welcome to Arago 2021.09! [ 4.079746] systemd[1]: Set hostname to <j7-evm>. [ 4.319219] systemd[1]: Binding to IPv6 address not available since kernel does not support IPv6. [ 4.328116] systemd[1]: Binding to IPv6 address not available since kernel does not support IPv6. [ 4.354717] systemd[1]: /lib/systemd/system/docker.socket:6: ListenStream= references a path below legacy directory /var/run/, updating /var/run/docker.sock → /run/docker.sock; please update the unit file accordingly. [ 4.423159] random: systemd: uninitialized urandom read (16 bytes read) [ 4.429898] systemd[1]: system-getty.slice: unit configures an IP firewall, but the local system does not support BPF/cgroup firewalling. [ 4.442235] systemd[1]: (This warning is only shown for the first unit using IP firewalling.) [ 4.452272] systemd[1]: Created slice system-getty.slice. [ OK ] Created slice system-getty.slice. [ 4.473439] random: systemd: uninitialized urandom read (16 bytes read) [ 4.480806] systemd[1]: Created slice system-serial\x2dgetty.slice. [ OK ] Created slice system-serial\x2dgetty.slice. [ 4.501435] random: systemd: uninitialized urandom read (16 bytes read) [ 4.508654] systemd[1]: Created slice User and Session Slice. [ OK ] Created slice User and Session Slice. [ 4.529566] systemd[1]: Started Dispatch Password Requests to Console Directory Watch. [ OK ] Started Dispatch Password …ts to Console Directory Watch. [ 4.553481] systemd[1]: Started Forward Password Requests to Wall Directory Watch. [ OK ] Started Forward Password R…uests to Wall Directory Watch. [ 4.577478] systemd[1]: Reached target Paths. [ OK ] Reached target Paths. [ 4.593417] systemd[1]: Reached target Remote File Systems. [ OK ] Reached target Remote File Systems. [ 4.613410] systemd[1]: Reached target Slices. [ OK ] Reached target Slices. [ 4.629415] systemd[1]: Reached target Swap. [ OK ] Reached target Swap. [ 4.654684] systemd[1]: Listening on RPCbind Server Activation Socket. [ OK ] Listening on RPCbind Server Activation Socket. [ 4.677452] systemd[1]: Reached target RPC Port Mapper. [ OK ] Reached target RPC Port Mapper. [ 4.701269] systemd[1]: Listening on Process Core Dump Socket. [ OK ] Listening on Process Core Dump Socket. [ 4.721561] systemd[1]: Listening on initctl Compatibility Named Pipe. [ OK ] Listening on initctl Compatibility Named Pipe. [ 4.755331] systemd[1]: Condition check resulted in Journal Audit Socket being skipped. [ 4.763692] systemd[1]: Listening on Journal Socket (/dev/log). [ OK ] Listening on Journal Socket (/dev/log). [ 4.785660] systemd[1]: Listening on Journal Socket. [ OK ] Listening on Journal Socket. [ 4.801722] systemd[1]: Listening on Network Service Netlink Socket. [ OK ] Listening on Network Service Netlink Socket. [ 4.825613] systemd[1]: Listening on udev Control Socket. [ OK ] Listening on udev Control Socket. [ 4.845546] systemd[1]: Listening on udev Kernel Socket. [ OK ] Listening on udev Kernel Socket. [ 4.867776] systemd[1]: Mounting Huge Pages File System... Mounting Huge Pages File System... [ 4.887738] systemd[1]: Mounting POSIX Message Queue File System... Mounting POSIX Message Queue File System... [ 4.911679] systemd[1]: Mounting Kernel Debug File System... Mounting Kernel Debug File System... [ 4.933893] systemd[1]: Mounting Temporary Directory (/tmp)... Mounting Temporary Directory (/tmp)... [ 4.949591] systemd[1]: Condition check resulted in Create list of static device nodes for the current kernel being skipped. [ 4.963148] systemd[1]: Starting Start psplash boot splash screen... Starting Start psplash boot splash screen... [ 4.987755] systemd[1]: Starting RPC Bind... Starting RPC Bind... [ 5.005582] systemd[1]: Condition check resulted in File System Check on Root Device being skipped. [ 5.017782] systemd[1]: Starting Journal Service... Starting Journal Service... [ 5.050051] systemd[1]: Starting Load Kernel Modules... Starting Load Kernel Modules... [ 5.067944] systemd[1]: Starting Remount Root and Kernel File Systems... Starting Remount Root and Kernel File Systems... [ 5.087172] EXT4-fs (mmcblk1p2): re-mounted. Opts: (null) [ 5.096282] systemd[1]: Starting udev Coldplug all Devices... Starting udev Coldplug all Devices... [ 5.116392] systemd[1]: Started RPC Bind. [ OK ] Started RPC Bind. [ 5.129805] systemd[1]: Started Journal Service. [ OK ] Started Journal Service. [ OK ] Mounted Huge Pages File System. [ OK ] Mounted POSIX Message Queue File System. [ OK ] Mounted Kernel Debug File System. [ OK ] Mounted Temporary Directory (/tmp). [FAILED] Failed to start Start psplash boot splash screen. See 'systemctl status psplash-start.service' for details. [DEPEND] Dependency failed for Star…progress communication helper. [FAILED] Failed to start Load Kernel Modules. See 'systemctl status systemd-modules-load.service' for details. [ OK ] Started Remount Root and Kernel File Systems. Mounting Kernel Configuration File System... Starting Flush Journal to Persistent Storage... [ 5.348545] systemd-journald[239]: Received client request to flush runtime journal. Starting Apply Kernel Variables... Starting Create Static Device Nodes in /dev... [ OK ] Mounted Kernel Configuration File System. [ OK ] Started Flush Journal to Persistent Storage. [ OK ] Started Apply Kernel Variables. [ OK ] Started Create Static Device Nodes in /dev. [ OK ] Started udev Coldplug all Devices. [ 5.477977] random: systemd: uninitialized urandom read (16 bytes read) [ OK ] Reached target Local File Systems (Pre). [ 5.501477] random: systemd: uninitialized urandom read (16 bytes read) Mounting /media/ram... [ 5.513663] random: systemd-journal: uninitialized urandom read (16 bytes read) Mounting /var/volatile... Starting udev Wait for Complete Device Initialization... Starting udev Kernel Device Manager... [ OK ] Mounted /media/ram. [ OK ] Mounted /var/volatile. Starting Load/Save Random Seed... [ OK ] Reached target Local File Systems. Starting Create Volatile Files and Directories... [ OK ] Started Create Volatile Files and Directories. Starting Network Time Synchronization... Starting Update UTMP about System Boot/Shutdown... [ OK ] Started udev Kernel Device Manager. [ OK ] Started Update UTMP about System Boot/Shutdown. [ OK ] Started Network Time Synchronization. [ OK ] Reached target System Time Set. [ OK ] Reached target System Time Synchronized. [ 6.776454] random: systemd: uninitialized urandom read (16 bytes read) [ 6.785611] random: systemd: uninitialized urandom read (16 bytes read) [ 7.590029] random: systemd: uninitialized urandom read (16 bytes read) [ 7.685393] random: crng init done [ 7.688797] random: 85 urandom warning(s) missed due to ratelimiting [ OK ] Started Load/Save Random Seed. [ OK ] Created slice system-systemd\x2dfsck.slice. [ OK ] Found device /dev/mmcblk1p1. Starting File System Check on /dev/mmcblk1p1... [ OK ] Started udev Wait for Complete Device Initialization. [ OK ] Started Hardware RNG Entropy Gatherer Daemon. [ OK ] Reached target System Initialization. [ OK ] Started Daily rotation of log files. [ OK ] Started Daily Cleanup of Temporary Directories. [ OK ] Reached target Timers. [ OK ] Listening on Avahi mDNS/DNS-SD Stack Activation Socket. [ OK ] Listening on D-Bus System Message Bus Socket. Starting Docker Socket for the API. [ OK ] Listening on dropbear.socket. Starting Reboot and dump vmcore via kexec... [ OK ] Listening on Docker Socket for the API. [ OK ] Reached target Sockets. [ OK ] Reached target Basic System. [ OK ] Started Job spooling tools. [ OK ] Started Periodic Command Scheduler. [ OK ] Started D-Bus System Message Bus. Starting Print notice about GPLv3 packages... Starting set host name as per compatible name... Starting IPv6 Packet Filtering Framework... Starting IPv4 Packet Filtering Framework... [ OK ] Started irqbalance daemon. Starting Telephony service... Starting Update pmic regis…fety feature on power rails... Starting rc.pvr.service... Starting startwlanap... Starting startwlansta... Starting Login Service... [ OK ] Started TEE Supplicant. Starting Update weston ini… based on the platform name... [ OK ] Started Reboot and dump vmcore via kexec. [ OK ] Started File System Check on /dev/mmcblk1p1. [ OK ] Started set host name as per compatible name. [ OK ] Started IPv6 Packet Filtering Framework. [ OK ] Started IPv4 Packet Filtering Framework. [ OK ] Started Update pmic regist…safety feature on power rails. [ OK ] Started rc.pvr.service. [ OK ] Started startwlanap. [ OK ] Started startwlansta. [ OK ] Started Update weston ini …ge based on the platform name. [ OK ] Started Telephony service. [ OK ] Reached target Network (Pre). Mounting /run/media/mmcblk1p1... Starting Network Service... Starting weston.service... [ OK ] Started Login Service. [ OK ] Started Network Service. Starting Wait for Network to be Configured... Starting Network Name Resolution... [ OK ] Mounted /run/media/mmcblk1p1. [ 9.233622] am65-cpsw-nuss c000000.ethernet: down msc_sl e0000000 tmo 0 [ 9.272615] am65-cpsw-nuss c000000.ethernet: set new flow-id-base 140 [ 9.308449] am65-cpsw-nuss c000000.ethernet: down msc_sl e0000000 tmo 0 [ 9.333869] am65-cpsw-nuss c000000.ethernet: set new flow-id-base 140 [ 9.361035] am65-cpsw-nuss c000000.ethernet: down msc_sl e0000000 tmo 0 [ 9.378261] am65-cpsw-nuss c000000.ethernet: set new flow-id-base 140 [ 9.397543] am65-cpsw-nuss c000000.ethernet: down msc_sl e0000000 tmo 0 [ 9.409749] am65-cpsw-nuss c000000.ethernet: set new flow-id-base 140 [ 9.432040] am65-cpsw-nuss c000000.ethernet: down msc_sl e0000000 tmo 0 [ 9.445034] am65-cpsw-nuss c000000.ethernet: set new flow-id-base 140 [ OK ] Started Network Name Resolution. [ OK ] Reached target Network. [ OK ] Reached target Host and Network Name Lookups. Starting Avahi mDNS/DNS-SD Stack... Starting Enable and configure wl18xx bluetooth stack... [ OK ] Started NFS status monitor for NFSv2/3 locking.. Starting Simple Network Ma…ent Protocol (SNMP) Daemon.... Starting Permit User Sessions... [ OK ] Started Permit User Sessions. [ OK ] Started Getty on tty1. [ OK ] Started Serial Getty on ttyS2. [ OK ] Started Serial Getty on ttyS3. [ OK ] Reached target Login Prompts. Starting Synchronize System and HW clocks... [ OK ] Started Enable and configure wl18xx bluetooth stack. [FAILED] Failed to start Synchronize System and HW clocks. See 'systemctl status sync-clocks.service' for details. [ OK ] Started Avahi mDNS/DNS-SD Stack. [ OK ] Started Simple Network Man…ement Protocol (SNMP) Daemon.. *************************************************************** *************************************************************** NOTICE: This file system contains the following GPLv3 packages: autoconf bash-dev bash bc binutils cifs-utils coreutils-stdbuf coreutils cpio cpp-symlinks cpp dosfstools elfutils g++-symlinks g++ gawk gcc-symlinks gcc gdb gdbserver gettext glmark2 gstreamer1.0-libav-dev gstreamer1.0-libav gzip less libasm1 libbfd libdw1 libelf1 libgdbm-compat4 libgdbm-dev libgdbm6 libgettextlib libgettextsrc libgmp-dev libgmp10 libgmpxx4 libidn2-0 libidn2-dev libmpc3 libmpfr6 libreadline-dev libreadline8 libunistring-dev libunistring2 m4-dev m4 make nettle-dev nettle parted python3-rfc3987 python3-strict-rfc3339 tar which zeromq If you do not wish to distribute GPLv3 components please remove the above packages prior to distribution. This can be done using the opkg remove command. i.e.: opkg remove <package> Where <package> is the name printed in the list above NOTE: If the package is a dependency of another package you will be notified of the dependent packages. You should use the --force-removal-of-dependent-packages option to also remove the dependent packages as well *************************************************************** *************************************************************** [ OK ] Started Print notice about GPLv3 packages. [ OK ] Started weston.service. Starting DEMO... Starting telnetd.service... [ OK ] Started DEMO. [ OK ] Started telnetd.service. _____ _____ _ _ | _ |___ ___ ___ ___ | _ |___ ___ |_|___ ___| |_ | | _| .'| . | . | | __| _| . | | | -_| _| _| |__|__|_| |__,|_ |___| |__| |_| |___|_| |___|___|_| |___| |___| Arago Project j7-evm ttyS2 Arago 2021.09 j7-evm ttyS2 j7-evm login: root root@j7-evm:~# lsmod Module Size Used by root@j7-evm:~# ls /dev/ 31010000.pat dma_heap i2c-5 loop3 null ptyp5 ram0 ram5 stdout tty12 tty22 tty32 tty42 tty52 tty62 ttyS6 ttyp7 urandom vcsa3 vfio 31011000.pat fd i2c-6 loop4 port ptyp6 ram1 ram6 tee0 tty13 tty23 tty33 tty43 tty53 tty63 ttyS7 ttyp8 vcs vcsa4 zero 31012000.pat full i2c-7 loop5 ptmx ptyp7 ram10 ram7 teepriv0 tty14 tty24 tty34 tty44 tty54 tty7 ttyS8 ttyp9 vcs1 vcsa5 31013000.pat gpiochip0 i2c-8 loop6 ptp0 ptyp8 ram11 ram8 tps659411 tty15 tty25 tty35 tty45 tty55 tty8 ttyS9 ttypa vcs2 vcsa6 31014000.pat gpiochip1 initctl loop7 ptp1 ptyp9 ram12 ram9 tps659413 tty16 tty26 tty36 tty46 tty56 tty9 ttyp0 ttypb vcs3 vcsu autofs gpiochip2 kmsg mem pts ptypa ram13 random tps659413_wd tty17 tty27 tty37 tty47 tty57 ttyS0 ttyp1 ttypc vcs4 vcsu1 block hugepages log mmcblk1 ptyp0 ptypb ram14 shm tty tty18 tty28 tty38 tty48 tty58 ttyS1 ttyp2 ttypd vcs5 vcsu2 char i2c-0 loop-control mmcblk1p1 ptyp1 ptypc ram15 snapshot tty0 tty19 tty29 tty39 tty49 tty59 ttyS2 ttyp3 ttype vcs6 vcsu3 console i2c-1 loop0 mmcblk1p2 ptyp2 ptypd ram2 snd tty1 tty2 tty3 tty4 tty5 tty6 ttyS3 ttyp4 ttypf vcsa vcsu4 disk i2c-2 loop1 mqueue ptyp3 ptype ram3 stderr tty10 tty20 tty30 tty40 tty50 tty60 ttyS4 ttyp5 ubi_ctrl vcsa1 vcsu5 dma-buf-phys i2c-4 loop2 net ptyp4 ptypf ram4 stdin tty11 tty21 tty31 tty41 tty51 tty61 ttyS5 ttyp6 udev_network_queue vcsa2 vcsu6 root@j7-evm:~#

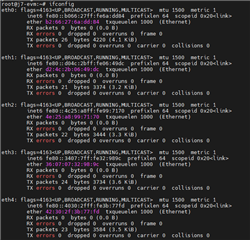

我可以使用 ifconfig -a 查看存在的所有5个接口

但当我尝试使用 ifconfig 打开接口 并集。 它显示如下所示的错误:

root@j7-evm:~# ifconfig eth0 up [ 325.312339] am65-cpsw-nuss c000000.ethernet: down msc_sl f0000000 tmo 0 [ 325.321145] am65-cpsw-nuss c000000.ethernet: set new flow-id-base 140 SIOCSIFFLAGS: No such device

您能帮我检查一下、告诉我哪里出了问题吗?

谢谢!

此致

LOC.Ta