工具与软件:

尊敬的 TI 专家:

客户正在使用 TDA4AP SDK9.2。

它们遵循以下常见问题解答、以启用 R5f 缓存 ECC。

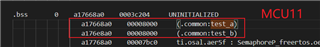

但是、正如您可以从下图中看到的、常见问题解答中使用的地址适用于 MCU1-0。 在寄存器手册中、我们只能找到 MCU1-0和 MCU1-1的情况。 客户拥有双安全通道设计、MCU1-1和 MCU4-0都是其安全通道、需要启用高速缓存 ECC。 他们在寄存器手册中找不到与 MCU4-0相对应的地址。

您可以帮助客户找到 MCU4-0的寄存器地址吗?

非常感谢!

Kevin