你好

我想配置 ADC32RF80以将其小数减至16。 在以下配置中,我已成功使用 ADC32RF80将小数减至4和8:

小数4:

LMFS = 8422

PLL 模式= 20X

JESD 模式0,1,2 = 1,0,0

比率= 2.5

小数位数为8:

LMFS = 4421

PLL 模式= 20X

JESD 模式0,1,2 = 1,0,0

比率= 2.5

我正在尝试配置 ADC32RF80以将其小数减至16,以保持比率=2.5。 如果通道速率与4,8和16的位数相同,这将简化我们的固件。 为此,我尝试按如下方式配置 ADC32RF80:

小数位数为16:

LMFS = 2441

PLL 模式= 40X

JESD 模式0,1,2 = 2,0,0

比率= 2.5

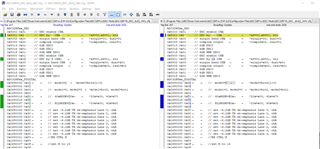

以下是与 JESD 配置和 DDC 配置相关的寄存器写入。 注释了用4和8进行小数位数的选项。 据我所知,在更改小数位率时,所有其他寄存器写入保持不变:

#define ADC_DEC_CHAN_A_DDC_EN 0x5000

#define ADC_DEC_CHAN_A_DECIM_factor 0x5001

#define ADC_DEC_CHAN_A_DUAL_BAND EN 0x5002

#define ADC_DEC_CHAN_A_REAL_OUT EN 0x5005

#define ADC_DEC_CHAN_A_DDC_MUX 0x5006

#define ADC_DEC_CHAN_A_DDC0_NCO1_LSB 0x5007

#define ADC_DEC_CHAN_A_DDC0_NCO1_MSB 0x5008

#define ADC_DEC_CHAN_A_DDC0_NCO2_LSB 0x5009

#define ADC_DEC_CHAN_A_DDC0_NCO2_MSB 0x500A

#define ADC_DEC_CHAN_A_DDCO_NCO3_LSB 0x500B

#define ADC_DEC_CHAN_A_DDC0_NCO3_MSB 0x500C

#define ADC_DEC_CHAN_A_DDC1_NCO4_LSB 0x500D

#define ADC_DEC_CHAN_A_DDC1_NCO4_MSB 0x500E

#define ADC_DEC_CHAN_A_NCO_SEL_PIN 0x500F

#define ADC_DEC_CHAN_A_NCO_SEL 0x5010

#define ADC_DEC_CHAN_A_LMFC_RESET_MODE 0x5011

#define ADC_DEC_CHAN_A_DDC0_6DB_Gain 0x5014

#define ADC_DEC_CHAN_A_DDC1_6DB_Gain 0x5016

#define ADC_DEC_CHAN_A_DDC_DET_LAT 0x501E

#define ADC_DEC_CHAN_A_WBF_6DB_Gain 0x501F

#define ADC_DEC_CHAN_B_DDC_EN 0x5800

#define ADC_DEC_CHAN_B_DECIM_factor 0x5801

#define ADC_DEC_CHAN_B_DUAL_BAND EN 0x5802

#define ADC_DEC_CHAN_B_REAL_OUT EN 0x5805

#define ADC_DEC_CHAN_B_DDC_MUX 0x5806

#define ADC_DEC_CHAN_B_DDC0_NCO1_LSB 0x5807

#define ADC_DEC_CHAN_B_DDC0_NCO1_MSB 0x5808

#define ADC_DEC_CHAN_B_DDC0_NCO2_LSB 0x5809

#define ADC_DEC_CHAN_B_DDC0_NCO2_MSB 0x580A

#define ADC_DEC_CHAN_B_DDCO_NCO3_LSB 0x580B

#define ADC_DEC_CHAN_B_DDC0_NCO3_MSB 0x580C

#define ADC_DEC_CHAN_B_DDC1_NCO4_LSB 0x580D

#define ADC_DEC_CHAN_B_DDC1_NCO4_MSB 0x580E

#define ADC_DEC_CHAN_B_NCO_SEL_PIN 0x580F

#define ADC_DEC_CHAN_B_NCO_SEL 0x5810

#define ADC_DEC_CHAN_B_LMFC_RESET_MODE 0x5811

#define ADC_DEC_CHAN_B_DDC0_6DB_Gain 0x5814

#define ADC_DEC_CHAN_B_DDC1_6DB_Gain 0x5816

#define ADC_DEC_CHAN_B_DDC_DET_LAT 0x581E

#define ADC_DEC_CHAN_B_WBF_6DB_Gain 0x581F

#define ADC_DIGITAL Bank_PAGE_SEL_MSB 0x4004

#define ADC_DIGITAL Bank_PAGE_SEL_MID 0x4003

#define ADC_DIGITAL Bank_PAGE_SEL_LSB 0x4002

#define ADC_MAIN_DIG_PAGE_NQ_Zone_EN 0x60A2

#define ADC_MAIN_DIG_DIG_RESET 0x6000

#define ADC_JESD_CHAN_A_CTRL_K 0x7001

#define ADC_JESD_CHA_SYNC_REG 0x7002

#define ADC_JESD_CHA_LINK_LAYER_TESTMODE 0x7003

#define ADC_JESD_CHAN_A_REL_ILA_SEQ 0x7004

#define ADC_JESD_CHAN_a_ching_EN 0x7006

#define ADC_JESD_CHAN_A_Frames_Per 多帧0x7007

#define ADC_JESD_CHA_40X_MODE 0x7016

#define ADC_JESD_CHA_LANE0_POL 0x7017

#define ADC_JESD_CHAN_A_SEL_EMP_LAN_0 0x7032

#define ADC_JESD_CHAN_A_SEL_EMP_LANK_1 0x7033

#define ADC_JESD_CHAN_A_SEL_EMP_LAN_2 0x7034

#define ADC_JESD_CHAN_A_SEL_EMP_LAN_3 0x7035

#define ADC_JESD_CHA_CMOS_SYNCB 0x7036

#define ADC_JESD_CHA_PLL_MODE 0x7037

#define ADC_JESD_CHA_EN_CMOS_SYNCB 0x703C

#define ADC_JESD_CHA_B_CTRL_K 0x6001

#define ADC_JESD_CHAN_B_SYNC_REG 0x6002

#define ADC_JESD_CHAN_B_LINK_LAYER_TESTMODE 0x6003

#define ADC_JESD_CHA_B_REL_ILA_SEQ 0x6004

#define ADC_JESD_CHAN_B_ch扰 流_EN 0x6006

#define ADC_JESD_CHAN_B_fr帧 按多帧0x6007

#define ADC_JESD_CHA_B_40X_MODE 0x6016

#define ADC_JESD_CHAN_B_LANE0_POL 0x6017

#define ADC_JESD_CHA_B_SEL_EMP_LAN_0 0x6032

#define ADC_JESD_CHA_B_SEL_EMP_LANK_1 0x6033

#define ADC_JESD_CHA_B_SEL_EMP_LAN_2 0x6034

#define ADC_JESD_CHA_B_SEL_EMP_LAN_3 0x6035

#define ADC_JESD_CHAN_B_CMOS_SYNCB 0x6036

#define ADC_JESD_CHAN_B_PLL_MODE 0x6037

#define ADC_JESD_CHAN_B_EN_CMOS_SYNCB 0x603C

//数字银行

// JESD 数字主页

ADC_DIGITAL _Bank_PAGE_SEL_LSB = 0x00

ADC_DIGITAL _BANK_PAGE_SEL_MID=0x00

ADC_DIGITAL Bank_PAGE_SEL_MSB=0x69

//ADC_JESD_CHA_SYNC_REG=0x01 // DEC 4/8

ADC_JESD_CHA_SYNC_REG=0x02 // DEC 16

//ADC_JESD_CHA_B_SYNC_REG=0x01 // DEC 4/8

ADC_JESD_CHA_B_SYNC_REG=0x02 // DEC 16

//ADC_JESD_CHA_PLL_MODE=0x00 // DEC 4/8

//ADC_JESD_CHA_B_PLL_MODE=0x00 // DEC 4/8

ADC_JESD_CHA_PLL_MODE=0x02 // DEC 16.

ADC_JESD_CHA_B_PLL_MODE=0x02 // DEC 16.

ADC_JESD_CHA_40X_MODE=0x70 // DEC 16

ADC_JESD_CHA_B_40X_MODE=0x70 // DEC 16

ADC_JESD_CHA_CTRL_K=0x80

ADC_JESD_CHA_B_CTRL_K=0x80

ADC_JESD_CHAN_A_Frames_Per Multiframe = 0x1F

ADC_JESD_CHAN_B_frame_per 多帧=0x1F

ADC_JESD_CHAN_A_LINK_LAYER_TESTMODE =0x00

ADC_JESD_CHAN_B_LINK_LAYER_TESTMODE=0x00

ADC_JESD_CHA_SEL_EMP_EMP_LAND_0=0x3C

ADC_JESD_CHA_B_SEL_EMP_LAN_0=0x3C

ADC_JESD_CHA_SEL_EMP_EMP_LANK_1=0x3C

ADC_JESD_CHA_B_SEL_EMP_LAN_1=0x3C

ADC_JESD_CHA_SEL_EMP_EMP_LANK_2=0x3C

ADC_JESD_CHA_B_SEL_EMP_LAN_2=0x3C

ADC_JESD_CHA_SEL_EMP_EMP_LAN_3=0x3C

ADC_JESD_CHA_B_SEL_EMP_LAN_3=0x3C

ADC_JESD_CHA_CMOS_SYNC=0x40 //设置为单端同步

ADC_JESD_CHA_EN_CMOS_SYNC=0x01 //设置为单端同步

//数字银行

//直接寻址

// DDC 页面

ADC_DEC_CHAN_A_DDC_EN=0x01

//ADC_DEC_CHA_DECIM_factor=0x00 // DEC 4.

//ADC_DEC_CHA_DECIM_factor=0x02 // DEC 8.

ADC_DEC_CHA_DECIM_factor=0x07 // DEC 16.

ADC_DEC_CHAN_A_DULE_BAD_EN=0x00 //单频段

ADC_DEC_CHAN_A_REAL_OUT EN=0x00

ADC_DEC_CHAN_A_DDC_MUX=0x00

ADC_DEC_CHAN_A_DDC0_NCO1_LSB = 0x55 // NCO1 = 21845 = 1GHz CF

ADC_DEC_CHAN_A_DDC0_NCO1_MSB=0x55

ADC_DEC_CHAN_A_DDC0_NCO2_LSB = 0x00

ADC_DEC_CHAN_A_DDC0_NCO2_MSB=0x00

ADC_DEC_CHAN_A_DDCO_NCO3_LSB = 0x00

ADC_DEC_CHA_DDC0_NCO3_MSB=0x00

ADC_DEC_CHA_DDC1_NCO4_LSB = 0x00

ADC_DEC_CHAN_A_DDC1_NCO4_MSB=0x00

ADC_DEC_CHAN_A_WBF_6dB_Gain =0x01 //使用 WB DDC 添加6dB 增益

ADC_DEC_CHAN_A_DDC0_6DB_GIN=0x01

ADC_DEC_CHAN_A_DDC1_6DB_GIN=0x01

ADC_DEC_CHAN_A_NCO_SEL_PIN=0x00 //通过 SPI 选择 NCO

ADC_DEC_CHAN_A_NCO_SEL=0x00 // NCO 1已选定

ADC_DEC_CHAN_A_LMFC_RESET_MODE=0x00 //所有 DDP 和 NCOS 都将重置为每个 LMFC

//ADC_DEC_CHAN_A_DDC_DET_LAT=0x50 //确保 DEC x 4,DEC x 8的确定性延迟

ADC_DEC_CHAN_A_DDC_DET_LAT=0x20 //确保 DEC 的确定性延迟为16

ADC_DEC_CHAN_B_DDC_EN=0x01

//ADC_DEC_CHAN_B_DECIM_factor=0x00 // DEC 4.

//ADC_DEC_CHAN_B_DECIM_factor=0x02 // DEC 8.

ADC_DEC_CHA_B_DECIM_factor=0x07 // DEC 16

ADC_DEC_CHAN_B_双频带_EN=0x00 //单频带

ADC_DEC_CHAN_B_REAL_OUT EN=0x00

ADC_DEC_CHAN_B_DDC_MUX=0x00

ADC_DEC_CHAN_B_DDC0_NCO1_LSB = 0x55 // NCO1 = 21845 = 1GHZ CF

ADC_DEC_CHAN_B_DDC0_NCO1_MSB=0x55

ADC_DEC_CHAN_B_DDC0_NCO2_LSB=0x00

ADC_DEC_CHAN_B_DDC0_NCO2_MSB=0x00

ADC_DEC_CHAN_B_DDCO_NCO3_LSB=0x00

ADC_DEC_CHAN_B_DDC0_NCO3_MSB=0x00

ADC_DEC_CHAN_B_DDC1_NCO4_LSB=0x00

ADC_DEC_CHAN_B_DDC1_NCO4_MSB=0x00

ADC_DEC_CHAN_B_DDC0_6DB_Gain = 0x01

ADC_DEC_CHAN_B_DDC1_6dB_Gain = 0x01

ADC_DEC_CHAN_B_B_WBF_6DB_Gain =0x01 //使用 WB DDC 添加6dB 增益

ADC_DEC_CHAN_B_NCO_SEL_PIN=0x00 //通过 SPI 选择 NCO

ADC_DEC_CHAN_B_NCO_SEL=0x00 // NCO 1已选定

ADC_DEC_CHAN_B_LMFC_RESET_MODE=0x00 //所有 DDP 和 NCOS 都将重置为每个 LMFC

//ADC_DEC_CHAN_B_DDC_DET_LAT=0x50 //确保 DEC x 4,DEC x 8的确定性延迟

ADC_DEC_CHAN_B_DDC_DET_LAT=0x20 //确保 DEC 的确定性延迟为16

是否有一些我没有正确设置以将小数位数减至16? 或者,我是否按错误的顺序设置了一些小数位数16? PLL 模式已更改为40X 这一事实是否对计时等有任何其他影响,我需要考虑这些影响?

谢谢你。