主题中讨论的其他器件:AFE7769EVM、 AFE7769

您好!

我正在尝试通过 JESD204C 将 ZC102 EVM 板与 AFE7769EVM-3p5模块通信。 我使用的是 Xilinx JESD204C 和 JES204 PHY IP。 在 Vivado、我将通道速率设置为8.11008、并将 REFCLK 设置为122.88Mhz。 我正在通过 Latte 软件配置 AFE7769EVM 板。 python 脚本的主要参数如下所示。

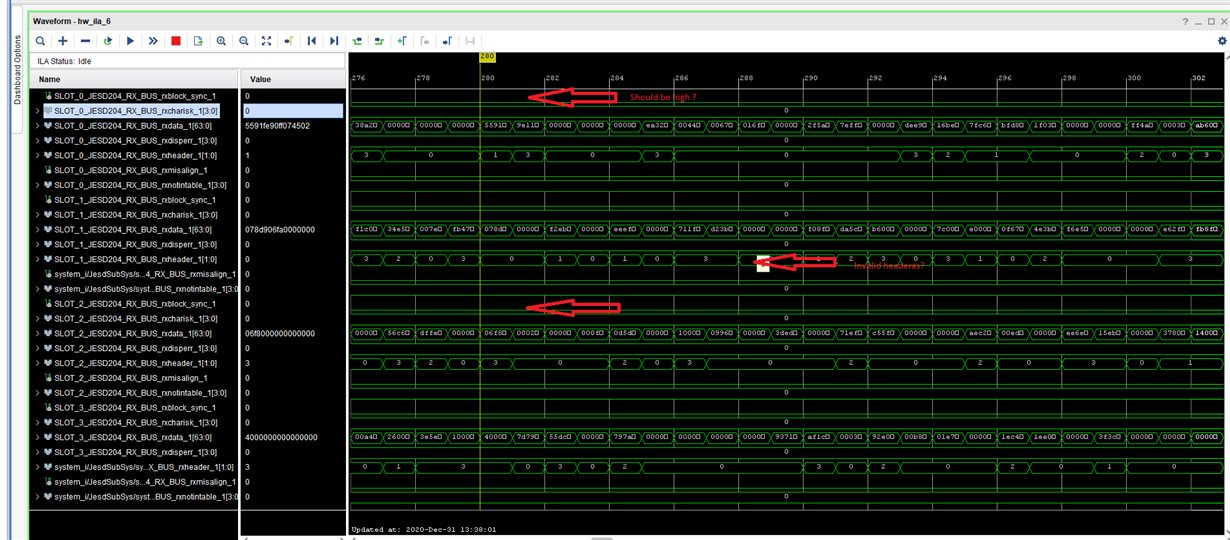

当我使用 JESD204PHY IP 的输出端配置 FPGA 和 AFE7769 EVM 时,我观察到无效的2位同步报头(如0011),并且无法建立同步。 (在收发器的输出端)

除了这个眼图外、通道也接近预期(非常糟糕)、但我看不到任何原因、因为两个卡都是 EVM、应该正确设计。

您是否知道问题可能是什么? 您是否有 适用于 ZCU 102板的 JESD204C 示例设计? (您之前向我发送了 JESD204B 的示例设计、 它正在工作。 因此我似乎也需要 JESD204C:)

我认为我的 AFE 配置文件可能不正确。 那么、您是否有适用于 JESD204C 的 Latte python 配置文件?

提前感谢。

TAMER。

sysParams.FRef = 491.52

sysParams.fs = 2949.12

sysParams.pllMuxModes = 0

0:4T4R 模式、PLL0作为主器件。 所有 LOS 的 PLL 0。

1:4T4R 模式、PLL2作为主器件。 所有 LOS 的 PLL 2。

#2:4T4R FDD 模式。 用于 TX 的 PLL0和用于 RX 的 PLL2。

3:2*2T2R FDD 模式:PLL0 AB-TX;PLL3 AB-RX;PLL2 CD TX;PLL4 CD RX

4:2T2R FDD - TDD 模式:PLL0 AB-TX;PLL3-AB-RX;PLL2 CD

sysParams.pllLo =[3500.01、sysParams.fs、3501.06、1800.24、3400.0] PLL 的 PLL 频率[0、1、2、3、4]

sysParams.setTxLoFbNcoFreqForTxCalib =正确

##在下面的参数中、首先在数组中用于第一个2T2R1F 和第二个2T2R1F。

# JESD 和串行器/解串器参数

sysParams.useSpiSysref =错误

sysParams.LMFSHdRx =[28810"、"28810"]

sysParams.LMFSHdFb =["12820"、"12820"]

sysParams.LMFSHdTx =["48410"、"48410"]

sysParams.systemMode =[1、1]# 0 -相同、1-FDD、2-TDD

sysParams.dedicatedLaneMode =[1、1]

sysParams.jesdProtocol = 2#0#1#0 #-0:B;1:H;2:C

sysParams.serdesFirmware =正确

sysParams.jesdTxLaneMux =[1、0、2、3、4、5、6、7]#[0、1、2、3、4、5、6、7]# RX1、RX2、RX3、RX4、FB1、FB2

sysParams.jesdRxLaneMux =[0、1、2、3、4、5、6、7]#[0、1、2、3、4、5、6、7]

sysParams.jesdRxRbd =[15、15]

sysParams.jesdScr =[错误、错误]

sysParams.serdesTxLanePolarity =[假、假、假、假、真、真、真]

sysParams.serdesRxLanePolarity =[假、假、假、假、真、真、真]

sysParams.jesdK =[1、1]

sysParams.syncLoopBack =真

sysParams.jesdLoopbackEn = 1.

sysParams.jesdTxRxABSyncMux = 0

sysParams.jesdTxRxCDSyncMux = 0

sysParams.jesdTxFBABSyncMux = 0

sysParams.jesdTxFBCDSyncMux = 0

sysParams.jesdRxABSyncMux = 0

sysParams.jesdRxCDSyncMux = 0

#sysParams.jesdABLvdsSync = True

#sysParams.jesdCDLvdsSync = True

#抽取和内插参数

sysParams.ddcFactorRx =[24、24]

sysParams.ddcFactorFb =[12、12]

sysParams.ducFactorTx =[12、12]

sysParams.fbNco =[3500.01、3500.01]

sysParams.lowIfNcoRx =[0、0]

sysParams.lowIfNcoTx =[0、0]

sysParams.lowIfNcoFb =[0、0]

LMKParams.pllEn =正确

LMKParams.lmkFrefClk =真

LMKParams.inputClk = 1474.56

LMKParams.sysrefFreq = 3.84

如果 simulationMode=False:

setupParams.skipFpga=1

setupParams.skipLmk = 0

AFE.skipRxConfig=0

AFE.skipFbConfig=0

AFE.skipTxConfig=0

AFE.skipAgc=0

sysParams.gpioConfigMode=1.

''

PAP 配置

sysParams.txDSAUpdateMode=1.

对于 I IN 范围(4):

sysParams.srConfigParams[i]['GainStepSize']=38

sysParams.srConfigParams[i]['AttnStepSize']=38

sysParams.srConfigParams[i]['AmplUpdateCycles']=6

sysParams.srConfigParams[i]['threshold']=30

sysParams.srConfigParams[i]['enable']=True

sysParams.srConfigParams[i]['mode']=10

#Ext AGC 配置

对于 I IN 范围(4):

sysParams.agcRegConfigParams[i]['enableIa']=0

sysParams.agcRegConfigParams[i]['phmOvrEn']=1

sysParams.agcRegConfigParams[i]['enableSa']=0

sysParams.agcRegConfigParams[i]['enableSd']=0

sysParams.agcRegConfigParams[i]['enableBa']=1

sysParams.agcRegConfigParams[i]['gainControl']=4.

sysParams.agcRegConfigParams[i]['fdsaOffset']=6

INT 引脚

sysParams.intPinsParams[0]['JESD']=True

sysParams.intPinsParams[0]['SPI']=True

sysParams.intPinsParams[0]['SRTXA']=True

sysParams.intPinsParams[0]['SRTXB']=True

sysParams.intPinsParams[0]['SRTXC']=True

sysParams.intPinsParams[0]['SRTXD']=True

sysParams.intPinsParams[0]['PLL0']=True

sysParams.intPinsParams[0]['PLL1']=True

sysParams.intPinsParams[0]['PLL2']=True

sysParams.intPinsParams[0]['PLL3']=True

sysParams.intPinsParams[0]['PLL4']=True

''

校准

sysParams.enableRxDSaFactoryCal =错误

sysParams.enableTxDSaFactoryCal =错误

sysParams.enableTxIqmcLolTrackingCorr =错误

sysParams.enableRxIqmcLolTrackingCorr = True

sysParams.txIqMcCalibMode = 0# 0 -单 FB 模式 FB AB;1 -单 FB 模式 FB CD;2 -双 FB_Mode

sysParams.txDSaCalibMode = 0

sysParams.rxDSaCalibMode = 0

logDumpInst.setFileName(ASTERIX_DIR+DEVICES_DIR+r"\config.txt")

logDumpInst.logFormat=0x4

logDumpInst.rewriteFile=1

logDumpInst.rewriteFileFormat4=1

device.optimizeWrites=0

device.rawWriteLogEn = 1.

device.rewriteFile=1

device.rawWriteLogsFile=Asterix_DIR+device_DIR+r"\test.txt"#"D:\AFE77xx_config/testBroadcast.txt"

lmk rawWriteLogEn = 0

lmk rawWriteLogsFile=device.rawWriteLogsFile

# AFE.initializeConfig ()

AFE.deviceBringup ()

device.rawWriteLogEn = 1.

lmk rawWriteLogEn = 0

engine.sampleNo=32768

AFE.TOP.OverrideTdd (1、1、1)