主题中讨论的其他器件:AFE7950、 LMK04828

我制作了 一个与 AFE7950EVM 相似的 ADC EVM ( AFE7950 )

差异如下:

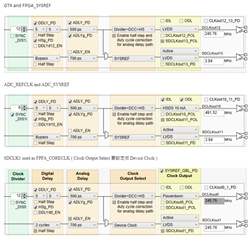

TI AFE7950EVM 中的 LMK04828输出通道版本 ADC EVM I Made

DCLK0 GTX V.S. DCLK12.

SDCLK1 FPGA_SYSREF V.S. SDLCK13.

DCLK2 ADC_REFCLK V.S. DCLK10.

SDCLK3 ADC_SYSREF V.S. SDCLK11.

SDCLK9 FPGA_REFCLK2 V.S. DCLK0

DCLK12. FPFA_CORRECLK V.S. SDCLK1

P.S. 其余内容相同,包括 TX、RX、SYNC……

下面是我的问题:如何修改软件 Latte 以便 LMK04828具有正确的输出

P.S. 我尝试根据 E2E 论坛文章修改 LMK 输出

我发现、当我更改 LMK 时钟分频器中的参数时、它只能修改 LMK。

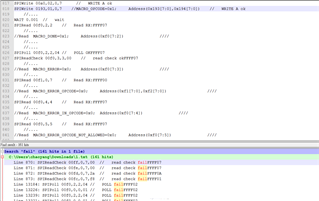

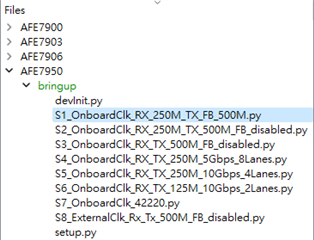

但是、一旦我运行 S1_OnboardCLK_RX_250M_TX_FB_500M.py 等脚本

LMK 复位为之前的设置、因此 ADC 找不到 REFCLK!!

请提供帮助~谢谢~