我将使用 Xilinx zynqmp 启动 afe7920。

在 Latte 中、我们有了所需的设置、

ZYNQMP 通过 SPI 将设置写入 AFE7920。

但从 AFE7920到 FPGA 的数据是不变的。

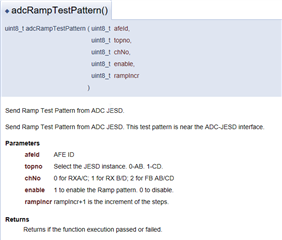

我想通过 SPI 设置从 AFE7920发送类似测试模式的数据、在查看寄存器映射时、我发现了以下寄存器。

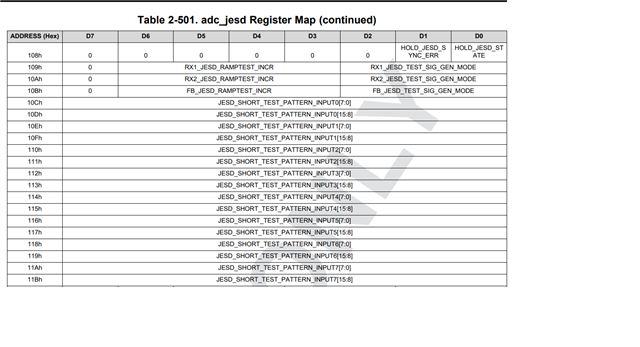

如果您查看 ADC 寄存器映射、您将看到109到11B 的测试模式寄存器。

我按如下方式设置值、在通过 FPGA ILA 查看时未看到任何值变化。

我是否缺少某些内容或设置不正确?

写入0016 01

写入010C 01

写入010d 12

写入010e 34

写入010f 56

写入0110 78

写入0111 9a

写入0112 bc

写入0113 DE

写入0114 f0

写入0115 10

写入0116 32

写入0117 54

写入0118 76

写入0119 98

写入011a BA

写入011b ed

写入0109 01或02

写入010A 01 或02

写入010C 01 或02

写入0016 02

写入010C 01

写入010d 12

写入010e 34

写入010f 56

写入0110 78

写入0111 9a

写入0112 bc

写入0113 DE

写入0114 f0

写入0115 10

写入0116 32

写入0117 54

写入0118 76

写入0119 98

写入011a BA

写入011b ed

写入0109 01

写入0109 01 或02

写入010A 01 或02

写入010C 01 或02