主题中讨论的其他器件: LMK04828、 AFE8000

我将配置 AFE8000EVM 板、与 Xilinx 的 VPK120板匹配。

使用您提供的参考设计合成 FPGA 似乎可以起作用。

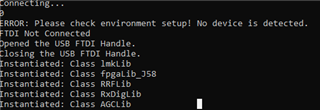

但是、当我 使用 Vivado 将映像下载到 FPGA 时、会看到以下消息:

我认为映像加载正确-我添加了一些调试逻辑、这似乎没问题、但我不知道为什么会看到这些错误消息。

进一步调试表明 FPGA 没有从 AFE8000EVM 接收时钟、而是保持在复位状态。

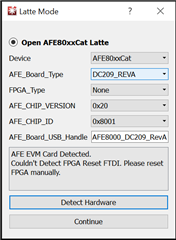

看看 AFE8000EVM 板、当我尝试连接到 Latte 时、在引导时会看到以下内容:

该消息表明它可以看到 EVM 卡、但无法看到 FPGA。 我不确定这是否是配置问题导致的。

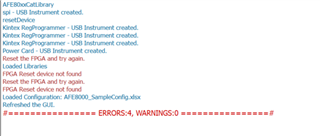

在 Latte 中按"Continue"后、主 GUI 中就会看到以下消息:

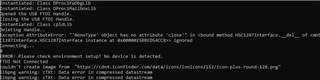

控制台日志的有趣部分如下:

您可以在这里提供的任何帮助都将非常有帮助。

除此之外、我还有几个具体的问题:

所需的配置顺序是什么。

在运行 Latte 之前、是否需要对 FPGA 成功编程? 如果是、缺少时钟是否存在问题?

或者、在配置 FPGA 之前、我是否需要访问 Latte 以使其能够对 LMK04828进行编程?

您能否确认我需要为 LMK_CLKIN 提供什么时钟频率? 在随附的文档中

发行版(RefDesign-Doc.pptx)中有对968MHz 的引用、但 AFE8000EVMBringupGuide.pptx 中建议使用10MHz。

我们认为10MHz 正确、但您能确认吗?