Other Parts Discussed in Thread: DAC38RF82

我有四个通道从 Arria10连接到 DAC38RF82。

FPGA 通道0 LID 0连接到 DAC 通道0

FPGA 通道1 LID 1连接到与之反转的 DAC 通道1

FPGA 通道2 LID 2连接到 DAC 通道4反转

FPGA 通道3 LID 3连接到 DAC 通道5

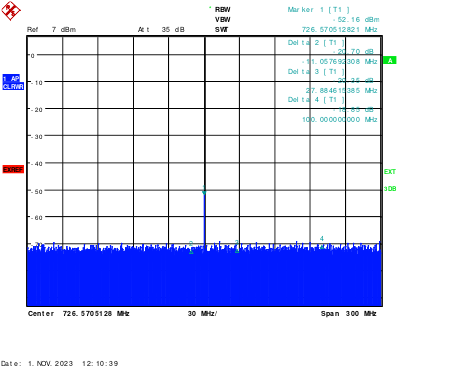

DAC 报告通道1的链路配置错误。 未报告其他错误。 根据该线程 e2e.ti.com/.../dac38rf83-link-configuration-error-reported-by-dac 的理解 、我可以禁用寄存器0x51中的位5以防止来自此错误的同步请求。 如果我这样做、JESD 接缝正常工作、我在 DAC 输出端看到信号。 我从另一个线程中看到、发送器和接收器的不同 JESD 设置可能会导致链路配置错误。 我已经检查了两次,他们的接缝是一样的。 我能想到的唯一一件事是那个特定的通道的盖子一定是错误的。 我还可以通过将 LID 设置错误来强制其他通道报告链路配置错误、但我无法消除通道1的错误。 我是否误解了有关 LID 或 OCTETPATHX_SEL 的内容?

0x146:0x0048

0x147:0x2886

0x148:0x313C

0x15F:0x0145

0x160:0x2367

0x246:0x0048

0x247:0x2886

0x248:0x313C

0x25F:0x0145

0x260:0x2367