Other Parts Discussed in Thread: AFE7900

e2e.ti.com/.../latte_5F00_script.txt

尊敬的 David:

我使用的是具有 Xilinx 超焊评估板的 AFE7900 EVM (Avnet UltraZed-7EV SOM) 器件型号(xczu7ev-fbb900-1-I)。

我使用 Latte 对 AFE7900进行编程。 定义 AFE7900参数的 Latte 脚本为:

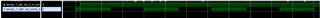

ADC 采样 = 2949.12MSPS

L M F S HD = 1 2 4 1 0

sysParams.ddcFactorRx =[24、24、24] #采用24倍 RX A、B、C 和 D 抽取的 DDC 抽取因子

完整的 Latte python 脚本随附了注释

我使用的 Xilinx AMD IP 用于 JESD204B 接收接口。

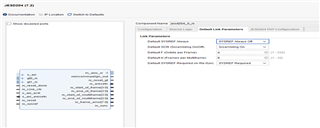

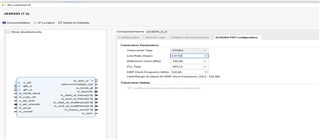

Xilinx JESD204 IP 参数

JESD204通道速率 = 4.9152Gbps

JESD204B 接口

每多帧的帧数= 8

每帧八位位组= 4

使用的通道= 4

换序启用

参考时钟= 122.88Mhz

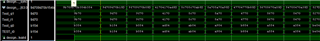

1.使用 Latte 对 AFE7900进行编程后、我们已经配置了 Xilinx JESD204 IP。 我们将得到以下日志。 我如预期的那样获得了 K 模式。 如下图所示

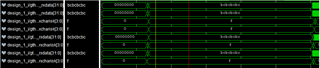

2.我也得到如下的 ILA 模式:

3.我已经使用 Latte 在 AFE7900中对 ADC 斜坡模式进行了编程。 我得到了如下所述的 Latte 日志、

写入0x0015值0x00

写入0x0016值0x01

写入0x0109值0x02

写入0x0109值0x0a

输入:ADCJesdLib 类的 adcRampTestPattern

写入0x010a 值0x02

写入0x010a 值0x0a

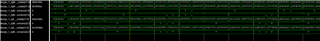

4.我已在斜坡模式的芯片范围上获得以下数据、其增量为2

5.从 RTL 到 AFE7900的同步信号也显示在下图中,系统参考时钟频率为1.92Mhz

在上面的图像中,我面临的是,在 ADC 斜坡模式中,我没有得到正确的斜坡模式递增2 (正如 Latte 配置文件所预期的那样)。 斜坡模式在某些情况下看起来似乎是随机数、 甚至是斜坡模式递减2。

您能帮助我在此配置中启动 AFE7900吗?

谢谢

梅尔