请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TLV62065-Q1 工具/软件:WEBENCH设计工具

您好:

使用官方网站 pspice model-SLIM249B.ZIP (110KB)- PSpice 模型

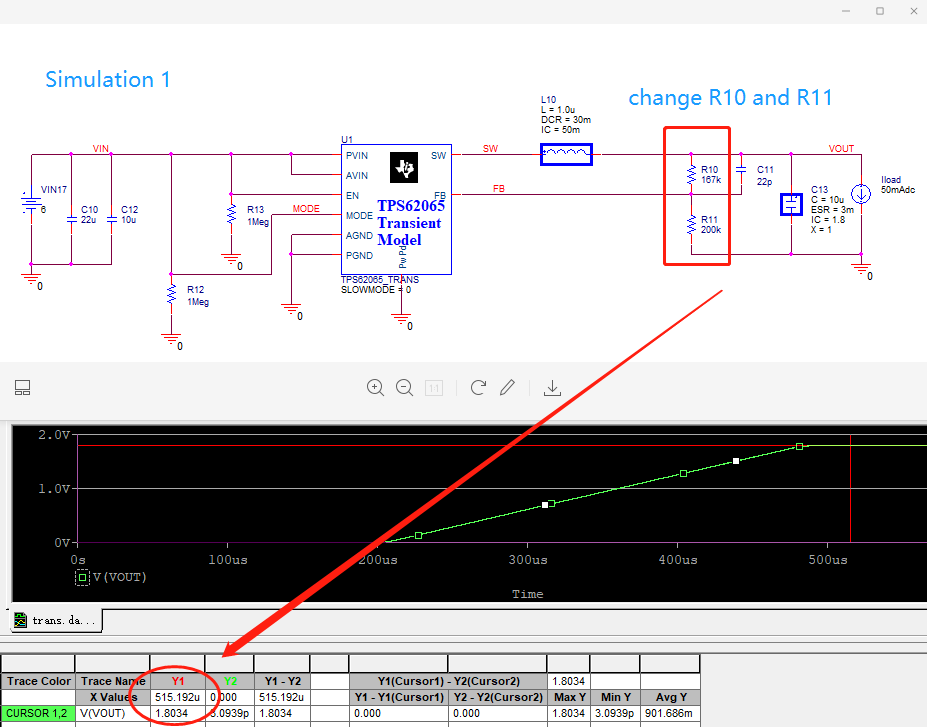

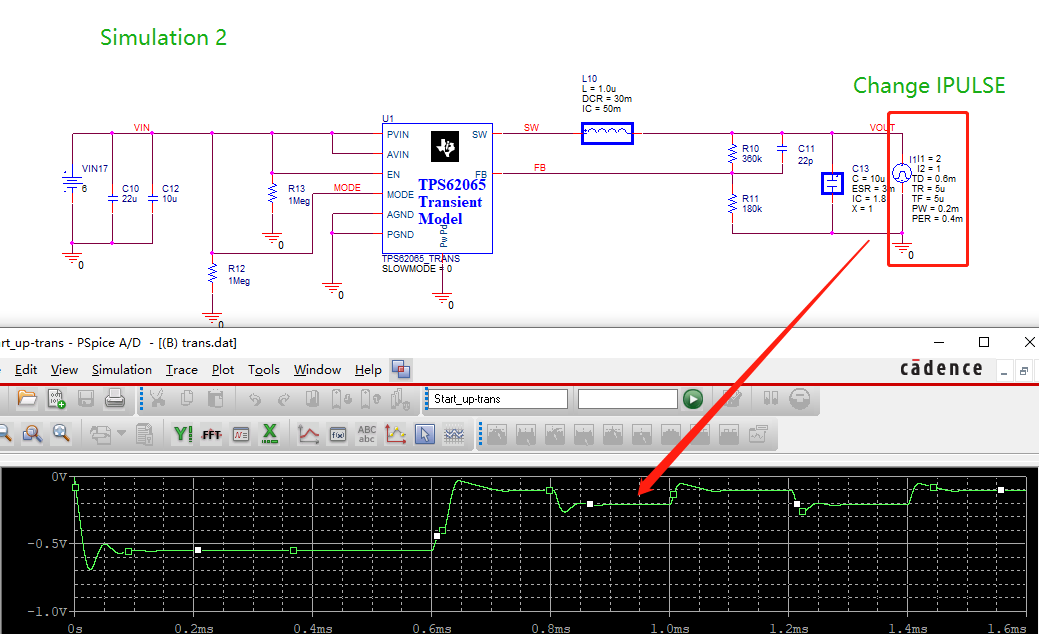

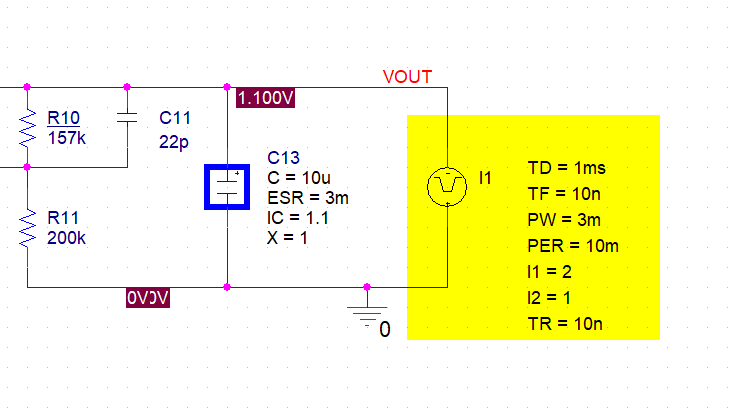

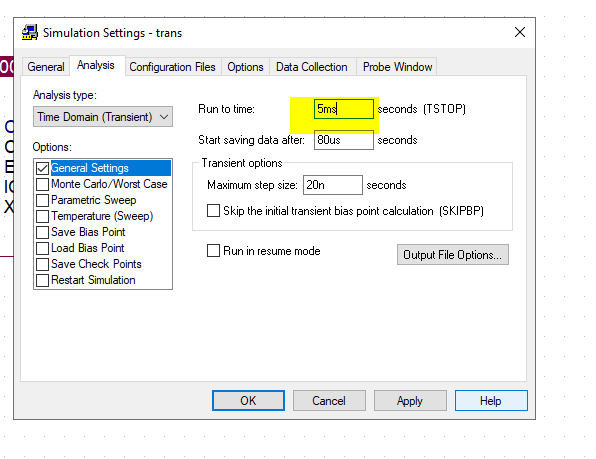

仿真条件:

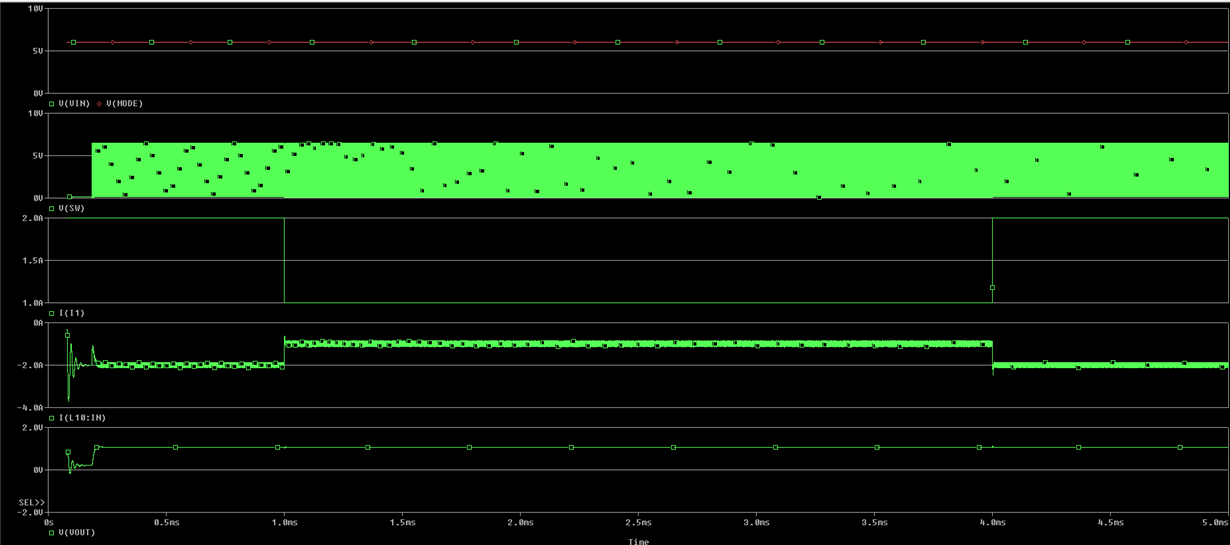

仿真1:更改 R10和 R11、所有其他参数保持不变、启动仿真、VOUT 不是1.1V、

问题1:为什么 VOUT 为1.8V?

仿真2:更改 Iload、所有其他参数保持不变、启动仿真、VOUT 波形异常。

问题1:为什么 VOUT 波形异常?

谢谢