Thread 中讨论的其他器件:SysConfig

你好。

我正在使用一个仅支持 SPI 模式0和3 (POL=0、PHA =0或 POL=1、PHA =0)的外部闪存芯片。

当我将 SPI 驱动器配置为使用模式0或3 (SPI_POL0_PHA0或 SPI_POL1_PHA0)时、每个8位帧之间会暂停、在这种情况下 CS 线路短暂拉高、从而结束与外部芯片的任何通信。 请参见图像。

当我将 SPI 驱动 器配置为模式1或模式2 (SPI_POL1_PHA1或 SPI_POL0_PHA1)时。 没有帧暂停、但外部芯片不支持这些模式。 请参见图像。

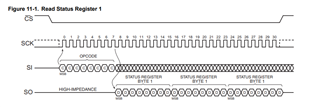

更换内容应如下所示、见闪存芯片数据表。 请参见图像。

我发现建议将 spiCC26X2DMAHWAttrs 中的.minDmaTransferSize 从默认值10更改为1、但这似乎没有影响。

非常感谢您的任何帮助!