我们对 Vdd=0v 有一些顾虑。

VDD=0v、IO 引脚是高阻态还是其他什么

VDD=0v、逻辑引脚如何

我们的应用是 SPI 树。

当 Vdd 没有电源时、我们需要测量 IO 是否为高阻态、而 不是 IO 连接到 GND 或 Vcc。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Shih、

TMUX1574具有断电保护和失效防护逻辑-这些功能将处理您所关心的两种情况。

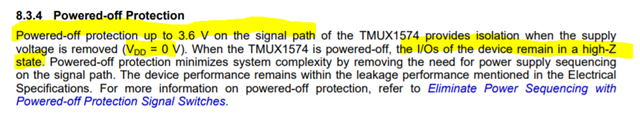

1个 I/O 引脚为高阻态(当 VDD = 0V 时、模拟 I/O 上具有高达3.6V 的保护)。 请参阅以下数据表摘录:

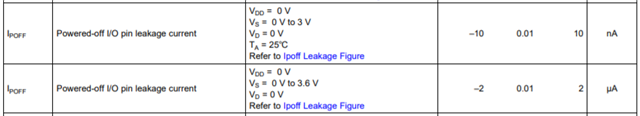

可能存在少量泄漏电流-请参阅下面的断电情况下的泄漏:

第一个规格在室温下的输入为0V-3V、第二个规格在整个温度范围内的输入为0V-3.6V (这就是第一个规格和第二个规格之间出现增加的原因)

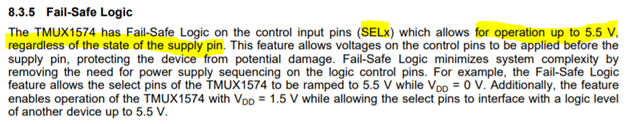

2.由于采用数字逻辑门架构、逻辑引脚的输入通常为高阻抗、因此引脚特性变化不大。 然而、借助于高达5.5V 的失效防护逻辑、可在 VDD = 0V 时在 SEL 引脚上斜升、而不会损坏器件。 在 VDD = 1.5V 之前、器件将不会"切换"-请参阅下面的数据表摘录:

总的来说、TMUX1574应该能够在这个应用中正常工作。 由于其配置、通道规格以及保护特性、这是 SPI 应用中非常受欢迎的器件。 所有这些使得 TMUX1574成为 SPI 应用的理想选择。

如果您有任何其他问题、请告诉我!

最棒的

Parker Dodson