1、单个 tmux136芯片和三个串联 tmux136芯片之间的带宽差是多少、或者带宽不受芯片的多级联影响。

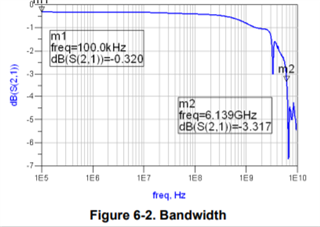

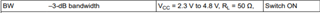

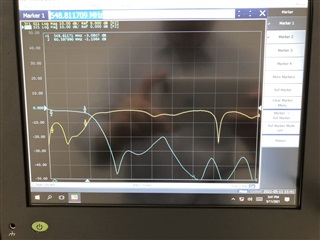

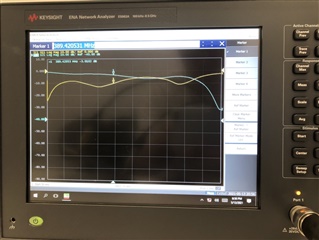

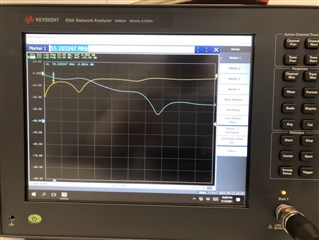

2.在规范中写入的带宽(-3dB):6.1GHz。 带宽图还显示、当带宽处于1G 范围内时、带宽为 dB (S (2、1))>-0.5。 1G 内的频率响应非常好。 上面是一条直线、但我们发现它不是。 在100MHz 时、出现 dB (S (2、1))<-1.5的情况。 在1GHz 带宽范围内、-3dB 是否也会定期出现。

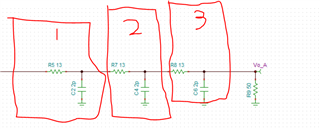

如果可以实现、在设计多级联芯片时应注意什么、以便带宽可以达到规格带宽曲线中所示的带宽。 当规格带宽曲线中显示的带宽在1G 以内时、它是 dB (S (2、1))>-0.5、在1G 内、频率响应是一条近似的直线。

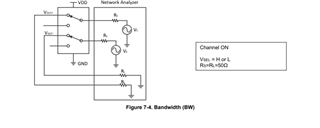

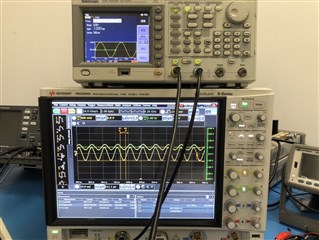

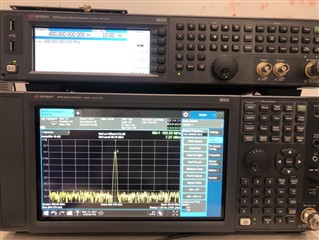

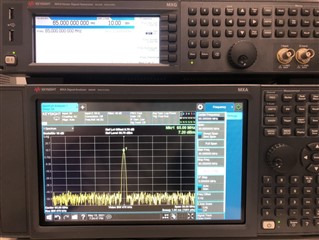

4.您是否使用常用的测试方法来测试带宽,如果不使用,您使用哪种测试方法?