您好!

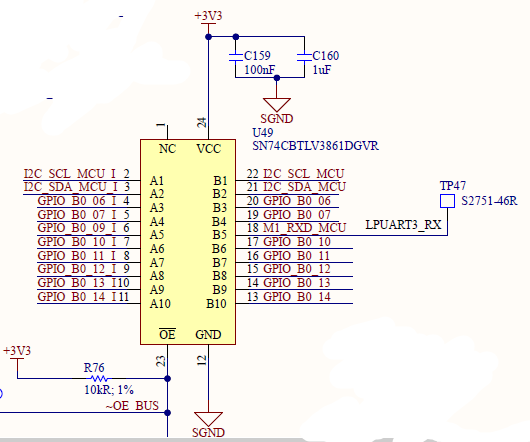

作为 电路板上电序列的一部分、我们使用 SN74CBTLV3861 10位总线开关将 MCU 引脚与外部负载隔离。

我们最近注意到的一件事是、

我们的工作电压为 Vcc=3.3V

情况1 (开关高阻抗): A1 =开路;B1 =通过2kR 上拉至3.3V;!OE =高电平.... 然后 B1测量值报告3.3V;A1报告悬空

情况2 (开关打开):A1 =开路;B1 =通过2kR 上拉至3.3V;!OE =低电平...然后 B1测量为3.15V;A1报告为3.15V

由于某种原因、总线开关激活会导致 B1上的电平从3.3V 下降到3.15V。 我们已在多个器件和电路板上注意到这一点、因此不太可能发生损坏。

您能否帮助我们了解 CASE2中出现压降的原因、即使通过数据表指定的5 Ω 导通电阻和轨到轨性能也是如此?

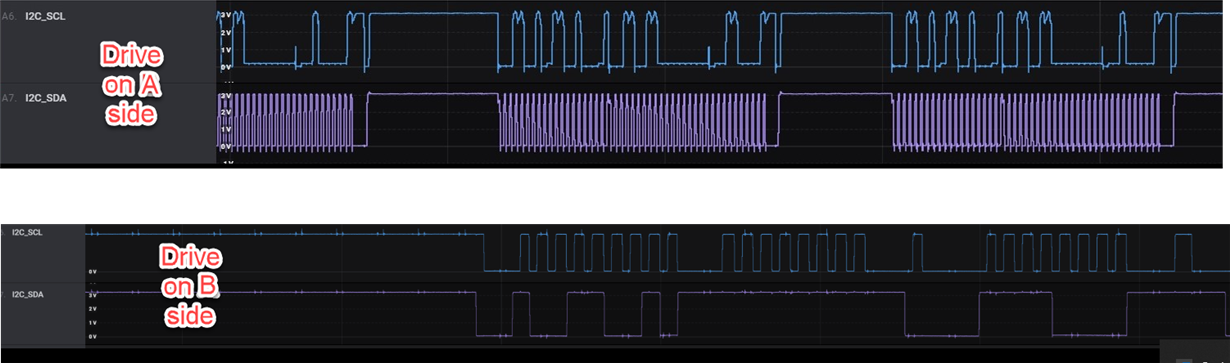

供参考:这些引脚的应用是 I2C (100k/400kbit/s)。

非常感谢!

Simon M.

隔离