主题中讨论的其他器件: TIDC-CC2650STK-SENSORTAG、 CC2651R3

嗨、大家好!

射频电路有问题、天线仅在约2米处工作正常。 我正尝试使用 SmartRF Studio 7对其进行测试。 我有两个用于 CC2651P3的 LP、因此在测试 RSSI 时、我将结果与 LP 进行了比较、因为我知道它们没问题。

结果是、当 TX 从我的自定义 PCB 到 LP 时、I 具有适当的连接强度和100%的成功率(测试 LP 到 LP 时与此类似)。 但测试 RX 时、结果非常差、大约为-90dBm (LP 上为-55)、成功率可能为20%。

看起来我只有 RX 有问题、TX 工作得不错、与 LP 类似。 但我在这个舞台上还是个新手,所以我完全错了。 这些可能只是我的错误假设和结果。

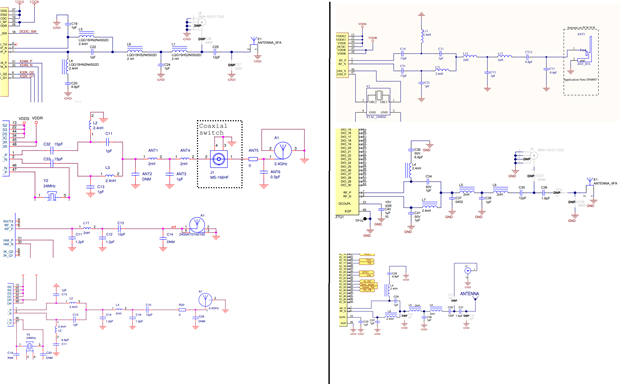

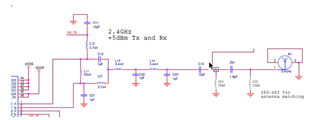

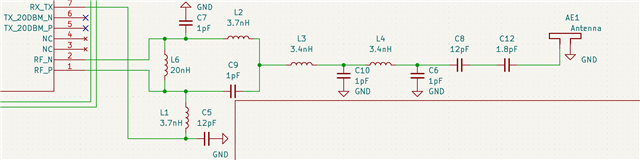

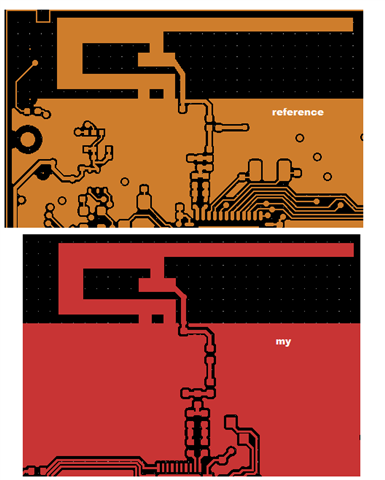

我尚不清楚天线匹配的主题、因此我决定采用 TIDC-CC2650STK-SENSORTAG 设计:

https://www.ti.com/tool/TIDC-CC2650STK-SENSORTAG

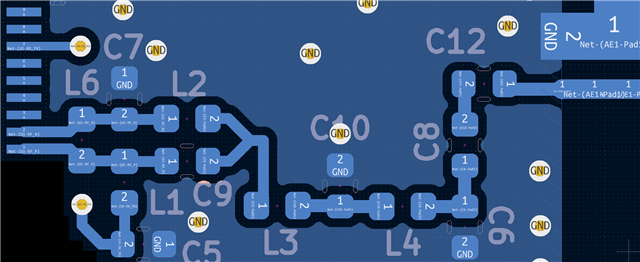

遗憾的是、您的所有示例都位于 Allegro Cadence 中、我将使用 KiCad、因此我必须手动复制设计、结果如下:

它不是100%准确,但我希望它足够接近(如果不是请告诉我)。 在按照参考设计执行操作时、我更换了 BOM 中的几个器件、因为它们不可用:

C32:GRM0332C1H150JA01D -> GJM1555C1H150FB01D

C33:GRM0332C1H150JA01D -> GJM1555C1H150FB01D

L2:LQG15HS2N4S02D -> LQG15HS2N4S02D

C11:GRM1555C1H1R0CA01D -> GJM1555C1H1R0BB01D

C13:GRM1555C1H1R0CA01D -> GJM1555C1H1R0BB01D

L3:LQG15HS2N4S02D -> LQG15HS2N4S02D

ANT1:LQG15HS2N0S02D -> LQG15HN2N0S02D

ANT3:GRM1555C1H1R0CA01D -> GJM1555C1H1R0BB01D

ANT4:LQG15HS2N0S02D -> LQG15HN2N0S02D

ANT5:电阻器_0402_0_50V_0.063W_M_+/-200ppm -> UNI-ROYAL (Uniroyal Elec) 0402WGF0000TCE

ANT6:GRM1555C1HR50BA01D -> GJM1555C1HR50BB01D

其中大部分来自 Murata、我当时使用他们的比较页面来检查组件。

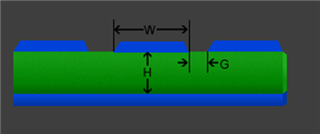

最后一项更改(至少我看到过)是 PCB 层、在参考设计中有4层、厚度为1.6、而 PCB 厚度为2层(厚度为1.6)。

我试图尽可能多地进行搜索并对所有内容进行比较、但我看不出问题出在哪里。

如果您看到 它、请告诉我、我知道这可能是简单而明显的。

非常感谢您花时间阅读本书、

迈克