您好:

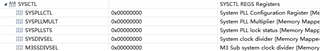

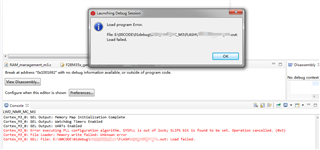

问题:工程中使用的F28M35芯片多个设计板出现上电之后,观察M3核运行主频,发现主频不对,锁相环被旁路掉。如果手动通过XRS脚接地复位一次,PLL就能工作正常。

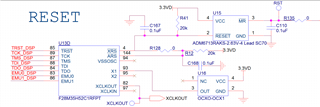

设计:

设计外部输入有源晶振时钟30M,M3设计主频75M,PLL设置如下:

// Sets up PLL, M3 running at 75MHz and C28 running at 150MHz

SysCtlClockConfigSet(SYSCTL_USE_PLL | (SYSCTL_SPLLIMULT_M & 0xA) |

SYSCTL_SYSDIV_1 | SYSCTL_M3SSDIV_2 |SYSCTL_XCLKDIV_4);

测试芯片供电正常,V18实测1.87V,V12实测1.21V。时钟输入30M正常。复位信号正常。

芯片此时是否损坏?或者工作于PLL旁路状态,或者DEEP SLEEP模式?