Other Parts Discussed in Thread: C2000WARE

大家好,我看了说明书 TRM(Rev. H),感觉里面有很多部分讲的很不清楚。

首先,非常感谢您的耐心阅读,写的有点多,但是,确实是相互关联的问题,没办法拆分成多个小问题。

说明书全文中只有在章节19.13.1 SCI FIFO Description 中的第6点 Buffers,出现过TXBUF,其他地方都是SCITXBUF,所以,一直以来我都认为这两个是一个寄存器,但是,如果将这两个寄存器视为一个,在理解上又有很多矛盾点,所以,我才会有这么一个问题: SCITXBUF 和 TXBUF 是同一个寄存器么?

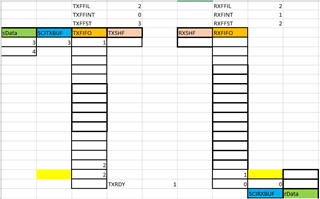

(为了方便讨论,后面会将TXFIFO上方的称为TXBUF,下方的称为SCITXBUF,如下图所示)

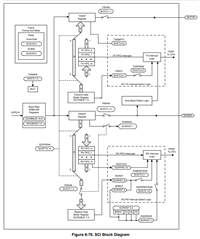

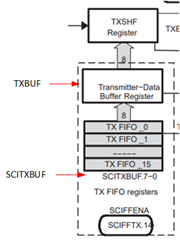

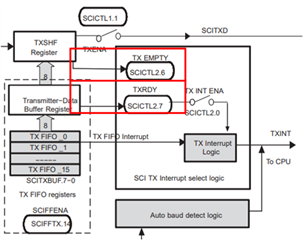

根据TRM(Rev.H)图19-2 SCI模组框图可以看出,TX FIFO队列前有一个 SCITXBUF.7-0,TX FIFO之后有一个 transmitter-Data Buffer Register.

但是,说明书里SCITXBUF的名称也是:SCITXBUF — transmitter data buffer register (p.2093). 所以我很疑惑,这两个寄存器是指的同一个么?

根据 章节19.13.1 SCI FIFO Description 中 第6点 关于Buffer的说明:

“The one-word transmit buffer of the standard SCI functions as a transition buffer between the transmit FIFO and shift register”

上句可以确定,这个一字长的发送缓冲器 位于 TX FIFO和 TXSHF之间。

“ With the FIFO enabled, TXSHF is directly loaded after an optional delay value (SCIFFCT), TXBUF is not used. ”

当FIFO模式启用时,TXSHF直接(从TX FIFO中根据选定的延迟)装填数据,不使用TXBUF。

所以,我认为的是,这个one-word transmit buffer就是特指TXBUF,而不是SCITXBUF.

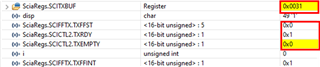

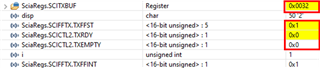

而且,发送首先需要对SCITXBUF写入,我单步debug的时候, 在CCS Expressions里观察SCITXBUF的写入是先于 FFTXST加1的。

所以,我理解的是,SCITXBUF和TXBUF不是一个寄存器,TX FIFO模式中,被越过的是TXBUF,但仍然必须通过对SCITXBUF写操作,才能发送。

而且,寄存器SCITXBUF先于TX FIFO进行装填的 (也就是说存在一个三级关系:SCITXBUF -> TX FIFO -> (TXBUF )-> TXSHF)。

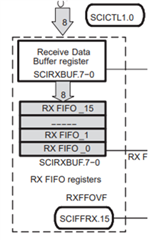

但是,接收器框图中在 RX FIFO队列的上下都是 SCIRXBUF.7-0,如果不存在RXBUF和SCIRXBUF的区别,如果说接收是发送的逆过程,那么,SCITXBUF和TXBUF又应该是一个寄存器。

与这个问题相关的是:

- 到底是SCITXBUF还是TXBUF,决定了TXRDY的值

- TXEMPTY 发送器空标志位到底什么时候为0?

说明书中的框图19-2还有一个点让我很疑惑:

从TXSHF延伸出指向TX EMPTY的箭头,是不是说明,其实,TX EMPTY只由TXSHF决定?

从TXBUF延伸出指向TXRDY的箭头,是不是说明,其实,TX RDY只由TXBUF决定?

但是根据说明书描述的:

- 只要SCITXBUF或/与TXSHF中被装填了数据,那么TX EMPTY 标志位置0.

(原文: 0h (R/W) = Transmitter buffer or shift register or both are loaded with data; 1h (R/W) = Transmitter buffer and shift registers are both empty)

问题:那就说明不只是TXSHF决定TXEMPTY,与框图所绘制的相互矛盾。还是第一个问题,到底是SCITXBUF还是TXBUF影响这一位?

- TXRDY当 SCITXBUF满时,被置0;SCITXBUF中的数据被移出后,被置1

(原文:0h (R/W) = SCITXBUF is full; 1h (R/W) = SCITXBUF is ready to receive the next character (SCITXBUF empty?))

问题: 我认为是TX FIFO队列前的SCITXBUF决定了TXRDY的值,而不是TX FIFO队列后的TXBUF, 因为如果是FIFO模式,TXBUF不会被使用,那么TXRDY的值也不应该受影响,但是,实际的实验中, HWREGH(base + SCI_O_TXBUF) = array[i]; 后, TXRDY会被置0

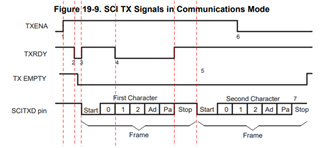

章节19.10.2中的图19-9所示的例子,又让我更加疑惑。

时刻1:TXENA发送使能。

时刻2:SCITXBUF被写入,此时TXRDY置0,同时TXEMPTY也应该置零,但是,上图中,TXEMPTY则是在时刻2与3之间置零的, 说明SCITXBUF被写入并没有影响TXEMPTY.

问题:这是真实会出现的吗,还是图示有错? 我自己实验时,只要SCITXBUF被写入,TXEMPTY就会置0。

时刻3:SCI将数据移入TXSHF,所以,TXRDY置1,说明数据从SCITXBUF中被转移到TXSHF中,现在SCITXBUF为空,准备好接收第二个字符。

时刻4到时刻5之间:发送完第一帧的Pa位后,图中TXRDY置1说明,此时,第二个数据被装填到TXSHF中,SCITXBUF再次为空,准备好接收新字符。

问题:此时,第一帧的发送还没有结束,Stop还没发出,TXSHF非空,第一帧的发送未完成,此时,是否可以向TXSHF装填新的数据,从而如上图所示的,让TXRDY置1。

这里不知道有没有启用FIFO,但是根据FIFO模式的描述,只有当TXSHF完成了最后一位的发送,才能够向TXSHF进行装填。

不知道标准SCI是不是允许像上图所示的,可以在第一帧发送Stop位时,就装填新的数据,从而置位TXRDY。

说明书里我没有找到相关内容。

感谢您的耐心阅读,望不吝赐教。

(向SCITXBUF写入'1')

(向SCITXBUF写入'1') (向SCITXBUF写入'2')

(向SCITXBUF写入'2')