Other Parts Discussed in Thread: ADS131M06, C2000WARE

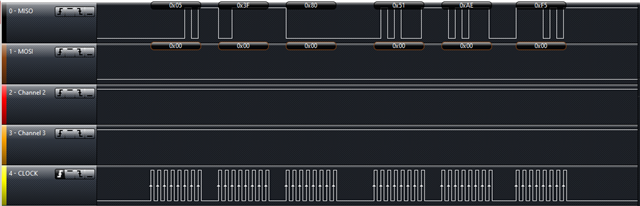

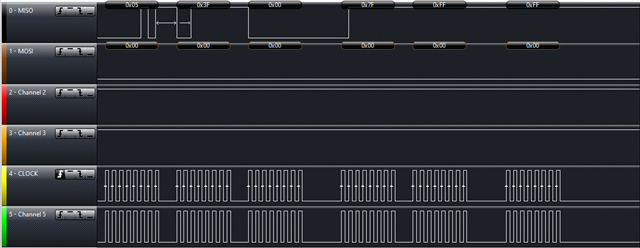

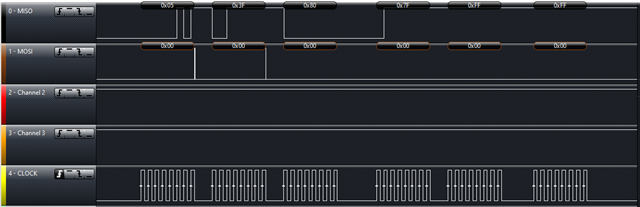

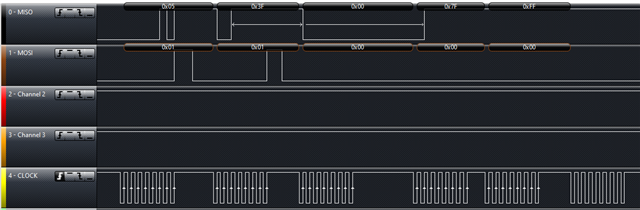

MCU SPI能输出时钟信号,SOMI能接收外部输入信号,但是SIMO无输出信号,一直为0

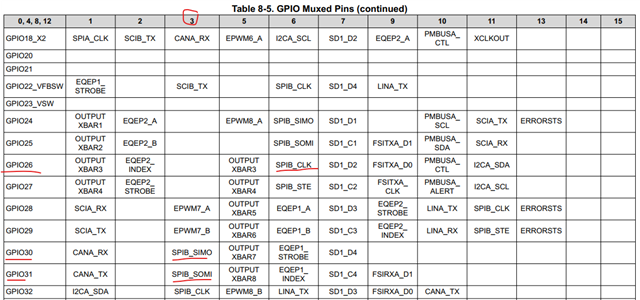

IO映射:

RESET :GPIO56

DRDY :GPIO27

SCLK :GPIO26

SOMI :GPIO31

SIMO :GPIO30

SPI从设备为ads131m06,不管mcu发出什么数据,SIMO上捕获到的数据总是0.

将GPIO30配置为普通IO,可以控制其高低电平。

请帮忙看看是哪里出了问题

初始化SPI代码:

void SPI_Initialize(void)

{

SpibRegs.SPICCR.bit.SPISWRESET = 0; //spi reset to configuration mode

SpibRegs.SPICCR.bit.CLKPOLARITY = 0; //DOut on falling Edge,Din on rising Edge

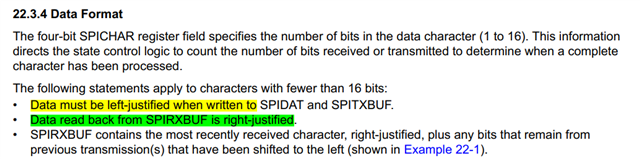

SpibRegs.SPICCR.bit.SPICHAR = (8-1); //16-bit word

SpibRegs.SPICCR.bit.SPILBK = 0; //loopback disabled

SpibRegs.SPICTL.bit.MASTER_SLAVE = 1; //Master

SpibRegs.SPICTL.bit.TALK = 1; //Transmit Enable

SpibRegs.SPICTL.bit.CLK_PHASE = 0; //normal clocking scheme,no delaying

SpibRegs.SPICTL.bit.SPIINTENA = 0; //Interrupt Disable

SpibRegs.SPIBRR.bit.SPI_BIT_RATE = SPI_BRR; //500kbps

SpibRegs.SPIPRI.bit.FREE = 1; //Halting on a breakpoint will not halt the SPI

DELAY_US(10);

//b15,SPIRST =1,resume FIFO to transmit or receive

//b14,SPIFFENA =1,enable FIFO

//b13,TXFIFO =1,release TX FIFO from reset

//b6,TXFFINTCLR =1,clear SPIFFTX[TXFFINT] flag

//b4~b0,TXFFIL =4,generate TX FIFO interrupt when there are less than 4 words in TX buffer

SpibRegs.SPIFFTX.all = 0xE040;

//b13,RXFIFORESET=1,re-enable RXFIFO

//b6,RXFFINTCLR =1,clear SPIFFRX[RXFFINT] flag

//b4-b0,RXFFIL = F,generate RX FIFO intterupt when there are more than 15 words in RX buffer

SpibRegs.SPIFFRX.all = 0x204F;

//no delay between every transfer from FIFO transmit buffer to transmit shift register

SpibRegs.SPIFFCT.all = 0x0;

SpibRegs.SPICCR.bit.SPISWRESET = 1; //Release the SPI from reset

SPI_InitGpio();

}

//

// InitSpiGpio - Initialize SPIA GPIOs

//

void SPI_InitGpio()

{

EALLOW;

GpioCtrlRegs.GPAPUD.bit.GPIO30 = 0; // Enable pull-up (SPISIMO)

GpioCtrlRegs.GPAPUD.bit.GPIO31 = 0; // Enable pull-up (SPISOMI)

GpioCtrlRegs.GPAPUD.bit.GPIO26 = 0; // Enable pull-up (SPICLK)

GpioCtrlRegs.GPAPUD.bit.GPIO27 = 0; // Enable pull-up (SPISTE)

GpioCtrlRegs.GPAQSEL2.bit.GPIO30 = 3; // Asynch input (SPISIMO)

GpioCtrlRegs.GPAQSEL2.bit.GPIO31 = 3; // Asynch input (SPISOMI)

GpioCtrlRegs.GPAQSEL2.bit.GPIO26 = 3; // Asynch input (SPICLK)

GpioCtrlRegs.GPAQSEL2.bit.GPIO27 = 3; // Asynch input (SPISTE)

GpioCtrlRegs.GPAGMUX2.bit.GPIO30 = 0; //0x3

GpioCtrlRegs.GPAMUX2.bit.GPIO30 = 3; //SPIB_SIMO

GpioCtrlRegs.GPAGMUX2.bit.GPIO31 = 0; //0x3

GpioCtrlRegs.GPAMUX2.bit.GPIO31 = 3; //SPIB_SOMI

GpioCtrlRegs.GPAGMUX2.bit.GPIO26 = 1; //0x6

GpioCtrlRegs.GPAMUX2.bit.GPIO26 = 2; //SPIB_CLK

GpioCtrlRegs.GPAGMUX2.bit.GPIO27 = 0; //

GpioCtrlRegs.GPAMUX2.bit.GPIO27 = 0; //

GpioCtrlRegs.GPADIR.bit.GPIO27 = 0; // Input

GpioCtrlRegs.GPAPUD.bit.GPIO27 = 0; // Enable pull-up /DRDY

GpioCtrlRegs.GPACTRL.bit.QUALPRD3= 0x3;//6 SYSCLK cycles

GpioCtrlRegs.GPBGMUX2.bit.GPIO56 = 0;

GpioCtrlRegs.GPBMUX2.bit.GPIO56 = 0;

GpioCtrlRegs.GPBPUD.bit.GPIO56 = 0; // Enable pull-up (SPI /RESET)

GpioCtrlRegs.GPBDIR.bit.GPIO56 = 1; // Output

GpioDataRegs.GPBSET.bit.GPIO56 = 1; // High

// GpioDataRegs.GPBCLEAR.bit.GPIO56 = 1; // Low,保持复位状态

//GpioCtrlRegs.GPAGMUX2.bit.GPIO30 = 0; //0

//GpioCtrlRegs.GPAMUX2.bit.GPIO30 = 0; //GPIO30

//GpioCtrlRegs.GPADIR.bit.GPIO30 = 1; // Output

EDIS;

}