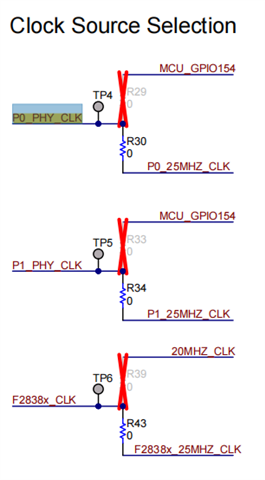

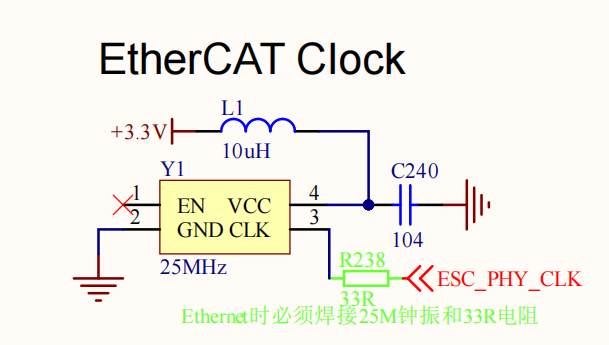

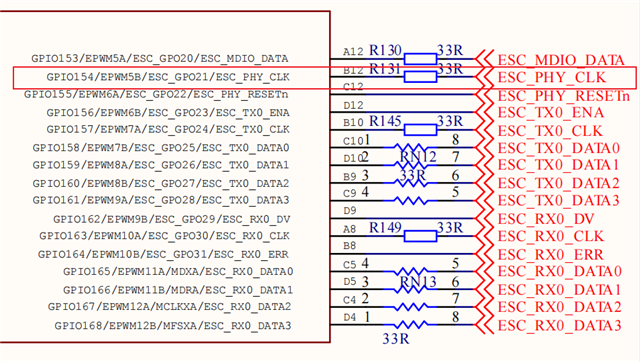

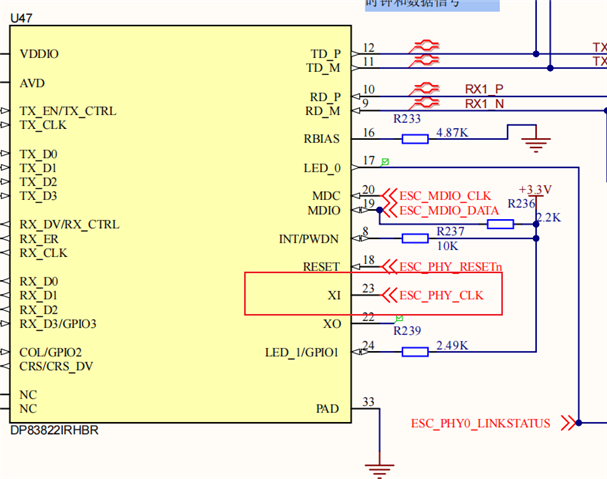

我想询问一下TI官方的TMDSCNCD28388D控制板中关于EtherCAT时钟的问题,下图1,2为TMDSCNCD28388D的时钟设计,图3,4,5为我自己设计的电路板的额时钟设计,其中10M为MCU时钟25M是给DP83822IRHBR提供的时钟,但是其中R238电阻还未焊接,ESC_PHY_CLK的网络节点与F28388的GPIO154、DP83822IRHBR的23引脚XI时钟输入相连。官方TMDSCNCD28388D中F28388的主控与P0_PHY_CLK均为25M,但是图二中红色的大叉是表示这些时钟与MCU_GPIO154都处在断开的状态吗?如果是处在断开的状态,那按照F28388 Technical_Reference_Manual中(图6)对EtherCAT时钟的描述是否会相驳?如果不相博,请问一下我个人设计的电路板关于EtherCAT这一块的时钟应该做出如何的修改呢?或者说如果要使用我上述的硬件配置要对参考例程进行如何修改?

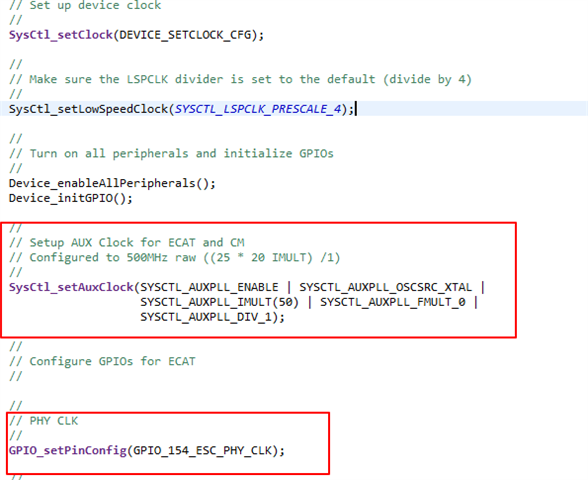

图1

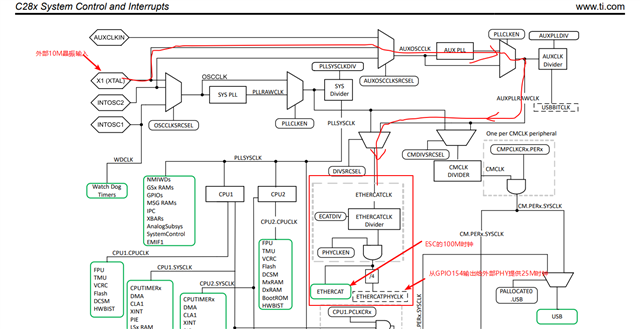

图2

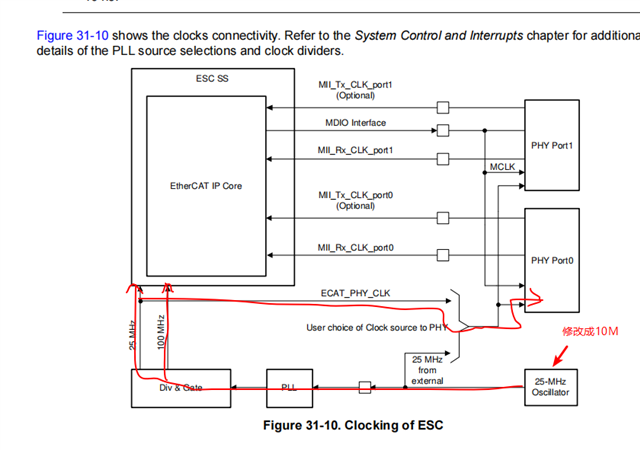

图3 EtherCAT25M时钟

图4

图5

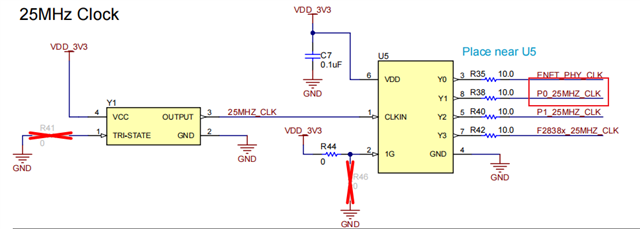

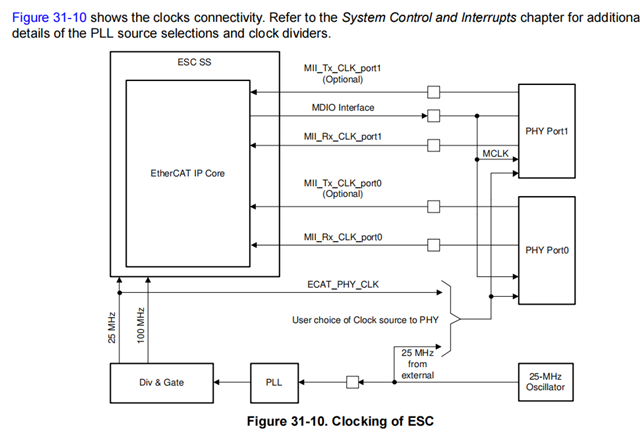

图6 Technical_Reference_Manual中对ESC时钟的描述