Hi Experts:

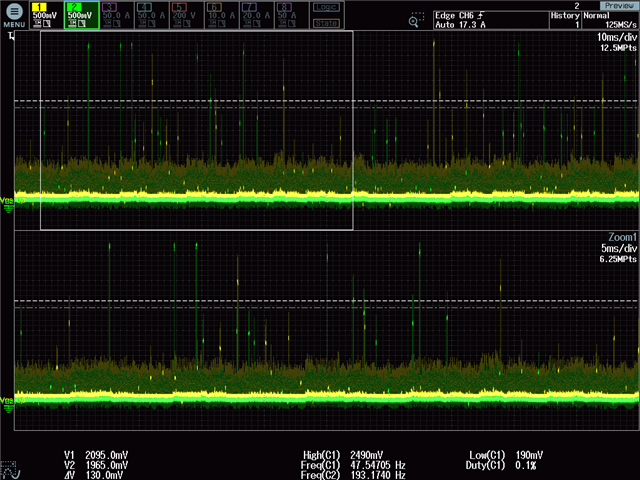

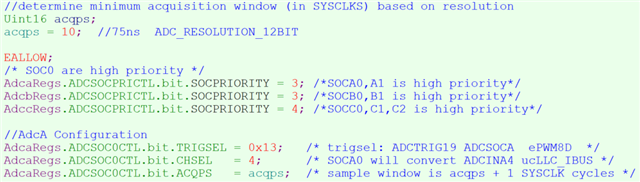

我们在应用TI F280039中遇到AD模块采样不稳定的问题,现象是外部送入AD端口的信号是稳定且干净的,但是通过DAC将MCU内部AD转换后的信号打出来后发现信号上存在很大的干扰,如下图所示,黄色和绿色是通过DAC打出来的内部AD模块结果寄存器中的值,看起来像是AD模块工作有问题。如下是我们关于AD模块的配置,采用外部供电。 请问有发现过类似的问题吗?这个问题对我们的控制影响很大,麻烦帮忙看看,谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Experts:

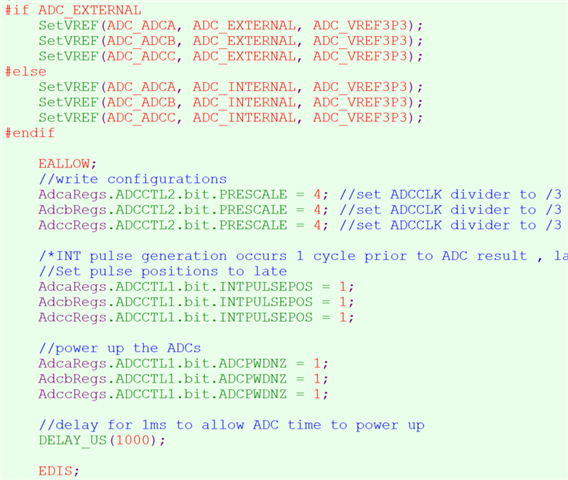

我们在应用TI F280039中遇到AD模块采样不稳定的问题,现象是外部送入AD端口的信号是稳定且干净的,但是通过DAC将MCU内部AD转换后的信号打出来后发现信号上存在很大的干扰,如下图所示,黄色和绿色是通过DAC打出来的内部AD模块结果寄存器中的值,看起来像是AD模块工作有问题。如下是我们关于AD模块的配置,采用外部供电。 请问有发现过类似的问题吗?这个问题对我们的控制影响很大,麻烦帮忙看看,谢谢!

Hi Yale:

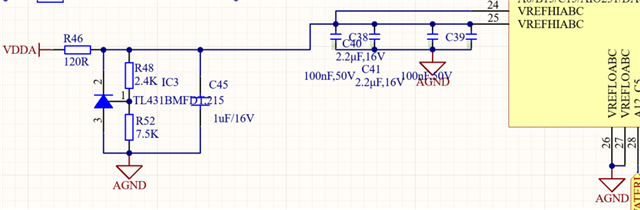

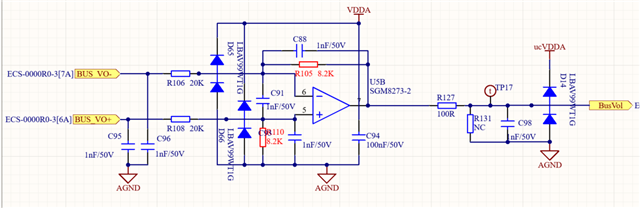

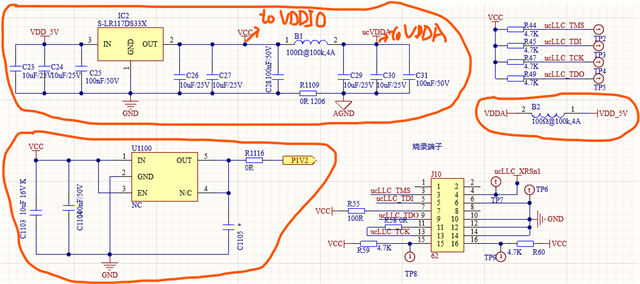

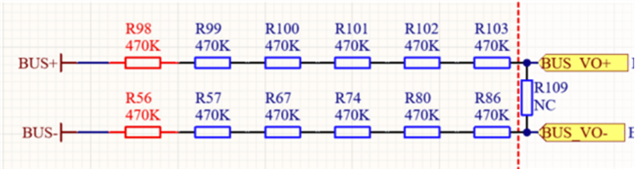

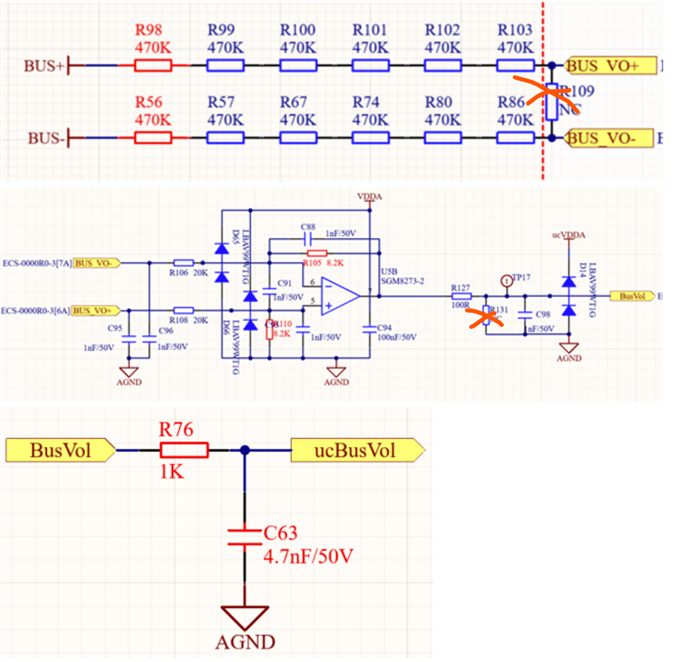

如下图1所示为为我们的voltage reference circuit, VDDA为5V,通过稳压芯片产生3.3V给AD外部基准供电,实验中有测试Pin24和Pin25电压波形,3.3V是稳定的。

图1

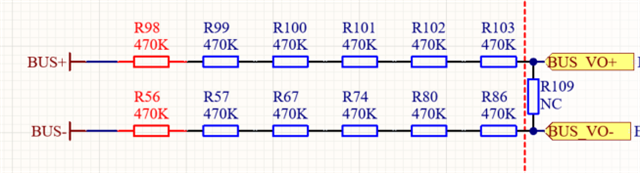

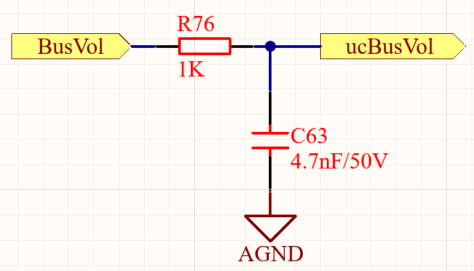

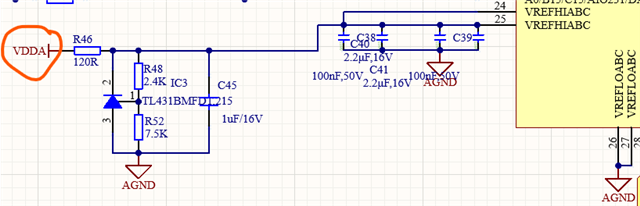

如下图2所示为我们的采样网络,Bus+和Bus-为800V左右的高压,经过分压和差分电路调理后送入AD端口(ucBusVol),实测该信号也是稳定的。

图2

另外我想问一下会不会与MCU layout的铺地有关,我们现在layout上将模拟地和数字地分开了。

Hi Yale:

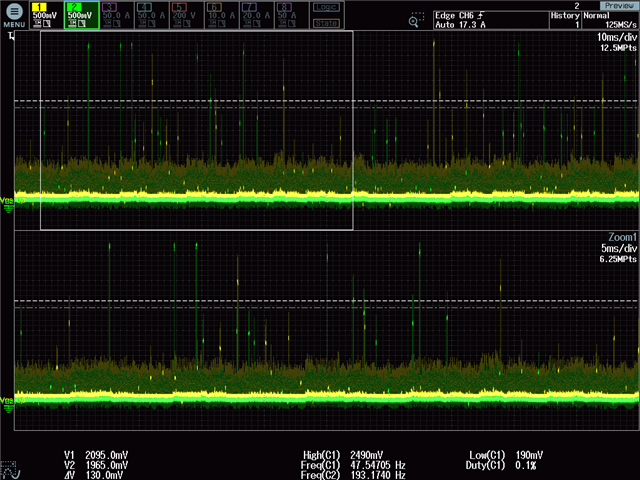

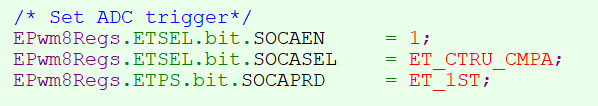

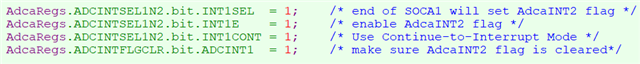

不是很清楚Ibukun Olumuyiwa 回复的意思。他的意思是如果我们是通过DMA读取ADCResult寄存器,可能会由于配置不对导致读取的数据有问题?我们实际是用的是ADCINT中断的方式读取ADC Result,首先设置EPWM模块以固定频率产生SOC信号,SOCA1转换完成后触发ADC中断,然后在中断服务函数里统一读取各个采样通道的结果,这样配置会有问题吗?

Hi Yale:

我回复一下Joseph的问题,麻烦跟进一下,谢谢!

1) As shown in Figure 1 below, the customer's voltage reference circuit, VDDA is 5V, and 3.3V is generated through the voltage regulato

Is VDDA supply and VDDIO supply generated from the same regulator? When these supplies are ganged, switching noise from the digital logic may couple to the VREF line. This could be a potential reason for the noise being observed.

如下图所示为我们MCU完整的供电网络,其中MCU数字供电VDDIO和模拟供电VDDA由同一个LDO产生,不过两者之间通过磁珠相连。AD模块的外部供电由另外一个LDO产生。请问VDDA和VDDIO这样供电可能会有问题?我们以前的项目方案都是由一个LDO产生两路供电的,实测下来供电信号是稳定的。

2)Figure 1 (input network) shows a string of 6 470k resistors (~2.8M series resistance per input). I do not see any voltage divider though so it seems to be that the 800V goes directly to the ADC channels, which obviously is not correct. Maybe there is a missing resistor going to ground that is not shown in the diagram?

表述有问题,Bus+和Bus-直接进入差分放大电路,没有分压。

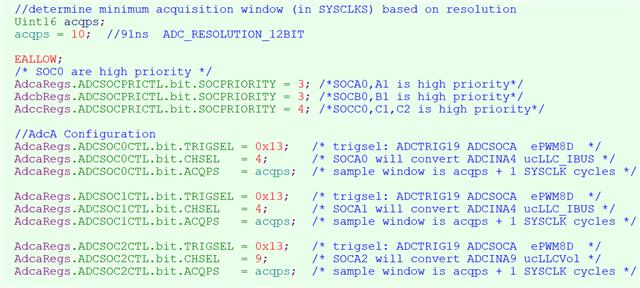

3)Regardless, the input network involves the use of high value resistors and capacitance that directly connects to the ADC inputs and this would require higher ACQPS because of this impedance for the ADC to properly sample the signal. Can you check what ACQPS value that the customer is using?

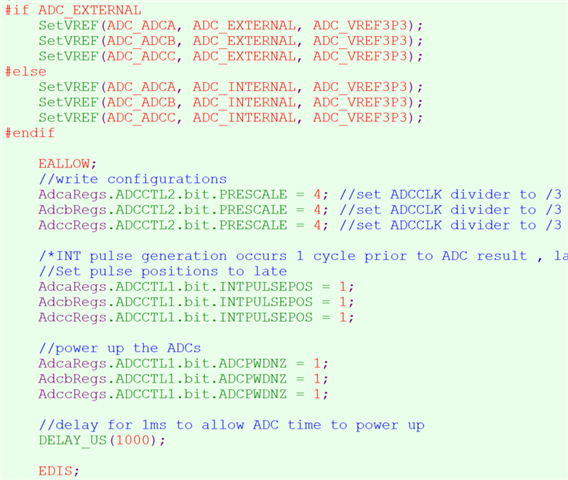

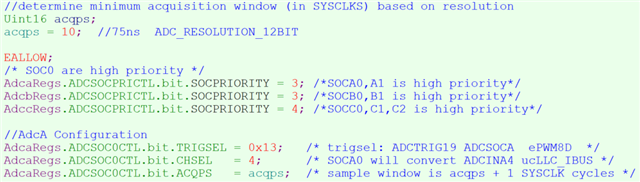

如下图所示为我们ACQPS的配置,ACQPS = 10,所有采样通道都配置成相同的,请问这样配置是否有问题?

Hi Yale:

我把我们的电压采样线路再重新描述一下,图上R109和R131两颗电阻实际没有使用,其实就是一个简单的差分放大后面接上两级RC滤波送入MCU口,调理后的电压计算公式为ucBusVol = R105/Sum(R98+R99+R100+R101+R102+R103+R106) *(Bus+ - Bus-)。

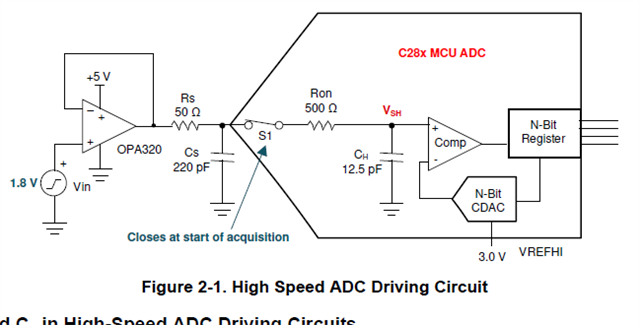

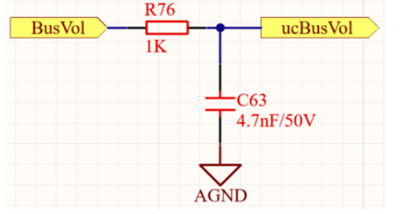

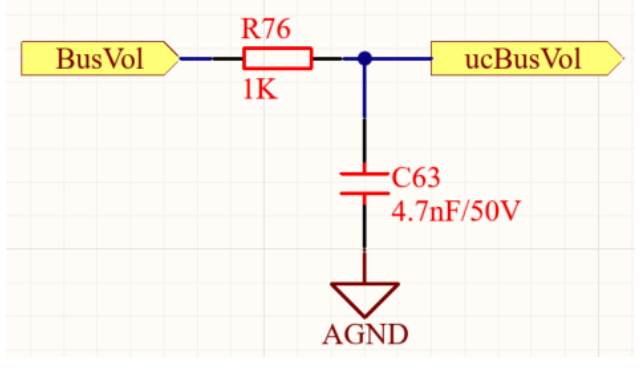

另外,根据Joseph的描述我看了section 16.13.2关于ACQPS计算的描述,有个问题想问一下,下图中Rs和Cs对应我们所用的采样线路里是最后一级RC滤波参数吗,也就是右图所示的参数。如果是的我我代入公式计算,对应的ACQPS应该是13,目前我们设置的是10。好像并不是Joseph所说的差很多。后面我会更改ACQPS值验证一下是不是这个问题。但我们一般采样线路里会放多级RC滤波,这个时候Rs和Cs是只考虑靠经MCU端口那级的参数吗?请帮忙继续问一下,谢谢!

感谢您对TI产品的关注!为更加有效地解决您的问题,我们建议您将问题发布在E2E英文技术论坛上(https://e2e.ti.com/),将由资深的英文论坛工程师为您提供帮助。