我想使用四线制SPI(STE、CLK、O、I)的FIFO实现两个28377D之间的全双工通讯,但是两个板子接收到的数据均不是我发送的,我使用示波器进行了检查,发现master发出的信号是正常的slave发出的信号是异常的,它将master发过来的一些数据又发送了回去,导致两者接收都存在异常。

我的程序逻辑如下:主机使用CPUTimer做计数器触发SPI读写,从机用FIFOInterrupt触发来实现SPI读写初始化程序与中断程序如下:

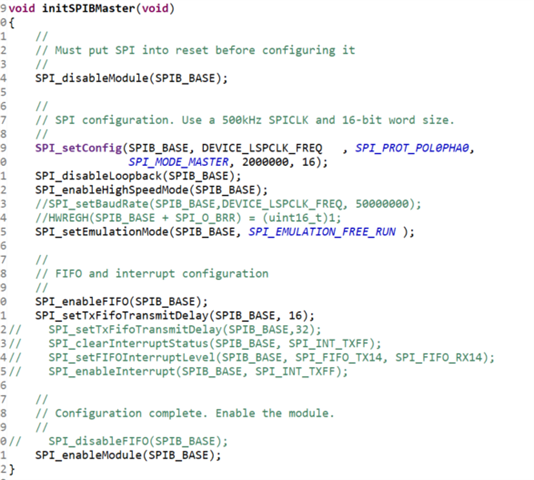

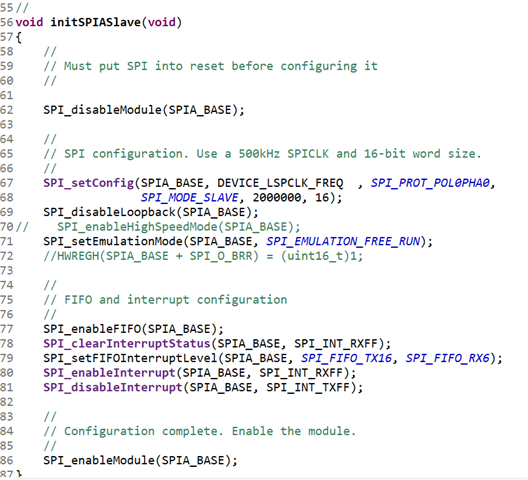

其中SPIA是从机,SPIB是主机。

我个人的理解是SPIA接收到的数据进入DAT寄存器后没有进入RXBUF反而又被发了出来导致整个程序紊乱,我想知道有没有什么方法可以改善这种情况,期待您能回复

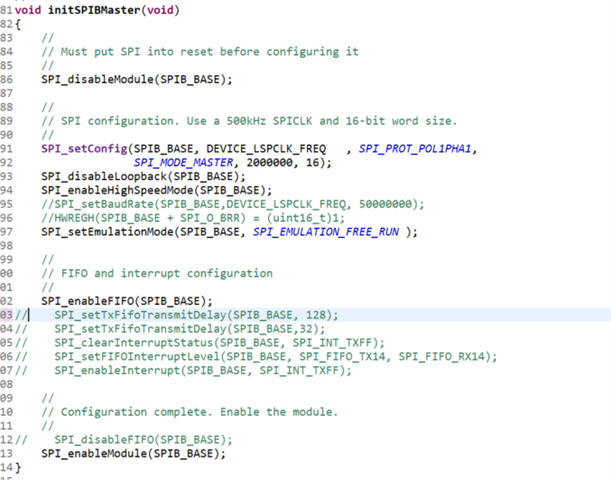

这是SPImaster的初始化过程

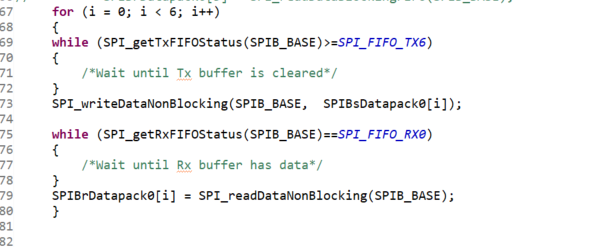

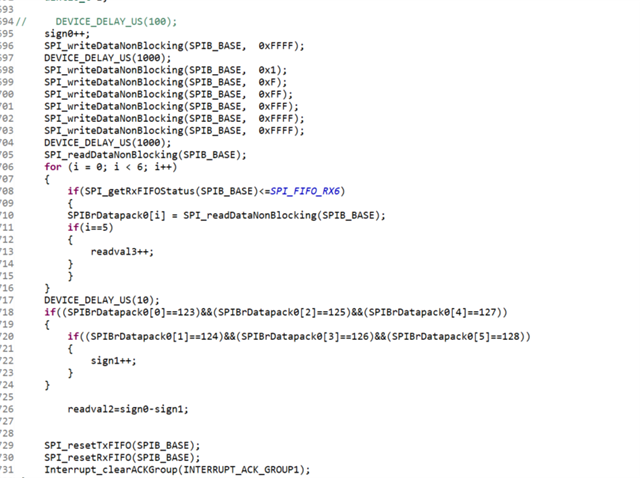

这是SPImaster的初始化过程 这是主机的发送程序,我通过一个定时器定时触发该程序,通过delay实现发送接收

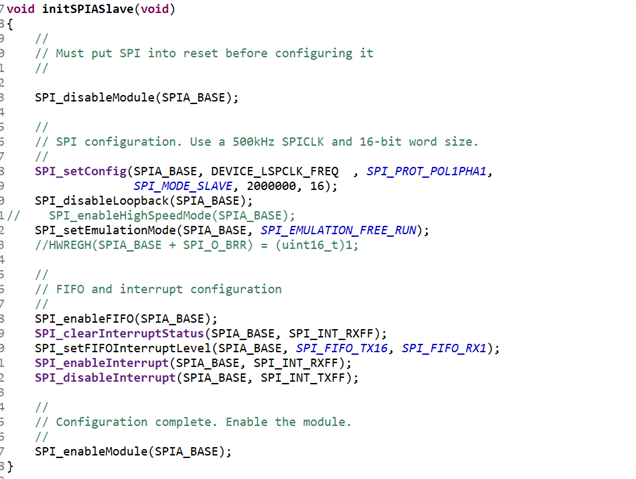

这是主机的发送程序,我通过一个定时器定时触发该程序,通过delay实现发送接收 这是SPIslave的初始化程序

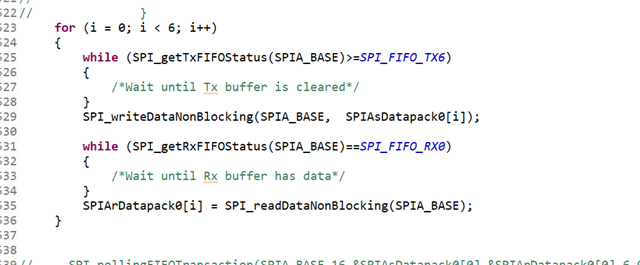

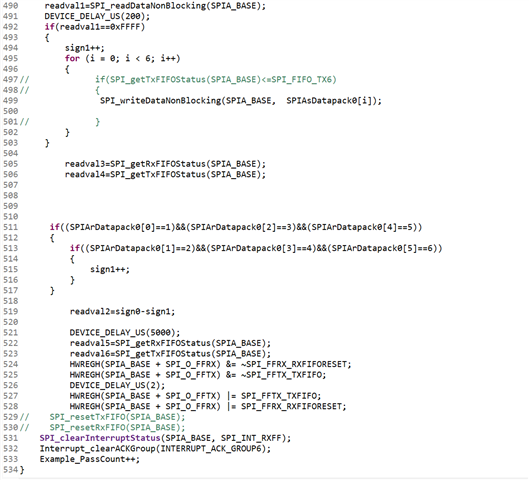

这是SPIslave的初始化程序 这是SPIslave的接收中断程序,同样的使用delay来实现接收与发送的配对。

这是SPIslave的接收中断程序,同样的使用delay来实现接收与发送的配对。