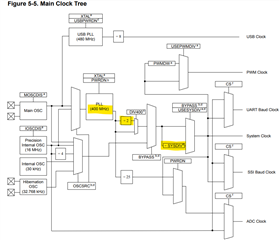

外部晶振 与 锁相环 PLL 以及 分频系数之间的关系说明在哪份文件中有说明?

TivaWare TM Peripheral Driver Library User's Guide 说明文件中 有个 20M 的设计例程,如下

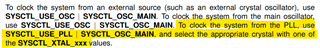

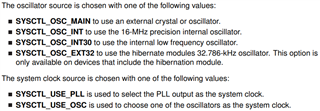

SysCtlClockSet(SYSCTL_SYSDIV_10 | SYSCTL_USE_PLL | SYSCTL_XTAL_4MHZ |SYSCTL_OSC_MAIN);

20M 是这样计算的吗?4 * 50 / 10,如果是,下面的晶振设置计算结果又是多少呢?

SysCtlClockSet(SYSCTL_SYSDIV_2_5 | SYSCTL_USE_PLL | SYSCTL_OSC_MAIN |SYSCTL_XTAL_16MHZ | SYSCTL_INT_OSC_DIS);

不可能是 320吧,因为最大文档说明是 80M