Other Parts Discussed in Thread: DRV8706-Q1, DRV8262, DRV8705-Q1

尊敬的TI团队:,

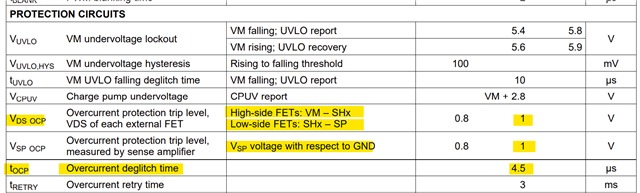

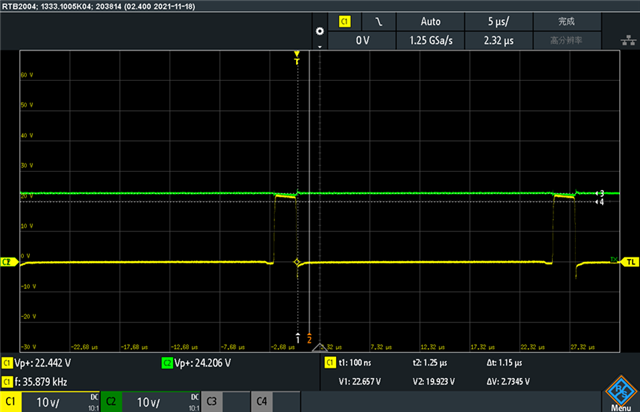

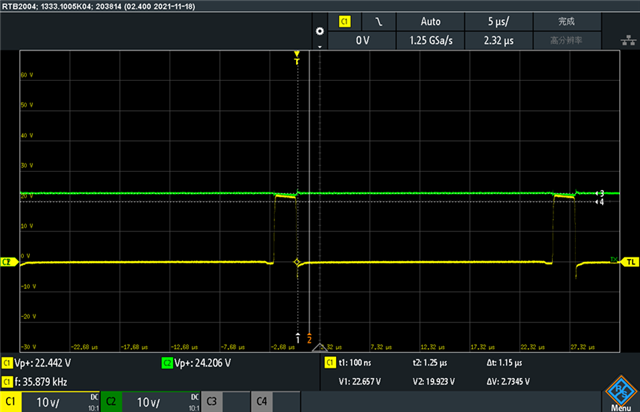

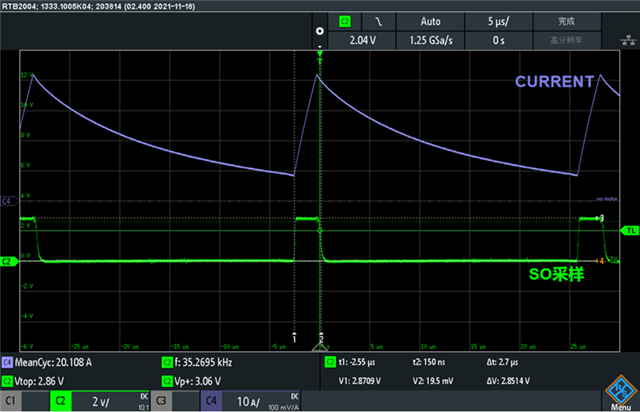

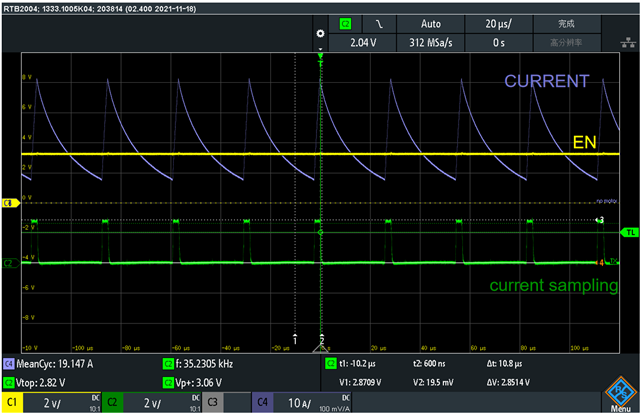

最近,我们的DRV8701芯片出现了以下故障,我们尝试将电机两极短路,此时尖峰电流可达到40A(设计的限流值为8A),出现尖峰电流的频率是35KHZ,而这时nfault引脚还是高电平,没有报错关断输出。

我们尝试更换了不同的电源和电池得到的现象都一致。

目前有以下两个问题:

(1)为什么出现尖峰电流的频率是35KHZ?

(2)为什么在超过硬件限流后nfault引脚还是高电平?

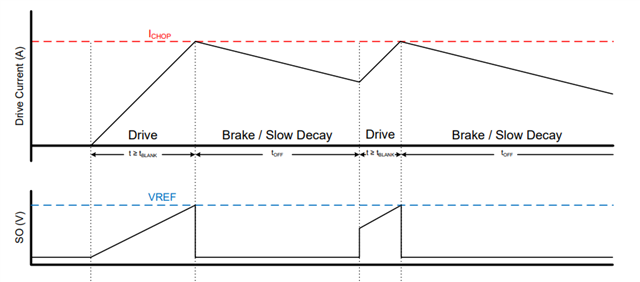

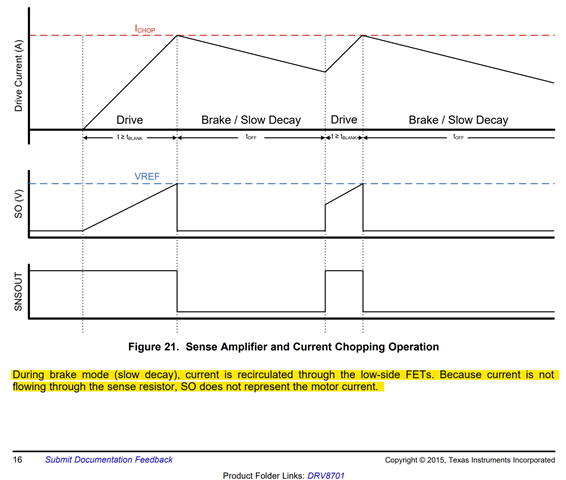

pic1

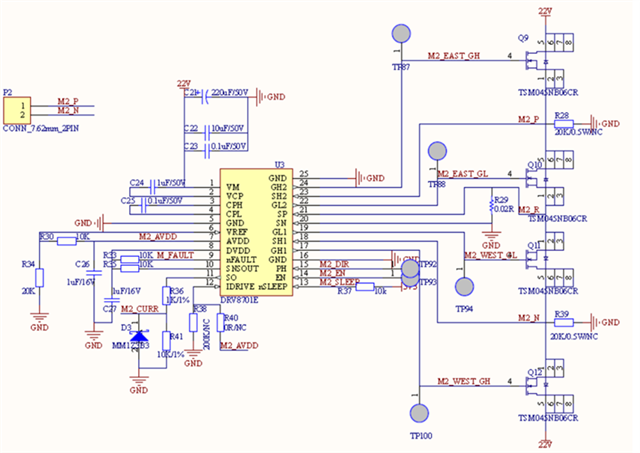

pic2

pic1为电流波形,pic2为设计的原理图。请问为何会出现这种现象?谢谢!