1.Nfault的引脚检测波形异常, 上拉电阻是10K,, 无其他分路泄放回路。

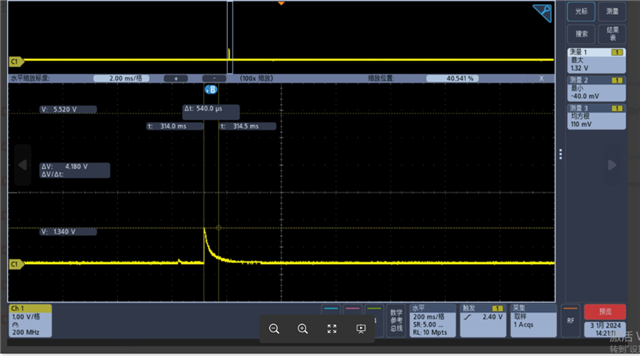

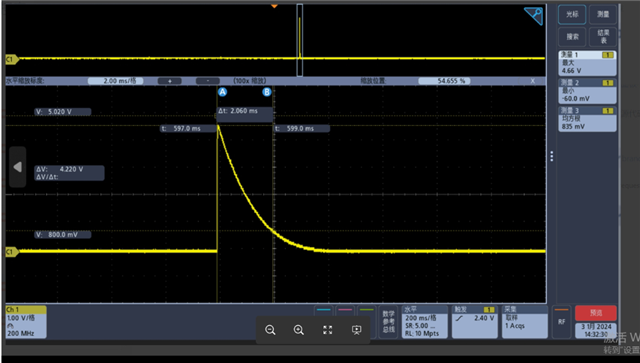

2.Disable的引脚 上下电存在误脉冲

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

1. 您的意思是10kΩ上拉对吧? 是只有一个低电平脉冲还是多个脉冲? 这些脉冲与禁用脉冲相关吗?

2. DISABLE 引脚是如何驱动的? 通常这是由 MCU 驱动的 GPIO。从 DISABLE 到 GPIO 引脚是否有串联电阻?DISABLE 引脚在内部从 DVDD 5V 拉高。当 VM 关闭时,DVDD 也会在 VM 达到 UVLO 时关闭。您能否分享原理图并描述工作电压?

板子是H版还是S版? 我们使用 S 版本 EVM,尝试了多个开/关周期,但没有看到意外的行为。也没有在 DISABLE 引脚上看到任何脉冲。

是什么情况下促使您抓取此波形?驱动程序没有按预期工作吗?最好通过查看 nFAULT、DISABLE 行为来了解尝试调试的其他问题。

怀疑您的问题可能来自驱动 DRV8873 的 MCU。这原因您排除过吗?能否断开DRV到MCU的所有外部连接并抓取波形?如果您能够像我们一样抓取 nFAULT、VM 电源和由 nFAULT 触发的 DISABLE 引脚,则可以帮助我们查看事件顺序并进行诊断。

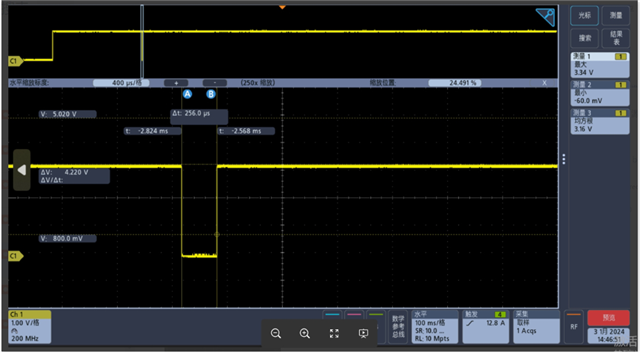

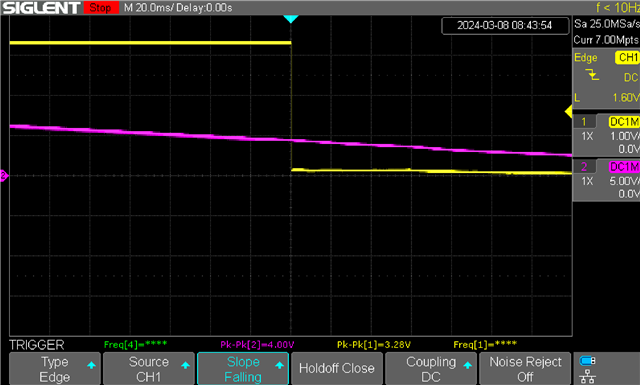

关闭 nFAULT 抓取电源。 黄色是 nFAULT,粉色是 VM。

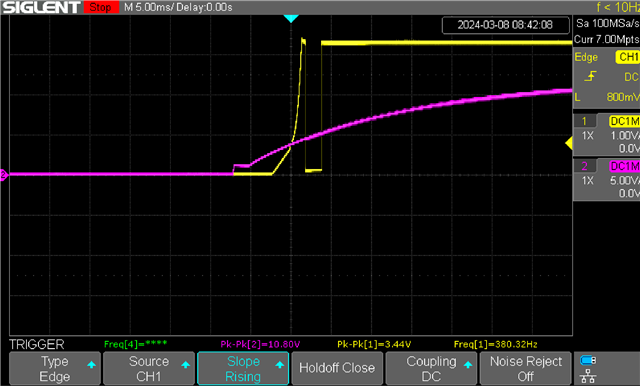

打开 nFAULT 抓取电源。黄色是 nFAULT,粉色是 VM。您可以看到,功率上升至最低工作电压以上,但 < UVLO nFAULT 较低,而当 VM > UVLO nFAULT 较高时,正如预期的那样。 这可以一致地再现。