TI Experts,

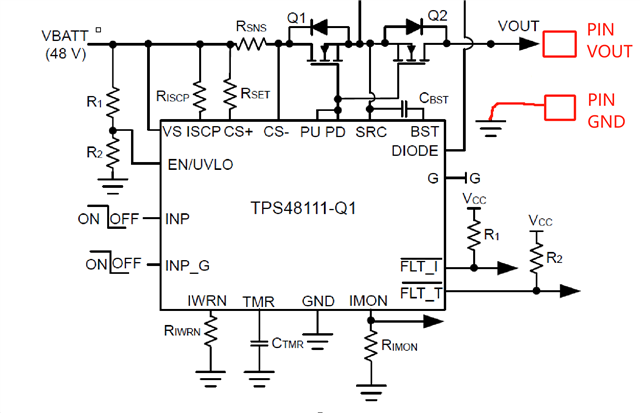

您好,我使用TPS48110驱动背靠背NMOS管,用作电池PACK外部充电通道的断路器,电路基本和规格书中的附图类似(没有预充电电路,EN通过GPIO控制,VOUT和GND之间没有电容)。我想请教一下,当INP为低,MOS断开时,Vout和GND之间,是不是即使短路也没关系?在我们的使用场景中,VOUT和GND会暴露在产品外部,产品有IP67的防水要求,当测试防水时,就相当于VOUT和GND短路。

从我目前测试的结果看,当MOS断开时,将VOUT和GND短在一起是没什么问题的。但我想再确认一下。

另外,将MOS断开有2种方式,

(1)将EN拉低,同时将INP拉低,让TPS48110处于不工作状态。但担心GS电压会处于不稳定状态

(2)将EN拉高,将INP拉低,芯片工作,但MOS断开

用于实现上面的功能(VOUT和GND短路时不会有问题), 请问这两种方式,更建议哪一种?

谢谢!