大家好,请大家帮忙分析解答一下下面的问题:

现象描述:tps65001用于tms320dm8168的电源轨道,电源轨道顺序为3.3V,1V_AVS,1V_CON,1.8V_D,1.8V_A,1.5V,0.9V。该电源轨道需要tps65001中的DCDC模块输出1.8V_D,LDO1模块输出1.8V_A,LDO2模块输出0.9V。断开负载情况下测试电源轨道电压均正常后(0.9V没有用,暂时不使能),调试电源轨道的上电顺序发现1.8V_D和1V_CON之间的时间间隔为600ms,而实际需求为0-50ms,测试1.8V_D和1.8V_A之间的时间间隔为200ms,实际需求0-10ms。

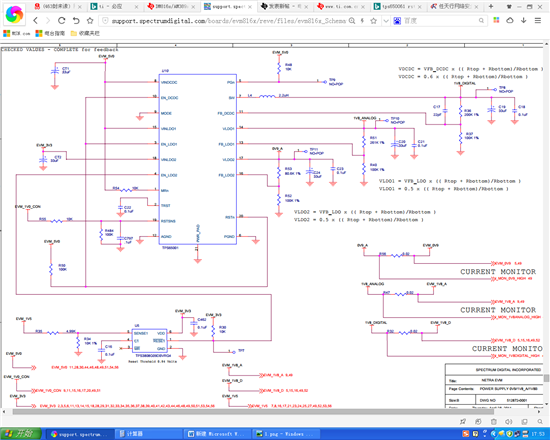

tps65001中的1.8V_D和1.8V_A的EN_DCDC、EN_LDO1由1V_CON控制,具体电路如下图所示(完全参照TI DM816x/AM389x 评估模块原理图设计),实测RST和EN_DCDC、EN_LDO1端电压为0.99V(根据tps65001数据手册可知EN_DCDC、EN_LDO1的Vih最小为1.2V—参考数据手册Electrical Characteristic),RST和EN端的0.99V与1V_CON之间的时间间隔为29ms。

根据tps65001数据手册可知RST引脚输出由VINDCDC、MR、RSTSNS两端的电压决定(参考数据手册Table1),实测板卡上的VINDCDC、MR电压为5V,RSTSNS电压为0.99V,输入均正常。

有什么原因会导致RST和EN端的电阻拉低呢?

输出电压正常,时间间隔不正常(甚至是1.8V_D和1.8V_A之间)是否是由EN端电压不正常导致的呢?有什么办法可以解决么?