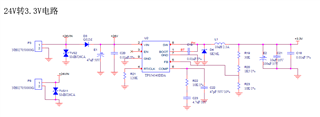

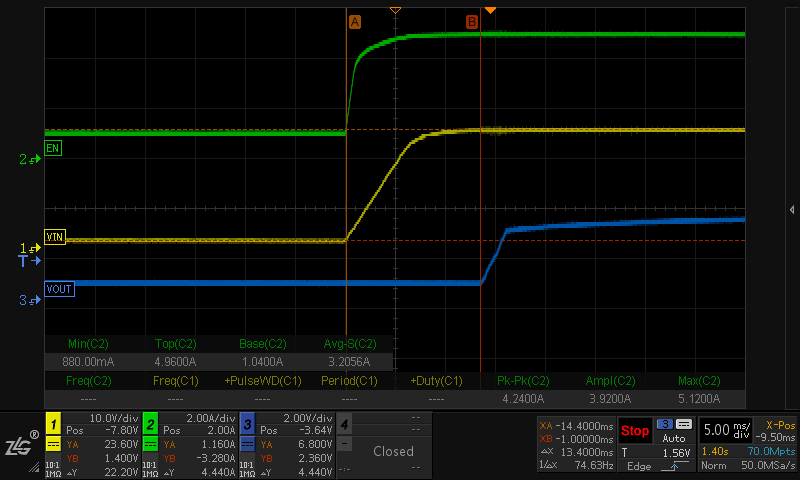

上图是电路原理图,C19为0.1uF。按上图测试上电时序(空载下)时,输出电压和输入电压启动间隔13.4ms(下图).记得以前测试时上电间隔都在几ms

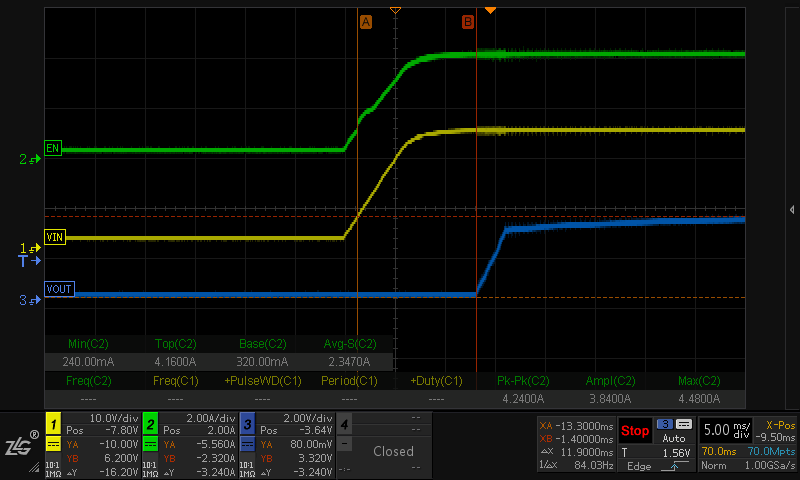

之后在EN和VCC之间接470K电阻,EN和GND之间接100K电阻,上电时序(空载下)如下图。输出电压依然未受EN控制。

请问TI工程师这种情况是怎么引起的呢?该怎么解决?谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

HI

除软起动影响输出电压上升,你可以用EN脚控制输入和输出的时间间隔,设计上输入通过电阻给到EN,然后EN接一个电容到GND,这样EN脚电压缓慢上升可以改变启动的时间间隔。

另外不同的输出电容,也应该可以影响输出的电压的上升速度。

Hi

EN电容大小要看你的时序控制,取太小启动快,取太大启动慢,具体可以依据测试来确认。

如果你采用分压电阻(分压电阻通过输入电压分得的电压给到EN脚)即可实现当输入电压大于Vstart时就启动。这样控制比较EN脚加电容好,因为芯片内部本身有上拉电压源。

HI

对照datasheet: https://www.ti.com.cn/cn/lit/ds/symlink/tps54340.pdf 28页8.12.1.2.8的计算方式来确认一下你的设计。(这里的描述比较清楚,看一下你按设计要求是否和参数一致)