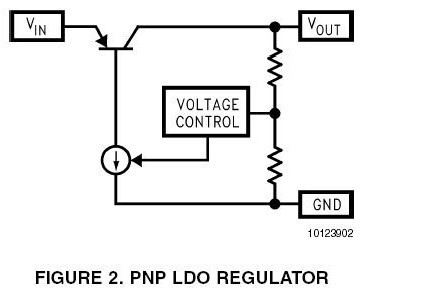

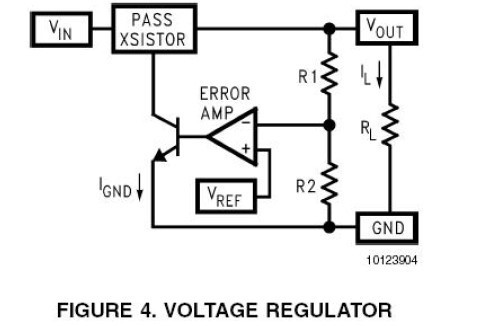

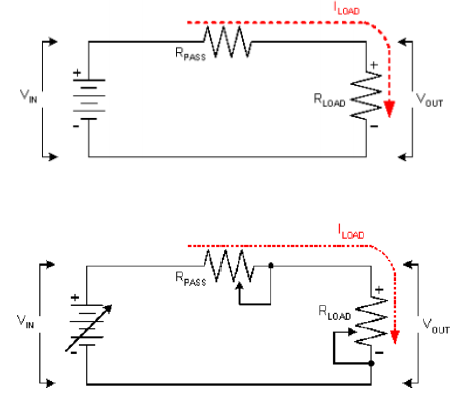

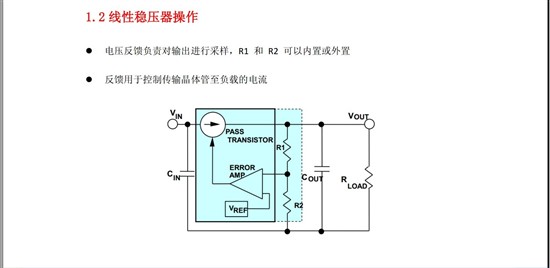

线性稳压器的工作原理是采用一个压控电流源以强制在稳压器输出端上产生一个固定电压,控制电路连续监视(检测)输出电压,并调节电流源(根据负载的需求)以把输出电压保持在期望的数值。

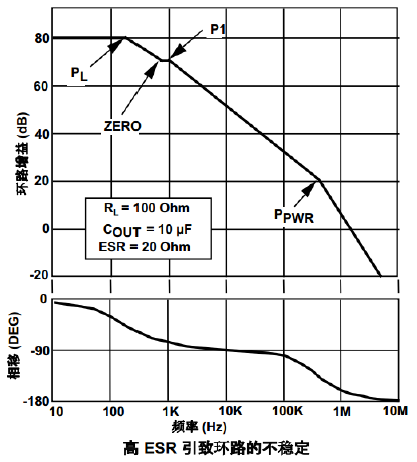

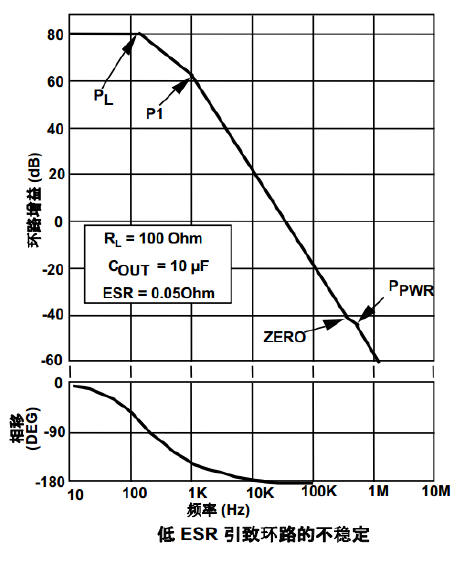

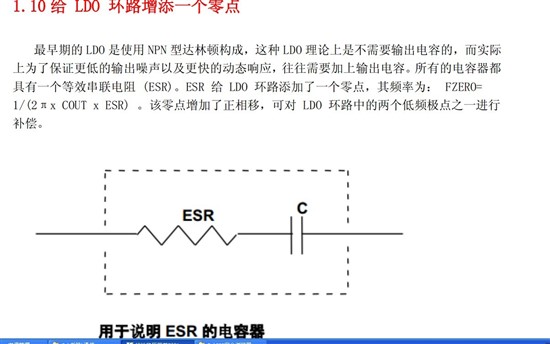

电流源的设计极限限定了稳压器在仍然保持电压调节作用的情况下所能供应的最大负载电流。输出电压采用一个反馈环路进行控制,其需要某种类型的补偿以确保环路稳定性。大多数线性稳压器都具有内置补偿功能电路,无需外部组件就能保持完全稳定。

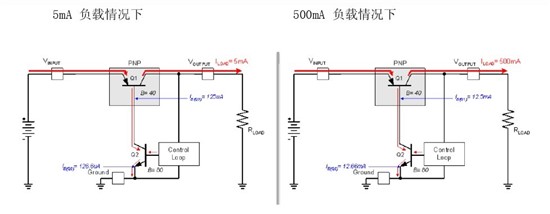

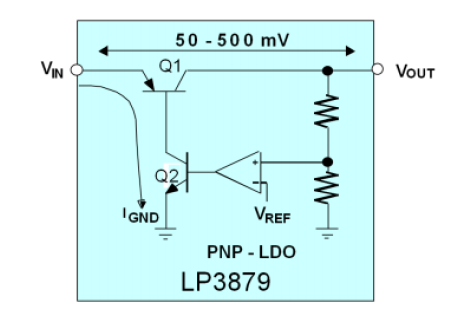

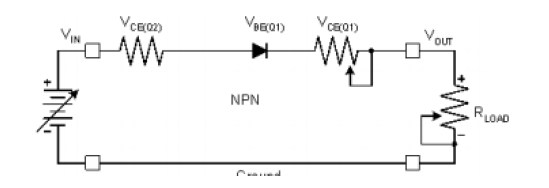

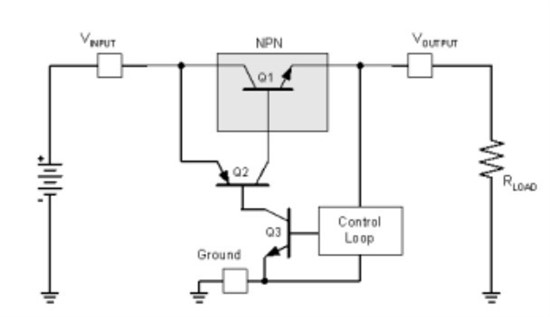

《线性稳压器基础知识》电子书共分为二章,第一章线性稳压器基础知识,讲述了最基础的线性稳压器知识理论,第二章线性稳压器的分类,讲述了NPN型的LDO、PNP型的LDO、NMOS型的LDO、PMOS型的LDO这四种不同线性稳压器的特性、架构图、功率损失的简单模型、传输元件,以及驱动电流与低/高负载电流的关系。