TI的工程师,您们好!我有两个问题请教,希望能尽快得到你们的指点!

问题1:

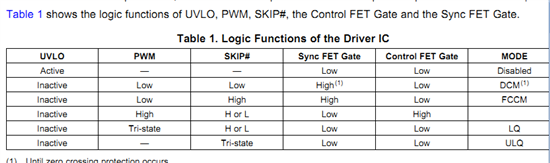

CSD97376Q4M的PWM端口支持三态输入,逻辑功能表如下:

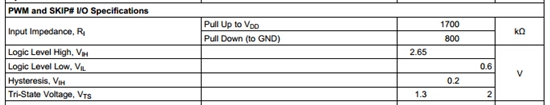

测试时,csd97376的供电为5V,半桥FET两端加的电压为6V,SKIP#端口上拉为5V,PWM控制信号有函数发生器提供。pwm为5V信号时,控制管和同步管可以正常的开通。当我想关断两个管子时,我给的PWM信号高电平为2V,低电平为1.4V,此时控制管的管压降为1.5V,同步管的管压降为4.5V。然而,继续切换至正常的5V pwm信号,两个管子的压降没有变化。掉电重启后,再给5V pwm信号,两个管子正常开通与关断。请问是什么原因?

假如 两管正常的开通与关断定义为状态1,两管均封锁定义为状态2。我的目的是利用PWM端口或者SKIP#端口 在状态1与状态2之间自由切换。请问如何做到?

问题2:

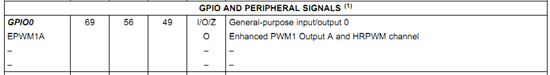

假如能解决问题1,即我的目的是利用PWM端口或者SKIP#端口 在状态1与状态2之间自由切换。当我采用TI的dsp型号为TMS320C2803X时,如何达到在状态1与状态2自由切换的目的。CSD97376Q4M的驱动PWM来自epwm模块,如下:

PWM功能时只有输出特性;该特性下,应该只能有高电平、低电平的脉冲方式输出吧,是否能呈现高阻特性?