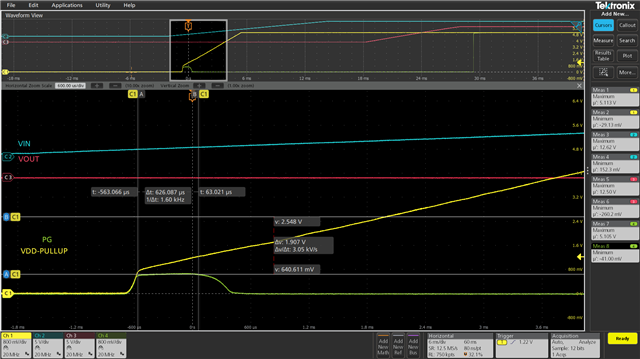

(在验证TPS25984 Evaluation Module (EVM)时,发现pg信号有较长时间拉高)

关于对TPS25984的测试,

一,其中电压监测点分别为:

- VDD_Pullup :TP24

- PG:TP20

- VIN:TP5

- VOUT:TP6

二,具体操作是:

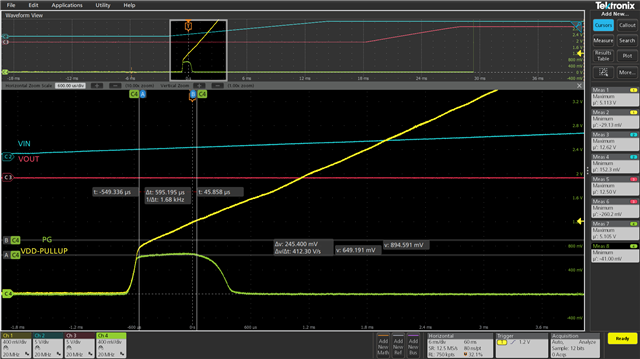

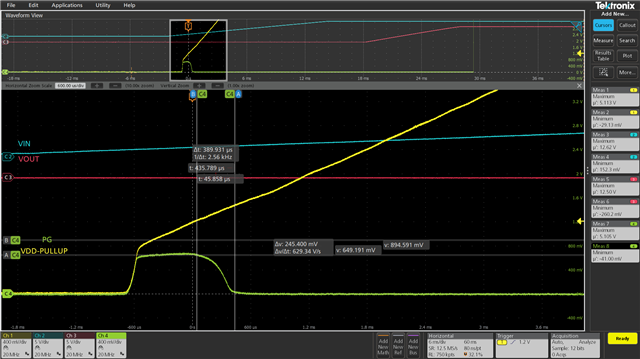

在输出端不抽载,然后给VIN电压12V,在power up的过程中发现PG会有一个上冲(如“power up”图),详细波形(如“T1”图)以及展开放大波形(如“T1_1”图),

想要了解一下对于T1过程中,PG出现如此长时间平台的原因是什么?以及T2过程的原因?