想用隔离驱动驱动mos,但是pspice for ti仿真显示OUT和VSS之间没有输出,但是如果把VSS1和VSS2电位设置为0就能正常输出驱动信号,请问是什么原因?

想用隔离驱动驱动mos,但是pspice for ti仿真显示OUT和VSS之间没有输出,但是如果把VSS1和VSS2电位设置为0就能正常输出驱动信号,请问是什么原因?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

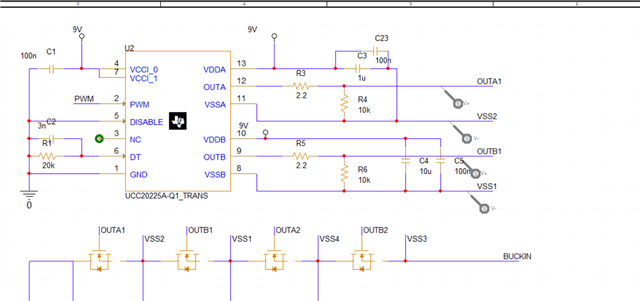

想用隔离驱动驱动mos,但是pspice for ti仿真显示OUT和VSS之间没有输出,但是如果把VSS1和VSS2电位设置为0就能正常输出驱动信号,请问是什么原因?

想用隔离驱动驱动mos,但是pspice for ti仿真显示OUT和VSS之间没有输出,但是如果把VSS1和VSS2电位设置为0就能正常输出驱动信号,请问是什么原因?

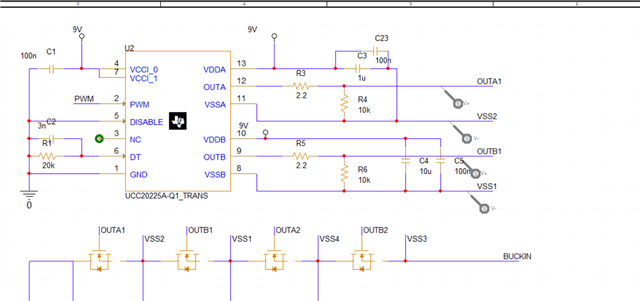

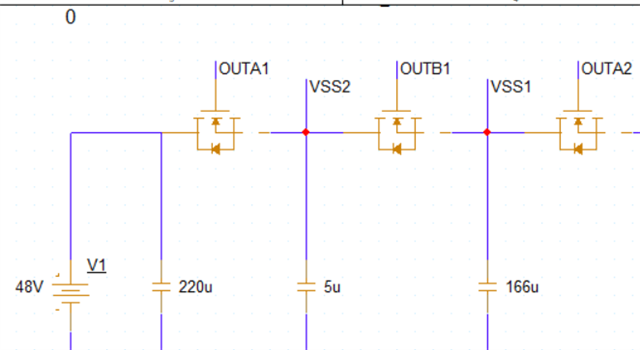

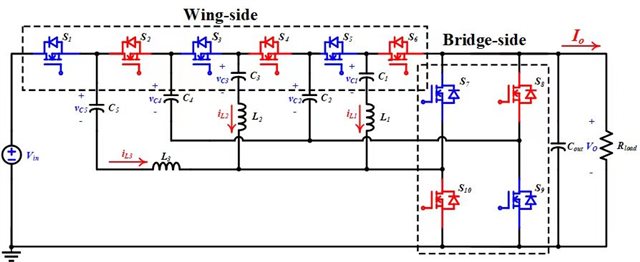

我的意思是就是两个mos管都是不接地的,不像那种半桥,如果是半桥我就用的正常的自举驱动,但是这种要用隔离驱动,但是没有输出驱动信号

Hi

datasheet给出的测试电路也是将VSS1和VSS2短在一起的。所以仿真应该是默认这样的连接(非半桥式的连接)。

你的实际电路能放上来看看吗?

,就是这样的,第二张图是整个的原理图,那我是需要把VSS1和VSS2短接吗??

,就是这样的,第二张图是整个的原理图,那我是需要把VSS1和VSS2短接吗??

Hi

没有看到类似的设计电路(TI这边没有类似的电路),一般来做要么都接地,要么就是半桥式的连接、