1、PIN3 EN是否可如此设计,需要控制负载的上电及下电;

2、功率限制主要作用是限制哪个的功率?在实际应用中是如何启作用的?

3、DV/DI是用作缓启动上电吗?GATE直接接个电容对地是否可以?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好:

1、PIN3 EN是否可如此设计,需要控制负载的上电及下电;

根据datasheet显示理论上可以这样接(给EN管脚供电),但是您用负载电压输出做EN的使能,负载输出的不稳定可能影响使能。这个可能影响到您稳定运行。综上说明官方不建议您这样接。

2、功率限制主要作用是限制哪个的功率?在实际应用中是如何启作用的?

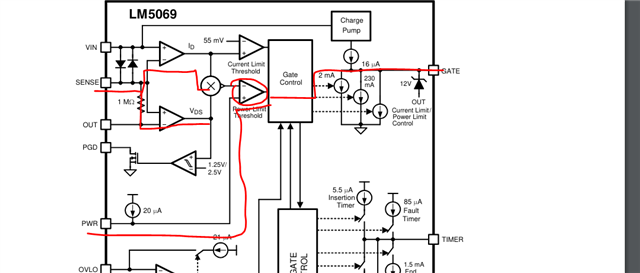

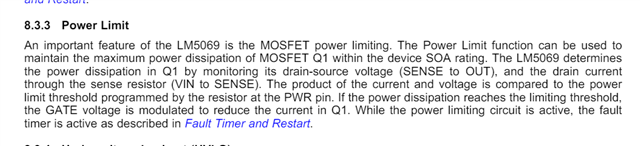

根据datasheet上的说明是通过Sense和power管脚搭配控制输出功率。

以上是示意图,一下是datasheet中的详细说明。

3、DV/DI是用作缓启动上电吗?GATE直接接个电容对地是否可以?

我想您是想问dv/dt是吗?

DV/DT控制通常用于限制负载上电时的电压上升速率(即电压对时间的导数),以减少浪涌电流和电磁干扰(EMI)。然而,在LM5069的文档中,并没有直接提到DV/DT控制作为一个特定的功能或引脚。通常,这种控制可能通过外部电路实现,如使用RC网络来限制电压上升速率。

GATE引脚接电容:

直接将GATE引脚接个电容对地可能不是最佳实践,因为这可能会影响MOSFET的栅极驱动性能。GATE引脚是MOSFET的栅极驱动输出,它需要根据负载和系统的具体需求来仔细设计。如果需要在启动过程中实现缓启动,可以考虑在GATE引脚和MOSFET栅极之间使用适当的RC网络或其他缓启动电路。