各位TI专家:

1. 4引脚WDI被拉高时(到VCC),或者拉底(到GND),为何1引脚输出不是稳定的低电平,而是再高低电平之间变化?

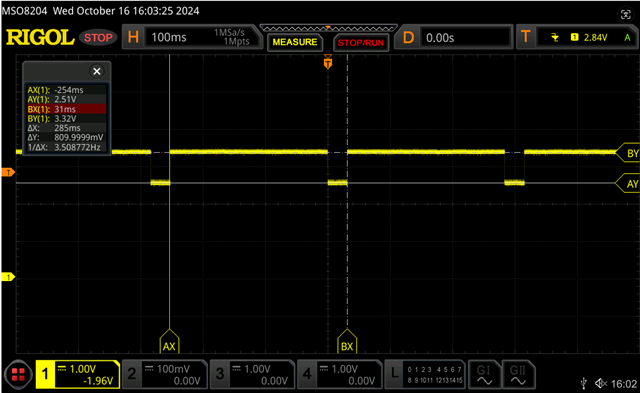

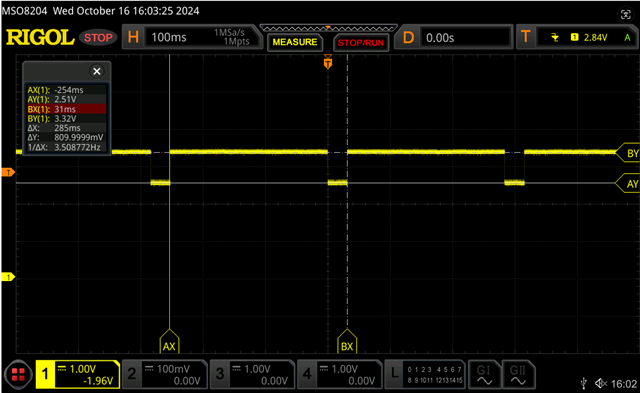

2. WDI引脚拉低时,1引脚输出,连接到了TI的或门芯片(SN74AHC1G32TDBVRQ1)的输入引脚上,但是此时1引脚电平的低电平无法在0V电位,这可能是什么原因导致的,具体波形如下:

如果要避免出现这个问题,应该如何操作?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

各位TI专家:

1. 4引脚WDI被拉高时(到VCC),或者拉底(到GND),为何1引脚输出不是稳定的低电平,而是再高低电平之间变化?

2. WDI引脚拉低时,1引脚输出,连接到了TI的或门芯片(SN74AHC1G32TDBVRQ1)的输入引脚上,但是此时1引脚电平的低电平无法在0V电位,这可能是什么原因导致的,具体波形如下:

如果要避免出现这个问题,应该如何操作?

您好

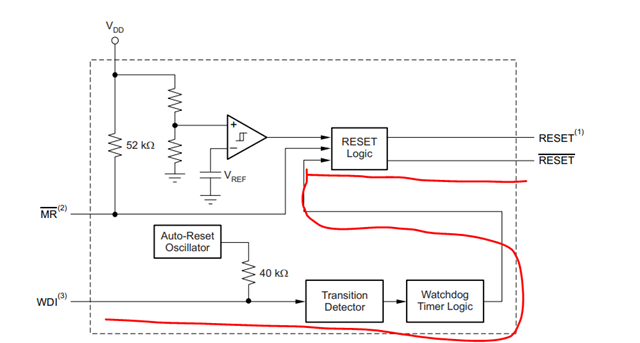

1. 4引脚WDI被拉高时(到VCC),或者拉底(到GND),为何1引脚输出不是稳定的低电平,而是再高低电平之间变化?

reset会受到WDI的拉高或拉低影响,至于为什么不是稳定低电平,因为在WDI在高或低的状态一段时间后,reset会被置位,当reset被置位后,WDI由于您的拉低或拉高没有改变状态,一段时间后又会将reset置位。具体说明请参考datasheet的第10页以及管脚定义都有说明。

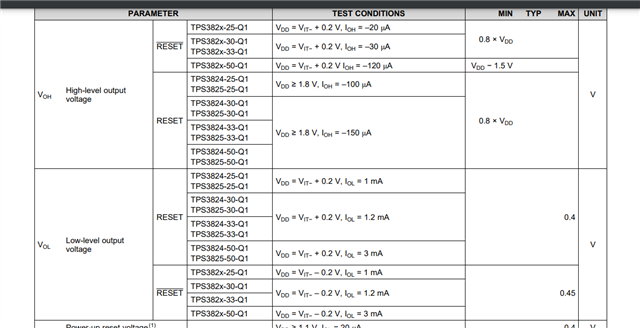

2. WDI引脚拉低时,1引脚输出,连接到了TI的或门芯片(SN74AHC1G32TDBVRQ1)的输入引脚上,但是此时1引脚电平的低电平无法在0V电位,这可能是什么原因导致的,具体波形如下:

这是官方测试reset的高低电平的范围,没有表明reset低电平必须是0V。官方给出的也是在一定的测试条件下的高低电平范围。