I have just been exposed to TMS320C6748 recently.I now want to write an SPI SLAVE program to receive FPGA data.I found these few sentences in section 28.2.7 of the data manual:

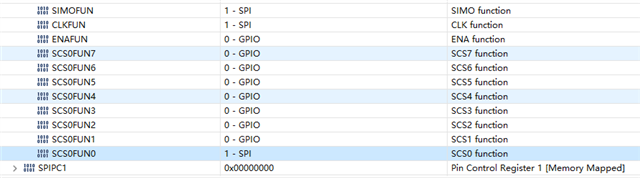

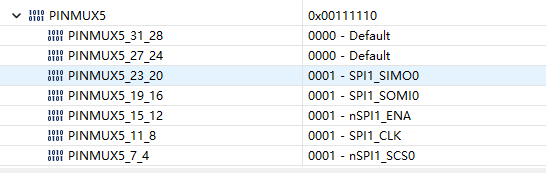

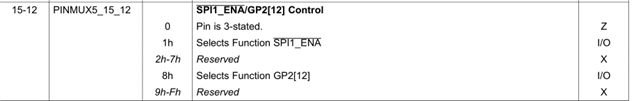

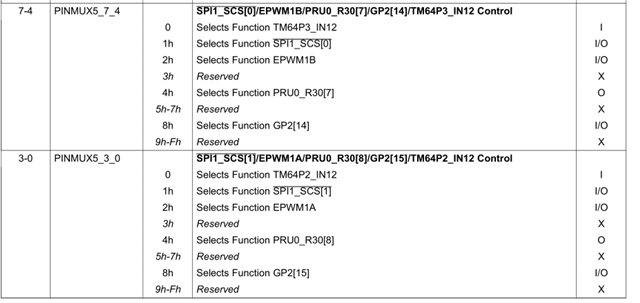

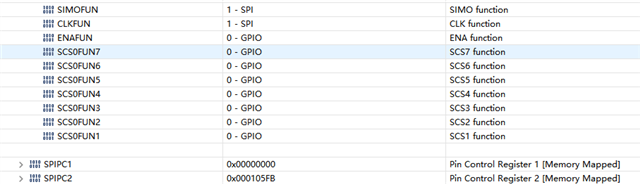

“ In SPI slave mode, the SPIx_SIMO and SPIx_CLK pin output buffer is in a high-impedance state and the SPIx_SOMI pin output buffer is enabled.”

How should I set it to look like a description?

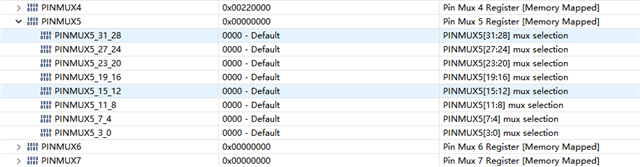

and:"In slave mode with 3-pin option, CPU writes to SPIDAT0[15:0] or SPIDAT1[15:0] makes the slave ready to transmit. CPU writes to the configuration bits in SPIDAT1 (not writing to SPIDAT1[15:0]) do not make the

slave ready to transmit."

I would like to know the difference and connection between SPIDAT1 [15:0] and SPIDAT1.

I really need your help. Thank you.