Other Parts Discussed in Thread: DAC38RF80

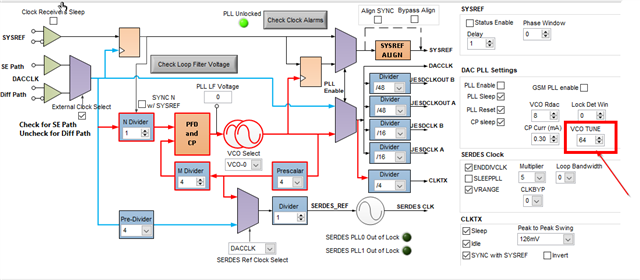

1. Use the DAC PLL clock as the serdes PLL reference signal (both DAC cores are enabled and configured in the same way):

a. The basic configuration is as follows:

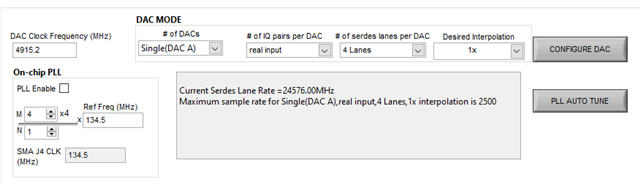

DAC CLK = 6G.

interp = 12.

L-M-F-S_HD = 4-2-1-1-1.

line rate = 5G.

DACCLK pad input 250MHz.

PLL_M = 6.

PLL_N = 1.

rate = half(01), MPY = 10.

MPY = 10.

b. The problem is described as follows:

First, the DACCLK pad is selected as the reference clock input to the serdes PLL and the DAC38RF90 outputs the signal correctly;

Secondly, while using the clock of DAC PLL as the reference signal of serdes PLL on the basis of the same project, then DAC38RF90 has no signal output and tx_sync is always 0. where SERDES_REFCLK_DIV is set to 6.

Therefore, please tell me, is there any other additional setting needed to select the clock signal of DAC PLL?

2. Use VCO_1 to generate the DAC core clock, use DACCLK as the reference clock for the SERDES PLL, and no signal output from DAC38RF90 (both DAC cores are enabled and configured in the same way).

c. The basic configuration is as follows:

DAC CLK = 9G.

interp = 12.

L-M-F-S_HD = 4-2-1-1-1.

line rate = 7.5G.

DACCLK pad input 187.5MHz.

PLL_M = 12.

PLL_N = 1.

rate = Full(00), MPY = 10.

MPY = 10.

The problem is described as follows:

tx_sync[0] is 0, tx_sync[1] = 1, however, there is no signal output from DAC38RF90 channel 1.

Therefore, there is the following question:

1. Do I need any other additional settings to use VCO_1?

2. Is there any additional setting needed to use the clock signal of DAC PLL as the reference clock of serdes PLL?