Other Parts Discussed in Thread: CC2642R

您好,非常感谢解答我一下几个问题。

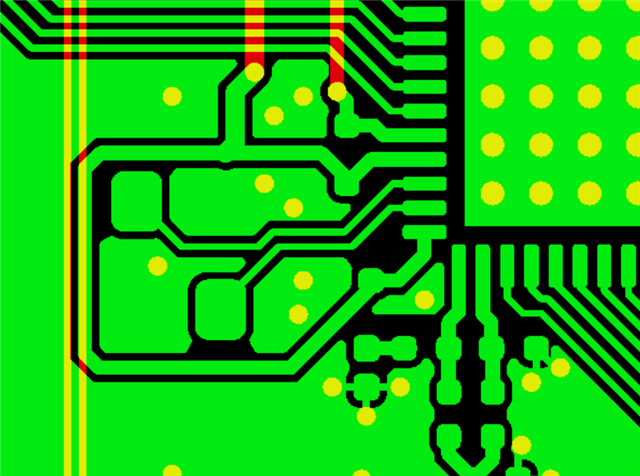

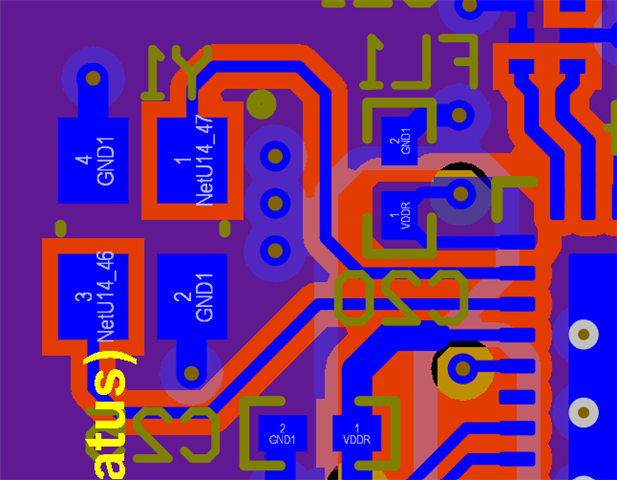

1)2640r2f,ti官方出的视频教程里支出,晶振需要被VDDR包裹,而不是平常设计的被地包裹,请问这是什么原理?另外其实有参考设计中也没有VDDDR包裹或GND包裹。

2)晶振下面要有一个完整的地平面,但是很多设计中要求晶振下面挖空,防止寄生电容问题?

3)对于YFV信号的封装,需要打过孔,那么晶振是否可以放到芯片的另一层?对于这样的情况晶振应该怎样处理。

4)射频部分电路信号是不是不必须在一条直线上?

5)为什么用带宽很高的胶棒天线,相距2m,环境蓝牙有十个左右。依旧会存在丢包,是不是ble就一定会存在丢包? 而在空旷的户外,几乎无蓝牙,可以做的5-6m不丢包。它受蓝牙环境影响这么大吗?

6)cc2642R不能设置外部偏置电路吗?