一、引言

随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着传输速率的升高而越来越突出。对于8Gbps及以上的高速应用更应该注意避免此类问题,为高速数字传输链路提供更多裕量。本文针对PCB设计中由小间距QFN封装引入串扰的抑制方法进行了仿真分析,为此类设计提供参考。

二、问题分析

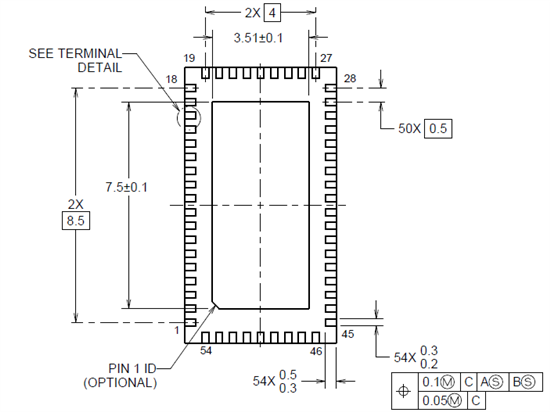

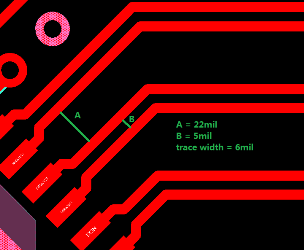

在PCB设计中,QFN封装的器件通常使用微带线从TOP或者BOTTOM层扇出。对于小间距的QFN封装,需要在扇出区域注意微带线之间的距离以及并行走线的长度。图一是一个0.5 pitch QFN封装的尺寸标注图。

图一 0.5 pitch QFN封装尺寸标注图

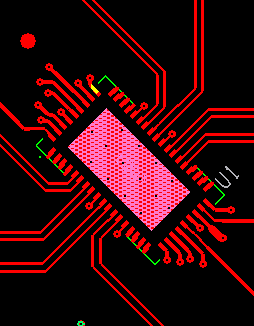

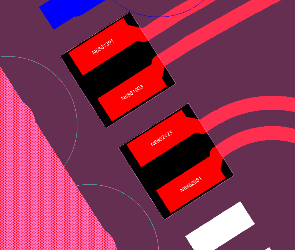

图二是一个使用0.5mm pitch QFN封装的典型的1.6mm 板厚的6层板PCB设计:

图二 QFN封装PCB设计TOP层走线

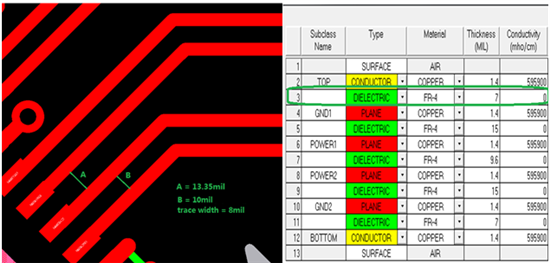

差分线走线线宽/线距为:8/10, 走线距离参考层7mil,板材为FR4.

图三 PCB差分走线间距与叠层

从上述设计我们可以看出,在扇出区域差分对间间距和差分对内的线间距相当,会使差分 对间的串扰增大。

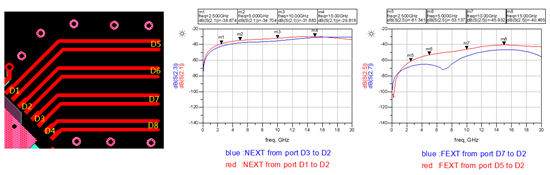

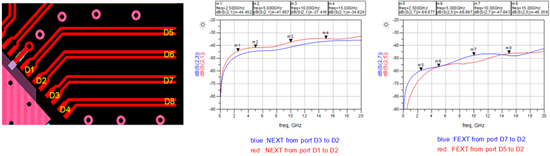

图四是上述设计的差分模式的近端串扰和远端串扰的仿真结果,图中D1~D6是差分端口。

图四 差分模式端口定义及串扰仿真结果

从仿真结果可以看出,即使在并行走线较短的情况下,差分端口D1对D2的近端串扰在5GHz超过了-40dB,在10GHz达到了-32dB,远端串扰在15GHz达到了-40dB。对于10Gbps及以上的应用而言,需要对此处的串扰进行优化,将串扰控制到-40dB以下。

三、优化方案分析

对于PCB设计来说,比较直接的优化方法是采用紧耦合的差分走线,增加差分对间的走线间距,并减小差分对之间的并行走线距离。

图五是针对上述设计使用紧耦合差分线进行串扰优化的一个实例:

图五 紧耦合差分布线图

图六是上述设计的差分模式的近端串扰和远端串扰的仿真结果:

图六 紧耦合差分端口定义及串扰仿真结果

从优化后的仿真结果可以看出,使用紧耦合并增加差分对之间的间距可以使差分对间的近端串扰在0~20G的频率范围内减小4.8~6.95dB。远端串扰在5G~20G的频率范围内减小约1.7~5.9dB。

|

|

2.5G |

5G |

10G |

15G |

|

原设计 |

38.874 |

34.704 |

31.883 |

29.818 |

|

紧耦合 |

44.452 |

41.657 |

37.416 |

34.624 |

|

优化结果 |

5.578 |

6.953 |

5.533 |

4.806 |

表一 近端串扰优化统计

|

|

2.5G |

5G |

10G |

15G |

|

原设计 |

61.341 |

53.137 |

45.932 |

40.465 |

|

紧耦合 |

59.667 |

56.697 |

47.643 |

46.359 |

|

优化结果 |

-1.674 |

3.56 |

1.711 |

5.894 |

表二 远端串扰优化统计

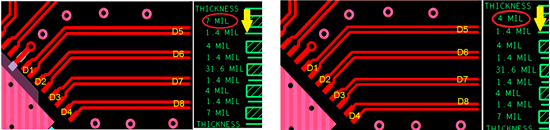

除了在布线时拉开差分对之间的间距并减小并行距离之外,我们还可以调整差分线走线层和参考平面的距离来抑制串扰。距离参考层越近,越有利于抑制串扰。在采用紧耦合走线方式的基础上,我们将TOP层与其参考层之间的距离由7mil调整到4mil。

图七 叠层调整示意图

根据上述优化进行仿真,仿真结果如下图:

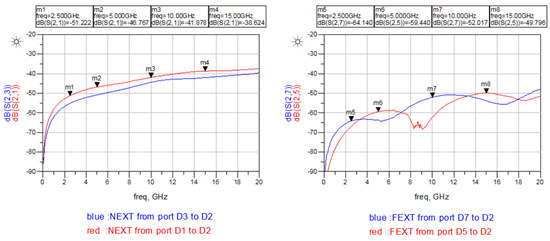

图八 叠层调整后串扰仿真结果

值得注意的是,当我们调整了走线与参考平面的距离之后,差分线的阻抗也随之发生变化,需要调整差分走线满足目标阻抗的要求。芯片的SMT焊盘距离参考平面距离变小之后阻抗也会变低,需要在SMT焊盘的参考平面上进行挖空处理来优化SMT焊盘的阻抗。具体挖空的尺寸需要根据叠层情况进行仿真来确定。

图九 叠层调整后QFN焊盘阻抗优化示意图

从仿真结果可以看出,调整走线与参考平面的距离后,使用紧耦合并增加差分对之间的间距可以使差分对间的近端串扰在0~20G的频率范围内减小8.8~12.3dB。远端串扰在0~20G范围内减小了2.8~9.3dB。

|

|

2.5G |

5G |

10G |

15G |

|

原设计 |

38.874 |

34.704 |

31.883 |

29.818 |

|

紧耦合 |

44.452 |

41.657 |

37.416 |

34.624 |

|

紧耦合+减小与参考面距离 |

51.222 |

46.767 |

41.878 |

38.624 |

|

最终优化结果 |

12.348 |

12.063 |

9.995 |

8.806 |

表三 近端串扰优化统计

|

|

2.5G |

5G |

10G |

15G |

|

原设计 |

61.341 |

53.137 |

45.932 |

40.465 |

|

紧耦合 |

59.667 |

56.697 |

47.643 |

46.359 |

|

紧耦合+减小与参考面距离 |

64.141 |

59.44 |

52.017 |

49.796 |

|

最终优化结果 |

2.8 |

6.303 |

6.085 |

9.331 |

表四 远端串扰优化统计

四、结论

通过仿真优化我们可以将由小间距QFN封装在PCB上引起的近端差分串扰减小8~12dB,远端串扰减小3~9dB,为高速数据传输通道提供更多裕量。本文涉及的串扰抑制方法可以在制定PCB布线规则和叠层时综合考虑,在PCB设计初期避免由小间距QFN封装带来的串扰风险。

TI公司的产品DS125BR820、DS80PCI810等芯片都采用了体积小并且利于散热的QFN封装。您可以在www.ti.com/sigcon查询更多应用于server、storage以及telecom等领域的高速数据传输的repeater和retimer产品。

其他相关资源

- TI的DS125BR820 40GbE QSFP+信号调理参考设计

- TI的DS80PCI810 PCIe-Gen3卡参考设计

- TI的在线仿真设计工具Interface WEBENCH® Designer