作者:Wayne Liu

Abstract

FPD Link 器件广泛的应用于汽车影音娱乐以及ADAS系统中高清视频数据的传输。本文主要总结了FPD Link 串行、解串芯片的主要功能模块的基本工作原理以及其在链路中的作用,便于工程师们快速理解和应用FPD Link系列产品。

Contents

1..... FPD Link系统架构.............................................................................................................................. 2

2..... FPD Link 串行芯片架构介绍............................................................................................................... 4

2.1 视频接口...................................................................................................................................... 4

2.2 视频编码成帧............................................................................................................................... 4

2.3 时钟模块...................................................................................................................................... 5

2.4 I2C 控制模块................................................................................................................................ 6

2.5 反向数据通道............................................................................................................................... 6

3..... FPD Link 解串芯片架构介绍............................................................................................................... 6

3.1 自适应均衡电路(Adaptive Equalizer).......................................................................................... 7

3.2 CDR 模块..................................................................................................................................... 8

4..... 参考文献.............................................................................................................................................. 8

Figures

Figure 1. FPD Link典型应用框图.................................................................................................. 2

Figure 2. FPD Link信号结构.......................................................................................................... 2

Figure 3. FPD Link支持多种线束.................................................................................................. 3

Figure 4. FPD Link串行器典型的应用框图................................................................................... 4

Figure 5. DS90UB953-Q1前向通道帧结构.................................................................................... 4

Figure 6. DS90UB953-Q1对输入时钟抖动的要求......................................................................... 6

Figure 7. 反向通道帧结构............................................................................................................... 6

Figure 8. FPD Link解串器典型内部结构....................................................................................... 7

Figure 9. 高速信号眼图变化............................................................................................................ 7

Figure 10. CDR功能模块................................................................................................................. 8

Figure 11. CDR Jitter Tolerance..................................................................................................... 9

1. FPD Link系统架构

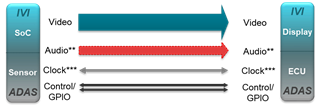

在车载影音娱乐和ADAS系统中,由于汽车空间结构的分配与限制,处理视频数据的SoC 与显示面板并不是布置在一起,获取图像的传感器与ECU也不在一起,这就需要把SoC 或者图像传感器输出的数据通过线束传递到显示面板或者ECU中,如Figure 1所示。视频数据一般都是RGB/HDMI/OLDI/DSI/CSI等并行的高速数据,如果将这些高速并行数据不经串化处理而直接传输,要求接插件的针数较多,尺寸较大,同时线束的重量、数量和成本都会比较大,线束的安装布局也会比较困难;同时,多条并行数据之间、数据与时钟之间的传输相位可能会出现明显的偏移,给系统带来传输误码;由于并行数据数量众多(有的多至30多位)且是单端信号,因此EMC设计难度也会大大增加;而且,并行数据只能单向传输,如果要实现系统的双向通信需要额外的反向传输通道。

Figure 1. FPD Link典型应用框图

TI 在业界率先提出了串行、解串器(FPD Link)的方案,通过把发送端的多条并行数据(包括视频和控制、语音等数据)转换成单条的串行数据,在接收端再把串行的数据转换恢复成显示面板或者SoC能接收的并行视频格式和低速控制信号, 如Figure 2所示,使上文中提到的所有问题都得以解决。

Figure 2. FPD Link信号结构

TI FPD Link除了能够完成视频数据的传输,它还有其他一些特点:

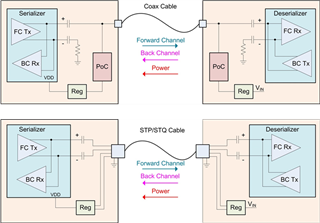

- POC (Power Over Cable)

-

由于视频数据经过了scramble 编码,空出了低频频段,系统可以利用视频传输线束的直流频段,向远端的摄像头供电,简化ADAS 系统远端摄像头的供电设计。

- 双向控制信号传输

-

类似于POC 的原理,FPD Link 器件可以利用视频传输中的空闲时隙,双向传送控制信号,实现诸如远端器件的寄存器访问、软件配置、显示器背光控制、触屏中断以及位置信息的上传等。

- 集成信号调理技术

-

在部分应用场景中视频源与接收端距离比较远,线束较长,信号幅度衰减较大。解串器中都集成了高速信号调理技术(Signal Conditioner), 如 Adaptive Equalizer, CDR 等模块,用于延长视频的传输距离。

- 支持多种视频线束

-

TI FPD Link 支持高速差分线束(HSD)和铜轴(Coax)电缆。灵活的视频线束选择,使FPD Link 适用于多种应用场景, 参见Figure 3。

- Figure 3. FPD Link支持多种线束

2. FPD Link 串行芯片架构介绍

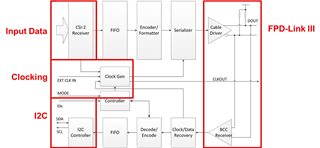

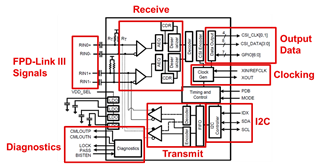

在视频数据的发送端是FPD Link 串行器(TX)。串行器主要包括了视频接口、格式编码器、串行器、时钟电路、控制电路以及反向通道恢复电路,框图如Figure 4。

Figure 4. FPD Link串行器典型的应用框图

2.1 视频接口

常见的视频接口有RGB、 OLDI、 HMDI、 DSI、 CSI、DP 等。一般一颗串行芯片只能支持一种视频接口,设计者需要根据SoC(IVI)或者Sensor/ISP(ADAS)提供的视频接口选择合适的串行芯片。Figure 4为DS90UB953-Q1的内部框图,视频接口为CSI-2,数据率为1.6Gbps/Lane, 一个CSI-2接口提供总共6.4Gbps的数据吞吐率,只要视频数据率低于这个最大吞吐率就可以被传输。

2.2 视频编码成帧

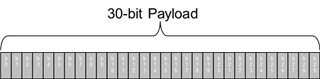

如下Figure 5为DS90UB953-Q1的输出帧格式。

Figure 5. DS90UB953-Q1前向通道帧结构

红蓝绿数据是真正的视频数据,灰色是GPIO/I2C/Audio/INT 信息,白色以及黄色是同步和DC balance 位。不同的FPD Link产品的这个字符串长度会有差异,91x产品为14bit, 933 是28bit, 935/953为40bit, 94x 为35bit。前向通道的数据速率不仅和帧长相关,也和视频数据的PCLK相关。以933为例:对于12-bit mode,把每三个像素的数据分发入两帧,每帧数据为28bits,所以线束中的数据率line rate = ƒPCLK × (2/3) × 28,如果取ƒPCLK = 100 MHz, line rate = (100 MHz) ×(2/3) × 28 = 1.87 Gbps;对于10-bit mode,把每两个像素分入同一帧中,每帧数据为28bits,则line rate = ƒPCLK/2 × 28;取ƒPCLK = 100 MHz, line rate = (100 MHz/2) × 28 =1.40 Gbps。

对于935或者953来说,每帧数据为40bits,每一帧里边可以包含4个CSI -2 端口输出的8bits,其它为GPIO/INT/I2S信息。对于synchronous mode,line rate = Ref_CLK × 160, Ref_CLK 为23~26MHz;对于nonsynchronous mode, line rate = Ref_CLK × 80, Ref_CLK 为 25~52MHz。

这些数据帧后续会经过串行器的8B/10B或者scramble扰码,实现数据的DC均衡,方便链路的AC 耦合传输,同时,数据经过扰码以后使得带宽范围变为[Line rate/20, Line rate/2],单位为Hz。

2.3 时钟模块

FPD Link发送方向的信号流向为:视频源模块以PCLK频率输出的并行信号,输入给加串器,然后经过加串器内部的8B/10B编码器或扰码器 (Scrambler),以更高速时钟进行并串转换,之后串行数据再经过驱动器 (Driver)发送出去。因为串行器把低速的并行输入数据串化到高速的串行数据,数据率提升很多倍,所以串行器需要从输入的低速时钟中通过PLL + VCO的方式生成一个高速时钟。

时钟模块主要是为整个系统提供参考时钟,确保系统同步工作。串行器的参考时钟可以有几个选择:

a. SoC视频接口提供的随路时钟; b. 本地提供的晶体或者晶振时钟;c. 从反向通道中恢复的解串器提供的参考时钟;d.芯片自身集成的时钟振荡电路。工程师选取芯片特定的参考时钟模式后,时钟模块会将相应的时钟分发到芯片的各个模块中,包括帧编码模块、串行器模块和锁相环,从而保证整个芯片乃至整个系统工作时钟源一致,避免FIFO的溢出和空载,也避免视频数据的行场、帧场同步信息紊乱。

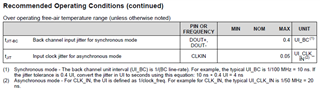

时钟模块是串行器很关键的一部分,它的抖动性能决定了串行器输出高速信号的质量。时钟模块是一个模拟部件,对输入参考时钟的抖动、电源噪声都比较敏感。设计者需要特别注意这部分的电路设计以及器件选型。Figure 6 是953对回传通道输入信号和CSI输入时钟抖动的要求。

Figure 6. DS90UB953-Q1对输入时钟抖动的要求

2.4 I2C 控制模块

FPD Link 器件除了可以被本地控制器通过I2C访问,还可以通过I2C访问对端的器件以及挂在对端器件上的其他器件,比如MCU、Image Sensor。在手册中,我们定义串行器为SER Device,解串器为DeSER Device,挂在SER/DeSER上的其他器件为Slave Device。当要通过SER 访问DeSER侧的Slave Device A时,在SER 设置Slave ID_x = Slave Alias ID_x = Slave Device A 的I2C地址Slave Alias ID_x即可。 这样SER就可以直接访问对端对应的Slave Device了。

2.5 反向数据通道

反向通道是TI 独有的专利技术(专利号US20120002573),是指与视频反方向的低速数据通道,即从解串芯片到串行芯片,用于传输GPIO/INT/I2C等控制信号。利用频分双工的原理,解串芯片把这些低速控制信号组成一个固定30比特帧长的数据帧,如Figure 7所示,并调制到一个固定的不随前向视频数据率的改变而改变的传输频率。为了减少反向通道对前向通道的频率干扰,反向通道采用了较低的传输频率:例如在953+ 954的应用中,当芯片配置在sync mode下,反向通道的速率是50Mbps;当芯片配置在non-sync mode下,反向通道的速率是10Mpbs;在933+954的应用中,反向通道的速率为2.5Mbps。954的反向通道还可以传送同步时钟,这样摄像头模块就可以不需要本地晶振,减少了自身的BOM成本。

Figure 7. 反向通道帧结构

3. FPD Link 解串芯片架构介绍

接收端(RX)解串芯片主要包括了信号调理模块(AEQ+CDR)、输出格式编码器、时钟模块、反向发送通道、芯片诊断模块等,如Figure 8所示。

Figure 8. FPD Link解串器典型内部结构

3.1 自适应均衡电路(Adaptive Equalizer)

高速视频信号从串行器传输到解串器的过程中经过PCB走线、连接器和线束,这些传输介质都会衰减信号幅度,增加信号噪声,而且频率越高,被影响的程度越大。 如Figure 9所示,串行器的输出数据的眼图为左边第一幅图所示,比较清晰、干净;经过传输线以后,眼图闭合,如中间第二幅图所示。为了补偿传输介质对信号的恶化,FPD Link 器件提供了Equalizer均衡器模块。这个模块放大补偿输入信号,且对信号高频部分补偿得更多,以此来部分抵消传输通道对信号的影响。通过Equalizer之后,输入信号的眼图重新张开,如右边第三幅图所示。

Figure 9. 高速信号眼图变化

由于FPD Link需要适应不同类型不同长度的线束,所以均衡器的高频增益值分多个等级,芯片会自动检测输入信号的质量,自适应地设置最佳的均衡值,这个自适应模块叫AEQ。该模块在解串器每次上电时做一次自适应补偿,所以即便线束存在老化、温漂、线束个体差异等实际差异时,AEQ 都能够自动选择出最佳的补偿等级。另外,技术人员也可以读取上电以后的AEQ 的补偿值,如果明显高于正常值,可以判断当前传输通道可能存在短路、松动、弯曲等异常情况。

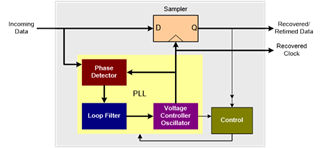

3.2 CDR 模块

典型的CDR(Clock Data Recovery) 电路的示意图如Figure 10所示,集成的锁相环电路锁定输入数据Incoming Data并输出降噪以后的较干净的同频率时钟Recovered Clock;同时这个干净时钟做为新的采样时钟,在Sampler上对输入数据重新采样并输出,从而达到滤除输入数据抖动、降低码间串扰、减少通道间串扰和恢复数据眼图的功能。

Figure 10. CDR功能模块

CDR电路最主要的功能就是滤除输入信号的固有抖动。在实际应用中,评价一个CDR电路的性能指标主要包括:

- Jitter Tolerance,抖动容限,指CDR在保证不失锁、无误码的情况下所允许的最大输入抖动

- Residual Jitter,残留抖动,指CDR恢复输出的数据中残留的固有噪声

- Jitter Transfer Function,抖动传输函数,指输出抖动和输入抖动的比值

CDR无法滤除输入信号环路带宽以内的近端噪声,而直接输出近端噪声,但这近端噪声不会影响CDR的锁定,所以在环路带宽之内,CDR的抖动容限可以很大;输入信号中大于环路带宽的噪声部分会被CDR的环路滤波器滤除,因此如果输入信号的带外噪声过大,会造成CDR无法及时追踪输入信号过大的频率变化,从而造成失锁和误码。

抖动容限和残留抖动是两个相互对立的参数,大的环路带宽,抖动容限较高但残留抖动较多;小的环路带宽,抖动容限较低但可以残留抖动较小。在实际应用中,技术人员需要在这两者之中取最适合系统的折中的、合理的环路带宽。

4. 参考文献

- DS90UB953-Q1datasheet (SNLS552C)

- DS90UB954-Q1 datasheet (SNLS570B)

- Exploring the Internal Test Pattern Generation Feature of 720p FPD-Link III Devices (SNLA132)

-

yinyin fan

-

取消

-

投赞成票

0

投反对票

-

-

登录以回复

-

更多

-

取消

-

Cherry Zhou

回复 yinyin fan

-

取消

-

投赞成票

0

投反对票

-

-

登录以回复

-

更多

-

取消

评论-

Cherry Zhou

回复 yinyin fan

-

取消

-

投赞成票

0

投反对票

-

-

登录以回复

-

更多

-

取消

子级