作者:Frank Qin

问题背景:

在IVI系统中,SoC-串行器-解串器-屏幕的链路中存在很多的干扰及未知因素。尤其是当下各类芯片基本都没有提供各类信号的并行输出,导致难以在串行链路中的各个点位分别抓取我们希望得到的数字信号,从而导致在整个系统出现不稳定或者时钟及脉冲信号不匹配时,我们无从下手去找到不匹配的点。

解决思路:

如果可以把串行信号或者“黑盒子”中的有意义的信号单独抓取出来,找到其中的“可变量”和“定量”,就可以比较简单的判断出链路中是否有哪个信号出现的偏差或抖动。

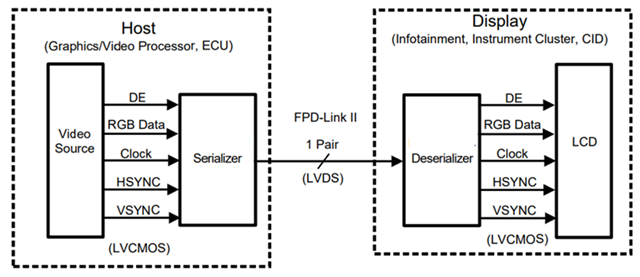

LVDS 可在并行和串行数据传输中工作。 在并行传输中,多个数据差分对同时承载多个信号,其中包括用于同步数据的时钟信号。 在串行通信中,多个单端信号被串行化为单个差分对,数据速率等于所有组合单端通道的数据速率。

因此,当我们需要分别分析各个数据的时候,并行数据传输的优势就比较明显了。

可做参考的四个信号:

PCLK(时钟信号)、DE(data enable数据使能信号)、Hsync(行同步信号)和Vsync(场同步信号)。

PCLK:在FPD-Link链路中,PCLK由SoC生成并发出,途径的FPD-Link SerDes芯片都参考此时钟信号。但目前的SoC和SerDes芯片都因为串行数据的传输格式而无法实际测量PCLK的数值。因此也无法确定SoC实际发出的PCLK是否和设置的理论值一致。因为链路上的SerDes芯片都是根据理论设置的PCLK值保持一致,所以一旦链路中的实际PCLK值有偏差,链路上的视频信号将会产生时钟偏差。

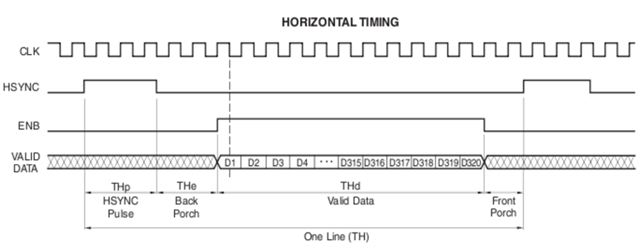

DE:顾名思义,DE信号是用于使能有效信号的,它用来区分有效视频数据(active data)和消隐信号(blanking)。由图1可以看出,DE信号仅在有效信号的区间内是高电平,其余均为低电平。因此,DE信号会由有效视频信号和消隐(包括Sync pulse、front porch和back porch)。

Hsync和Vsync:对于视频信号来说,每行图像信号扫描完之后都需要跳转至下一行,而Hsync也就是行同步信号就是每完成一行时候出现的一个用作提示的高电平。Hsync的周期可以直接理解为视频信号一行有效区加上消隐区的总脉冲周期。换句话说,Hsync就是每行的数据总和,不会受到时钟信号以及有效信号设置的影响,在整个链路中会保持一致。同理,Vsync是纵向的脉冲总和。

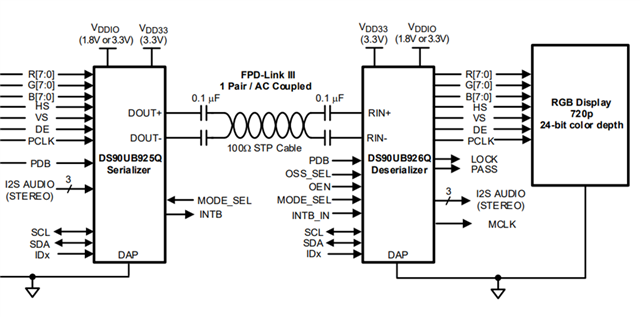

在TI的FPD-Link III代编解串器中,DS90UB926Q-Q1就是这样的一个输出模式。通过UB926的框图,可以看到输出的信号是分解出了上文提到的HS、VS、DE和PCLK数据。只需要在输出端用示波器或者分析仪抓取对应的信号即可。因此如果希望了解video source或者Sereializer在进入display之前的信号是否有异常或抖动,使用一个DS90UB926QEVM是最简单最直观的办法。

但有时无法替换掉deserializer或者我们需要把deserializer包含在被测试的链路中,下面会介绍一种原理一样的方式来分离出想要观察的HS、VS、DE或PCLK信号。

工具介绍:

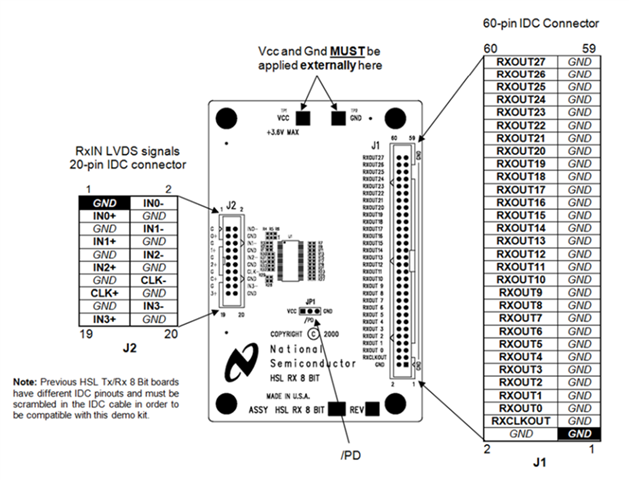

DS90CF386的EVM板(官网名称FLINK3V8BT-85)。

DS90CF386是FPD-Link的解串器,可以接收高达85MHz的LVDS信号输入。它的特点是可以做到并行的LVCMOS输出,如图所示,DS90CF386可以分别输出DE、RGB data、Clock、Hsync和Vsync数据给到接收端。这样的特性刚好可以解决我们新一代FPD-Link产品无法分别识别出这几个信号的问题。

DS90CF386共有ROUT[27:0]共计28个并行信号输出接口和一个专门的Clock output接口,其中24个作为24bits RGB信号输出,分为3组,每组8个。这24个输出接口应用于RGB666的信号格式,分别是模式下的24 color bits (R[8:0], G[8:0], B[8:0]),另外4个是对我们这个应用最关键的3 个控制信号(VS, HS and DE)以及一个CNTL信号。如上文提到的,VS, HS和DE是我们可以组为参考的重要标准。而在DS90CF386EVM板上,RXCLKOUT 作为了RCLK的输出引脚,可以直接作为引出CLK信号以作参考。

实际应用举例:

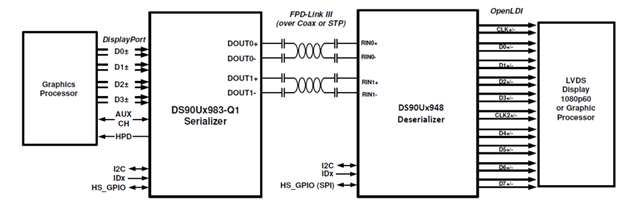

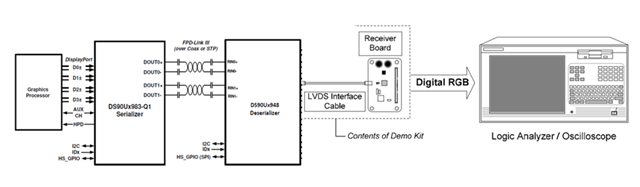

此系统为SA8155作为DP source,DS90UB983和DS90UB948作为FPD-Link编解串器的一个汽车中控屏架构。从8155主芯片发出的DP视频信号经过983和948最后到屏幕的过程中,我们都没有方便的测试点可以抓取这条视频信号的PCLK。因此当屏幕图像出现抖动的时候,我们无法得知何处的CLK时钟信号有偏差,即使知道8155发出的PCLK时钟信号和设置的理论值有偏差,我们也无法知晓具体偏差了多少以及调整的方向。此时,可以在948的LVDS输出后面接上一个DS90CF386 的EVM板,通过它把这个视频链路中的PCLK时钟信号抓取出来,通过和Hsync的对比确认PCLK是否有偏差并确定调整方向。

DS90CF386EVM板在使用时很简单,给VCC接上3.3V电源并接地后即可启动。因为作为LVDS输入的J2是micro USB接口,因此可能需要一些转接工具把948输出的信号连接至DS90CF386。以上连接完成后即可通过J1的输出抓取到这个视频信号通路里面的PCLK等数值。

通过这种方法获取的PCLK是链路中实际的像素时钟,可以通过和SoC以及串行器中设置的PCLK值进行对比,确认实际链路中的像素时钟是否和设置值有偏差以及偏差了多少。其中可以作为参考的一个重要指标就是Hsync值。如前文提到的,Hsync是不会受到时钟的影响,因此将Hsync作为周期性的参考基准是最为合适的。如果SoC或者整个系统会导致PCLK有不规律的抖动,此时单纯靠示波器显示出来的频率时难以判断的,因为不规律的抖动无法通过示波器的暂停或者触发等功能抓到。此时最有效的方法是使用示波器的无限余晖模式让PCLK波形不断叠加,如果没有不规则抖动,PCLK波形应当不断重叠在一起。

总结

随着汽车应用中需要传输的视频信号速率越来越高,DP/MIPI等协议逐渐成为主流,在这样一个完全由串行信号组成的系统中逐步拆解并定位可疑的异常点就需要一些可以破局的方法。本文即介绍了一种使用并行信号输出的解串器来分离各个信号以便分析的方法。