同步降压转换器已作为隔离式偏置电源在通信及工业市场得到认可。隔离式降压转换器或者通常所谓的 Fly-Buck™ 转换器,采用一个耦合电感器代替降压转换器电感器,用以创建隔离式输出以及非隔离式降压输出。每个隔离式输出只需一个绕组、一个整流器二极管和一个输出电容器。可使用这种拓扑以低成本的简单方式生成多个半稳压隔离式或非隔离式输出。

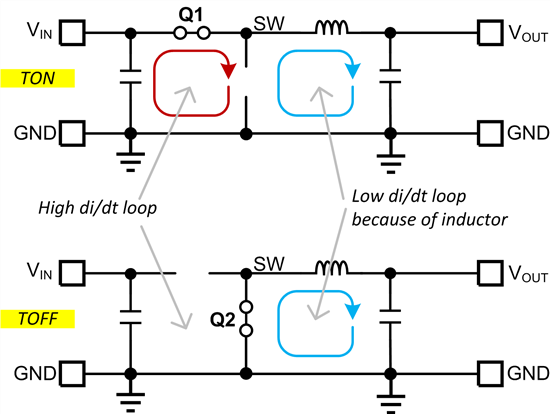

降压转换器和 Fly-Buck 转换器中存在一些主要电流差别。我们对降压转换器中的开关电流环路已经很熟悉了,如图 1 所示。包含输入旁路电容器、VIN 引脚、高低侧开关以及接地返回引脚的输入环路承载着开关电流。该环路应针对静音工作进行优化,达到最小迹线长度与最小环路面积。包含低侧开关、电感器、输出电容器以及接地返回路径的输出环路实际上承载着低纹波 DC 电流。虽然为实现低 DC 压降、低损耗和低稳压误差而让所有电流路径尽量最短非常重要,但该环路的面积并不像输入电流环路那么重要。

图 1. 降压转换器中的电流环路。VIN 环路为高 di/dt 环路。

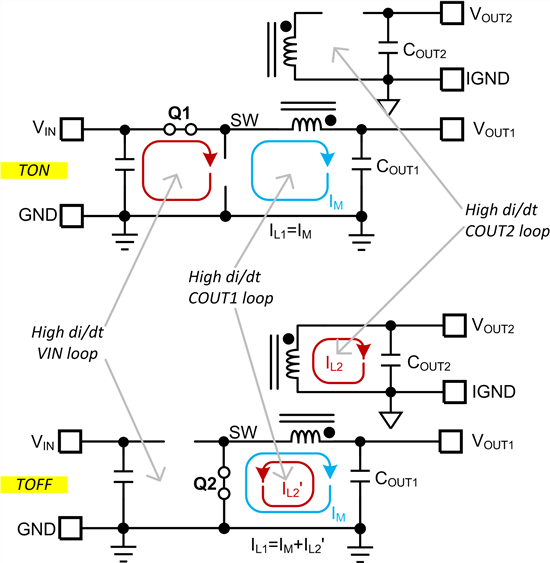

Fly-Buck 转换器的一次侧看上去与降压转换器类似,如图 2 所示。这里的 VIN 环路与降压转换器一样,也是高 di/dt 环路。然而,VOUT1 环路的电流与降压转换器有很大不同。除了一次电感器磁化电流外,该环路还包含来自二次绕组的反射电流。反射电流只含有其路径中耦合电感器的漏电感,因此 di/dt 明显高于电感器磁化电流。所以尽量减小 VOUT1 环路的环路面积也非常重要。同样的道理,包含二次电感器绕组、整流器二极管以及二次输出电容器的二次输出环路也需要最小化,因为里面有高 di/dt 电流流过。

图 2. Fly-Buck 转换器在一次侧有两个高 di/dt 环路。所有二次环路都是高 di/dt。

在布局 Fly-Buck 转换器时还需要记住:二次绕组也有一个开关节点。该二级开关节点 (SW2) 是高 dv/dt 节点,支持 VIN*N2/N1 的电压转换。因此,通常要让 SW2 迹线面积较小,才能防止其发出噪声。

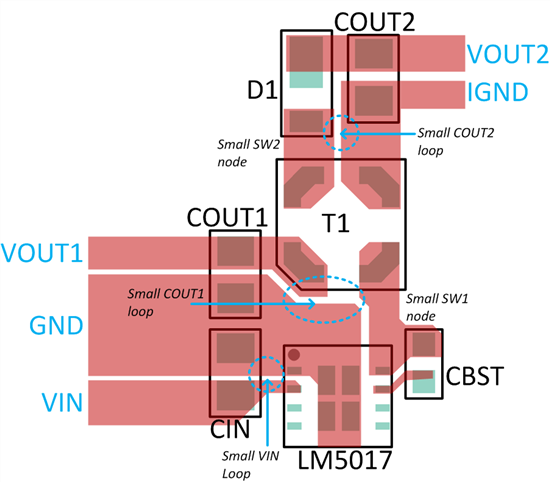

图 3 是融合本文指导内容的布局实例。与开关节点面积一样,一二次侧的高 di/dt 环路也可以进行最小化。

图 3.基于 LM5017 的 Fly-Buck 布局可对 di/dt 环路和高 di/dt SW1,2 节点面积进行最小化。

参考资料:

- 阅读应用手册:“设计隔离式降压 (Fly-Buck) 转换器”

- 观看视频:“LM5017 Fly-Buck 多输出演示”

- 在这里查看有关 TI 宽泛 VIN 产品的更多详情

- 阅读 How2Power 中的文章:“同步降压转换器为隔离式应用实现多偏置电轨及输入电压传感”

原文请参见: http://e2e.ti.com/blogs_/b/powerhouse/archive/2014/04/01/flybuck-pcb-layout-tips.aspx