作者:Aki Li

变频多相交错拓扑在大功率应用场景有广泛的应用场景,而采用数字控制时需要重点考虑PWM发波控制的灵活性和可靠性。本文介绍了在多相变频拓扑中使用新一代C2000的Type 4 EPWM 全局加载和一次加载功能的注意事项,并针对边界情况提出一种简单的解决方案。

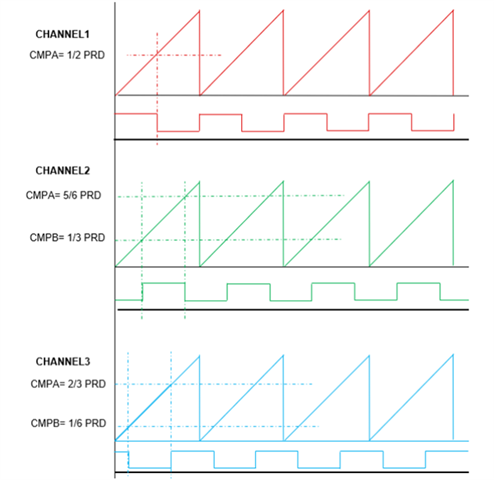

在应用文档Leverage New Type ePWM Features for Multiple Phase Control中介绍了针对多相交错拓扑的PWM 发波配置推荐方法,但由于相位寄存器TBPHS本身不支持影子模式,因此一般在实际变频拓扑应用中,不建议使用TBPHS来实现不同PWM模块之间的相位交错关系,而是利用不同PWM模块的CMPA/CMPB比较寄存器的大小关系来实现。例如,针对三相交错LLC, 应用文档Implement Three-Phase Interleaved LLC on C2000 Type-4 PWM推荐的PWM发波配置如图1所示,其中三路LLC对应的EPWM 模块选择同一个时基,图示只给出EPWMxA的发波动作配置,而EPWMxB通过死区模块以EPWMxA作为输入源在插入死区后产生。考虑到LLC是开关频率变化的拓扑,为了确保不同PWM模块的周期寄存器和比较寄存器的值在同一时刻点从影子寄存器生效到实际的PWM寄存器,需配合Type-4 EPWM的全局加载和一次加载功能。

图 1 三相交错LLC PWM配置

针对LLC的应用,一般建议将不同EPWM模块的周期寄存器TBPRD、比较寄存器CMPA/CMPB、死区寄存器DBRED/DBFED都选择使能全局加载功能,这样可以确保多个寄存器在设定的全局加载事件到来时在单周期全部加载完毕。此外,一次加载功能是指在手动刷新完毕所有EPWM寄存器后,使能一次加载开关寄存器GLDCTL2[OSHTLD],以确保在一次加载开关打开后,目标寄存器方可从影子寄存器生效,而且只刷新一次。由于每个PWM模块都有单独的GLDCTL2[OSHTLD]寄存器,建议采用EPWMXLINK[GLDCTL2LINK] 寄存器将其他的EPWM模块的关联到主相EPWM模块,从而只需要使能主相PWM模块的GLDCTL2[OSHTLD]寄存器,其他从相PWM模块的一次加载功能会同时打开。

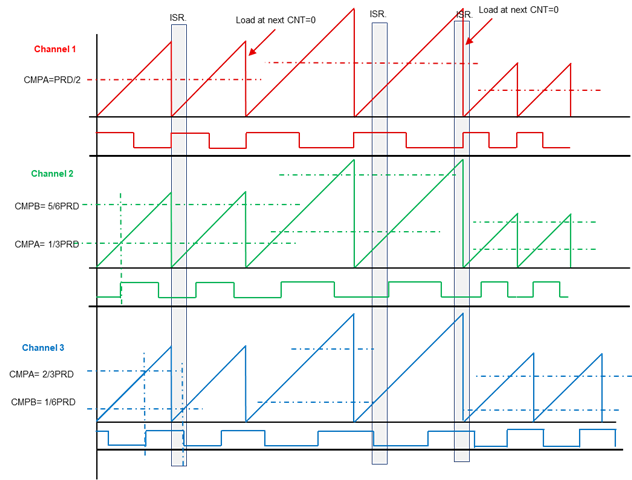

在大部分工况,通过以上机制可以规避多个PWM寄存器不同步刷新的风险,但仍需要注意如下的情况,当控制中断频率和开关频率不同步,且中断频率高于开关频率时,则有可能出现小概率事件,如图2 所示。假设在一个开关周期内触发两次中断,由于在第一次中断中使能了一次加载开关,则在第二次中断进行手动刷新PWM寄存器时,一次加载开关保持使能状态,如果在此过程碰到了全局加载事件(如CNT=0),就可能出现寄存器加载不同步的风险。图2中,假如在CNT=0前第三相PWM的周期没有及时更新写入,则在新的开关周期生效后,第三相PWM的频率和前两相的频率出现不同步现象。同样的情况,假设前后频率变化范围很大,频率增大后,如果对应的比较寄存器没有同步更新,甚至可能会导致在新的开关周期内无法产生比较匹配事件出现常高风险。

图 2 边界情况

为了规避此边界情况,如下参考代码提供了一种解决思路,以三相交错LLC的EPWM寄存器更新为例,当环路计算得到新的开关周期值后,在手动更新PWM寄存器的步骤中,增加一个判断条件,即如果当前时刻十分接近周期结束点,则在手动更新寄存器前插入一个固定的延时(延时时间取决于手动更新寄存器所需的时间),以确保手动更新寄存器的过程不会跨越全局加载事件。如下示例代码中,考虑到尽可能缩短手动刷新寄存器的时间,已将相关的比较寄存器的计算过程和寄存器的更新过程分开单独处理。

static inline void LLC_HAL_updatePWM(float32_t periodSet_pu)

{

static uint16_t tbprd_ticks = 0;

static uint16_t cmpa_1_ticks =0, cmpa_2_ticks = 0, cmpb_2_ticks = 0, cmpa_3_ticks = 0, cmpb_3_ticks = 0;

tbprd_ticks = LLC_PERIOD_MAX_TICKS * periodSet_pu;

cmpa_1_ticks = tbprd_ticks>>1; //phase 1 Compare A value

cmpa_2_ticks = tbprd_ticks*0.333333333; //phase 2 Compare A value

cmpb_2_ticks = tbprd_ticks*0.833333333; //phase 2 Compare B value

cmpa_3_ticks = tbprd_ticks*0.666666667; //phase 3 Compare A value

cmpb_3_ticks = tbprd_ticks*0.166666667; //phase 3 Compare B value

// Update the relevant PWM values for the actuation: TBPRD, CMPA, CMPB,

if(EPWM_getTimeBaseCounterValue(LLC_PRI1_PWM_BASE)< (EPWM_getTimeBasePeriod (LLC_PRI1_PWM_BASE) -20))

{

EPWM_setTimeBasePeriod(LLC_PRI1_PWM_BASE, tbprd_ticks); // Already enable EPWMLINK for TBPRD

EPWM_setCounterCompareValue(LLC_PRI1_PWM_BASE, EPWM_COUNTER_COMPARE_A, cmpa_1_ticks);

EPWM_setCounterCompareValue(LLC_PRI2_PWM_BASE, EPWM_COUNTER_COMPARE_A, cmpa_2_ticks);

EPWM_setCounterCompareValue(LLC_PRI2_PWM_BASE, EPWM_COUNTER_COMPARE_B, cmpb_2_ticks);

EPWM_setCounterCompareValue(LLC_PRI3_PWM_BASE, EPWM_COUNTER_COMPARE_A, cmpa_3_ticks);

EPWM_setCounterCompareValue(LLC_PRI3_PWM_BASE, EPWM_COUNTER_COMPARE_B, cmpb_3_ticks);

EPWM_setGlobalLoadOneShotLatch(LLC_PRI1_PWM_BASE);

}

else

{

__asm(" RPT #20 || NOP") ; //create 20 cycles delay

EPWM_setTimeBasePeriod(LLC_PRI1_PWM_BASE, tbprd_ticks);

EPWM_setCounterCompareValue(LLC_PRI1_PWM_BASE, EPWM_COUNTER_COMPARE_A, cmpa_1_ticks);

EPWM_setCounterCompareValue(LLC_PRI2_PWM_BASE, EPWM_COUNTER_COMPARE_A, cmpa_2_ticks);

EPWM_setCounterCompareValue(LLC_PRI2_PWM_BASE, EPWM_COUNTER_COMPARE_B, cmpb_2_ticks);

EPWM_setCounterCompareValue(LLC_PRI3_PWM_BASE, EPWM_COUNTER_COMPARE_A, cmpa_3_ticks);

EPWM_setCounterCompareValue(LLC_PRI3_PWM_BASE, EPWM_COUNTER_COMPARE_B, cmpb_3_ticks);

EPWM_setGlobalLoadOneShotLatch(LLC_PRI1_PWM_BASE);

}

}

值得一提的是,在F28P65x提供的Type 5 EPWM 中,有新的硬件机制也可以解决这个问题,具体可以参考对应的应用手册。

参考文献:

[1] Texas Instruments: Implement three-phase interleaved LLC on C2000 Type-4 PWM

[2] Texas Instruments: Leverage New Type ePWM Features for Multiple Phase Control