作者:Emma Wang and Minghan Dong

在通讯电源领域,有很多开发者需要采用峰值电流控制。在最新一代的C2000中,比如F28004X和F28002X(本文的讨论都是基于这两个系列的芯片),可以利用C2000内部的CMPSS 模块对电感电流进行比较,产生比较信号后,通过PWM的T1或T2事件去控制PWM的发波。

但是,Digital compare 模块和Trip zone 模块紧紧耦合在一起,所以开发者稍不留神,就会出现预料之外的现象。这里,以同步boost 电路为例,分析一下异常情况的原因和解决办法。

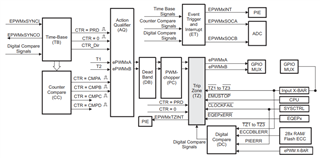

每个Digital compare模块能够根据你选则的输入信号,满足低或高时,产生总共4个比较事件,即DCAEVT1/2和DCBEVT1/2。然后去做一些事情,比如,产生PWM保护,同步其他PWM,或者是去触发ADC采样。另外,也可以将这个信号可以送入T1和T2事件,去做PWM的动作。

图1 PWM 子模块关系图

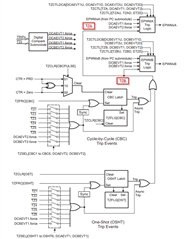

图2为PWM保护模块逻辑信号, 从图中可以清楚地知道,DCAEVT1/DCBEVT1只能用于ONE SHOT保护,DCAEVT2/DCBEVT2只能用于CBC保护。

图2 PWM保护模块逻辑信号

同时,由Digital Compare模块生成的DCAEVT1/2和DCBEVT1/2有两个路径可以作用到TZ:

- 一个是通过TZSEL 寄存器,选择为TZA 和TZB的输入源,即合上图2 左侧是选通开关;

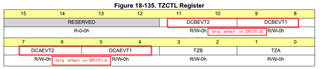

- 另外就是在图2右侧,force和DCAEVT2.force会直接作用到PWMxA,类似的,DCBEVT1.force和DCBEVT2.force会直接作用到PWMxB。如figure 18-135所描述。

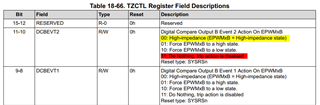

注:第一种方式,通过TZA 和TZB 的信号是有锁存器的,即会有CBC 或是OST的保护,而这里,TZCTL的DCAEVT1/2和DCBEVT1/2复位值为高阻态,这样如果外围电路有下拉,对应的动作会是拉低。第二种方式,DCAEVT1.force和DCAEVT2.force直接作用到PWMxA是没有锁存器的,所以在一个PWM周期内,如果相应的信号消失后,PWMxA就会立刻恢复。

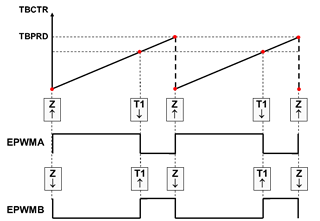

在同步boost 电路的设计中,开发者用PWM1A/ PWM1B 两个通道做Boost的主管和同步整流管的驱动。选择峰值电流控制,并将比较信号通过C2000内部的XBar给到DCBEVT2 产生T1动作,PWM的生成情况如图3所示(为了简化,图3没有加入死区),其中,PWM1B的波形为PWM1A的反转波形。这个时候,开发者并没有去修改TZCTL寄存器的值,即默认值高阻态。如table 18-66所描述。

图3 同步boost PWM 发波逻辑

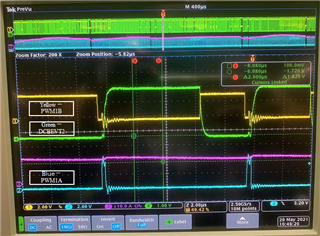

那么,当输入电压和输出电压非常接近的时候,这时,主管的占空比应该非常小,而同步整流管的占空比应该非常大。但是,实际上,从图4 同步boost在输入电压近似于输出电压时发波异常的波形图中可以看出,PWM1B的波形并不是PWM1A 的反转。原因在于,由于DCBEVT2.force 的作用(程序设定高有效)会强制PWM1B 为高阻,而PWM1B管脚在硬件上有下拉电阻,从而拉低了PWM1B ,直到DCBEVT2.force消失。

这边,需要注意,当DCAEVT1/2和DCBEVT1/2 做T1 和T2事件去动作PWM, 同时,没有禁掉DCAEVT1/2和DCBEVT1/2的Trip 功能时,如果T1 和T2事件与trip的动作是矛盾的,以trip 的动作为准。而DCBEVT2只会影响PWM1B,不会影响PWM1A。

所以,我们重新配置软件,把相应的TZCTL寄存器中的DCBEVT2的值改为11,即让DCBEVT2不产生保护作用。就可以解决波形异常的问题。

图4 同步boost在输入电压近似于输出电压时发波异常

参考资料:

TMS320F28002x Real-Time Microcontrollers Technical Reference Manual (Rev. A)

-

Victor Sam

-

取消

-

投赞成票

0

投反对票

-

-

登录以回复

-

更多

-

取消

评论-

Victor Sam

-

取消

-

投赞成票

0

投反对票

-

-

登录以回复

-

更多

-

取消

子级