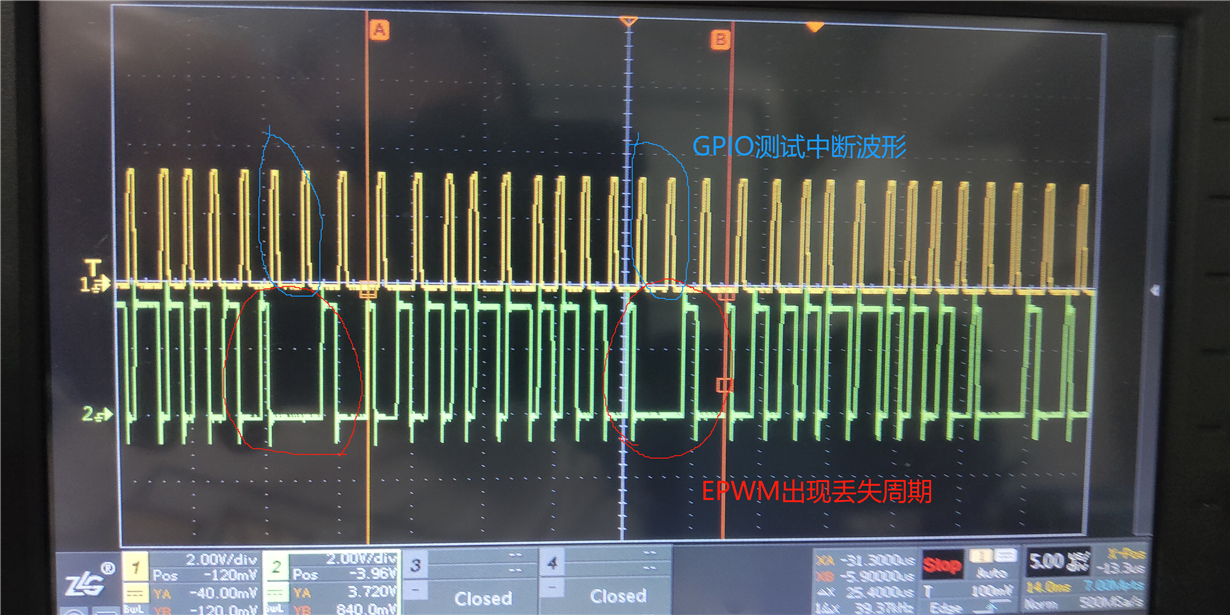

我在使用28335配置一个变周期和变占空比的程序时,想要实现每次计数值等于周期值时进入EPWM中断,给周期值和比较值进行赋值,从而在一个循环计数中,不断改变周期和占空比。现在是想要实现12个脉冲周期一个循环变时,出现有一个周期占空比丢失的情况,实际测量发现该次是进入中断,并且进行了计数,但是没有进行比较操作,也就是这个周期内全为低电平,之后正常进入下一个周期。请问这个可能是什么原因导致的?图中示波器波形是,1.使用一个GPIO引脚电平变化测试中断执行时间波形,进入电平为1,退出变成0 2.EPWM波形。

这是EPWM1中断函数配置:

interrupt void epwm1_isr(void)

{

// Update the CMPA and CMPB values

GpioDataRegs.GPASET.bit.GPIO6 = 1;

flag_in=1;

i++;

if(i>=13)

{

i=1;

}

if(flag_in==1)

{

switch(i)

{

case 1:EPwm1Regs.TBPRD=173;

EPwm1Regs.CMPA.half.CMPA=130;

flag_in=0;

{

// Update the CMPA and CMPB values

GpioDataRegs.GPASET.bit.GPIO6 = 1;

flag_in=1;

i++;

if(i>=13)

{

i=1;

}

if(flag_in==1)

{

switch(i)

{

case 1:EPwm1Regs.TBPRD=173;

EPwm1Regs.CMPA.half.CMPA=130;

flag_in=0;

break;

case 2:EPwm1Regs.TBPRD=393;

EPwm1Regs.CMPA.half.CMPA=267;

flag_in=0;

EPwm1Regs.CMPA.half.CMPA=267;

flag_in=0;

break;

case 3:EPwm1Regs.TBPRD=373;

EPwm1Regs.CMPA.half.CMPA=178;

flag_in=0;

case 3:EPwm1Regs.TBPRD=373;

EPwm1Regs.CMPA.half.CMPA=178;

flag_in=0;

break;

case 4:EPwm1Regs.TBPRD=323;

EPwm1Regs.CMPA.half.CMPA=107;

flag_in=0;

case 4:EPwm1Regs.TBPRD=323;

EPwm1Regs.CMPA.half.CMPA=107;

flag_in=0;

break;

case 5:EPwm1Regs.TBPRD=251;

EPwm1Regs.CMPA.half.CMPA=50;

flag_in=0;

case 5:EPwm1Regs.TBPRD=251;

EPwm1Regs.CMPA.half.CMPA=50;

flag_in=0;

break;

case 6:EPwm1Regs.TBPRD=337;

EPwm1Regs.CMPA.half.CMPA=37;

flag_in=0;

case 6:EPwm1Regs.TBPRD=337;

EPwm1Regs.CMPA.half.CMPA=37;

flag_in=0;

break;

case 7:EPwm1Regs.TBPRD=336;

EPwm1Regs.CMPA.half.CMPA=36;

flag_in=0;

case 7:EPwm1Regs.TBPRD=336;

EPwm1Regs.CMPA.half.CMPA=36;

flag_in=0;

break;

case 8:EPwm1Regs.TBPRD=237;

EPwm1Regs.CMPA.half.CMPA=37;

flag_in=0;

case 8:EPwm1Regs.TBPRD=237;

EPwm1Regs.CMPA.half.CMPA=37;

flag_in=0;

break;

case 9:EPwm1Regs.TBPRD=266;

EPwm1Regs.CMPA.half.CMPA=50;

flag_in=0;

case 9:EPwm1Regs.TBPRD=266;

EPwm1Regs.CMPA.half.CMPA=50;

flag_in=0;

break;

case 10:EPwm1Regs.TBPRD=302;

EPwm1Regs.CMPA.half.CMPA=107;

flag_in=0;

case 10:EPwm1Regs.TBPRD=302;

EPwm1Regs.CMPA.half.CMPA=107;

flag_in=0;

break;

case 11:EPwm1Regs.TBPRD=304;

EPwm1Regs.CMPA.half.CMPA=178;

flag_in=0;

t++;

case 11:EPwm1Regs.TBPRD=304;

EPwm1Regs.CMPA.half.CMPA=178;

flag_in=0;

t++;

break;

case 12:EPwm1Regs.TBPRD=311;

EPwm1Regs.CMPA.half.CMPA=267;

flag_in=0;

break;

// case 13:EPwm1Regs.TBPRD=311;

// EPwm1Regs.CMPA.half.CMPA=267;

// flag_in=0;

//

// break;

case 12:EPwm1Regs.TBPRD=311;

EPwm1Regs.CMPA.half.CMPA=267;

flag_in=0;

break;

// case 13:EPwm1Regs.TBPRD=311;

// EPwm1Regs.CMPA.half.CMPA=267;

// flag_in=0;

//

// break;

}

}

GpioDataRegs.GPACLEAR.bit.GPIO6 = 1;

// Clear INT flag for this timer

EPwm1Regs.ETCLR.bit.INT = 1;

// Acknowledge this interrupt to receive more interrupts from group 3

PieCtrlRegs.PIEACK.all = PIEACK_GROUP3;

}

PieCtrlRegs.PIEACK.all = PIEACK_GROUP3;

}

这是EPWM配置:

InitEPwm1Gpio();

InitEPwm2Gpio();

InitEPwm3Gpio();

InitEPwm4Gpio();

InitEPwm5Gpio();

InitEPwm6Gpio();

// EPwm1Regs.TBSTS.all=0;

// EPwm2Regs.TBSTS.all=0;

// EPwm3Regs.TBSTS.all=0;

// EPwm4Regs.TBSTS.all=0;

EPwm1Regs.TBPHS.half.TBPHS=0;

EPwm2Regs.TBPHS.half.TBPHS=0;

EPwm3Regs.TBPHS.half.TBPHS=0;

EPwm4Regs.TBPHS.half.TBPHS=0;

EPwm5Regs.TBPHS.half.TBPHS=0;

EPwm6Regs.TBPHS.half.TBPHS=0;

EPwm1Regs.TBCTR=0;

EPwm2Regs.TBCTR=0;

EPwm3Regs.TBCTR=0;

EPwm4Regs.TBCTR=0;

EPwm5Regs.TBCTR=0;

EPwm6Regs.TBCTR=0;

InitEPwm2Gpio();

InitEPwm3Gpio();

InitEPwm4Gpio();

InitEPwm5Gpio();

InitEPwm6Gpio();

// EPwm1Regs.TBSTS.all=0;

// EPwm2Regs.TBSTS.all=0;

// EPwm3Regs.TBSTS.all=0;

// EPwm4Regs.TBSTS.all=0;

EPwm1Regs.TBPHS.half.TBPHS=0;

EPwm2Regs.TBPHS.half.TBPHS=0;

EPwm3Regs.TBPHS.half.TBPHS=0;

EPwm4Regs.TBPHS.half.TBPHS=0;

EPwm5Regs.TBPHS.half.TBPHS=0;

EPwm6Regs.TBPHS.half.TBPHS=0;

EPwm1Regs.TBCTR=0;

EPwm2Regs.TBCTR=0;

EPwm3Regs.TBCTR=0;

EPwm4Regs.TBCTR=0;

EPwm5Regs.TBCTR=0;

EPwm6Regs.TBCTR=0;

// EPwm1Regs.CMPCTL.all=0x00; // Shadow mode for CMPA and CMPB

// EPwm2Regs.CMPCTL.all=0x00;

// EPwm3Regs.CMPCTL.all=0x00;

// EPwm4Regs.CMPCTL.all=0x00;

EPwm1Regs.CMPCTL.bit.SHDWAMODE=CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE=CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE=CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE=CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.SHDWAMODE=CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE=CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE=CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.LOADBMODE=CC_CTR_ZERO;

EPwm3Regs.CMPCTL.bit.SHDWAMODE=CC_SHADOW;

EPwm3Regs.CMPCTL.bit.SHDWBMODE=CC_SHADOW;

EPwm3Regs.CMPCTL.bit.LOADAMODE=CC_CTR_ZERO;

EPwm3Regs.CMPCTL.bit.LOADBMODE=CC_CTR_ZERO;

EPwm4Regs.CMPCTL.bit.SHDWAMODE=CC_SHADOW;

EPwm4Regs.CMPCTL.bit.SHDWBMODE=CC_SHADOW;

EPwm4Regs.CMPCTL.bit.LOADAMODE=CC_CTR_ZERO;

EPwm4Regs.CMPCTL.bit.LOADBMODE=CC_CTR_ZERO;

EPwm5Regs.CMPCTL.bit.SHDWAMODE=CC_SHADOW;

EPwm5Regs.CMPCTL.bit.SHDWBMODE=CC_SHADOW;

EPwm5Regs.CMPCTL.bit.LOADAMODE=CC_CTR_ZERO;

EPwm5Regs.CMPCTL.bit.LOADBMODE=CC_CTR_ZERO;

EPwm6Regs.CMPCTL.bit.SHDWAMODE=CC_SHADOW;

EPwm6Regs.CMPCTL.bit.SHDWBMODE=CC_SHADOW;

EPwm6Regs.CMPCTL.bit.LOADAMODE=CC_CTR_ZERO;

EPwm6Regs.CMPCTL.bit.LOADBMODE=CC_CTR_ZERO;

// EPwm2Regs.CMPCTL.all=0x00;

// EPwm3Regs.CMPCTL.all=0x00;

// EPwm4Regs.CMPCTL.all=0x00;

EPwm1Regs.CMPCTL.bit.SHDWAMODE=CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE=CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE=CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE=CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.SHDWAMODE=CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE=CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE=CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.LOADBMODE=CC_CTR_ZERO;

EPwm3Regs.CMPCTL.bit.SHDWAMODE=CC_SHADOW;

EPwm3Regs.CMPCTL.bit.SHDWBMODE=CC_SHADOW;

EPwm3Regs.CMPCTL.bit.LOADAMODE=CC_CTR_ZERO;

EPwm3Regs.CMPCTL.bit.LOADBMODE=CC_CTR_ZERO;

EPwm4Regs.CMPCTL.bit.SHDWAMODE=CC_SHADOW;

EPwm4Regs.CMPCTL.bit.SHDWBMODE=CC_SHADOW;

EPwm4Regs.CMPCTL.bit.LOADAMODE=CC_CTR_ZERO;

EPwm4Regs.CMPCTL.bit.LOADBMODE=CC_CTR_ZERO;

EPwm5Regs.CMPCTL.bit.SHDWAMODE=CC_SHADOW;

EPwm5Regs.CMPCTL.bit.SHDWBMODE=CC_SHADOW;

EPwm5Regs.CMPCTL.bit.LOADAMODE=CC_CTR_ZERO;

EPwm5Regs.CMPCTL.bit.LOADBMODE=CC_CTR_ZERO;

EPwm6Regs.CMPCTL.bit.SHDWAMODE=CC_SHADOW;

EPwm6Regs.CMPCTL.bit.SHDWBMODE=CC_SHADOW;

EPwm6Regs.CMPCTL.bit.LOADAMODE=CC_CTR_ZERO;

EPwm6Regs.CMPCTL.bit.LOADBMODE=CC_CTR_ZERO;

// EPwm1Regs.AQCTLA.all=0x61; // EPWMxA = 1 when CTR=CMPA and counter inc

// EPwm2Regs.AQCTLA.all=0x61;

// EPwm3Regs.AQCTLA.all=0x61;

// EPwm4Regs.AQCTLA.all=0x61;

EPwm1Regs.AQCTLA.bit.CAU=AQ_SET;

EPwm1Regs.AQCTLA.bit.PRD=AQ_CLEAR;

EPwm2Regs.AQCTLA.bit.CAU=AQ_SET;

EPwm2Regs.AQCTLA.bit.PRD=AQ_CLEAR;

EPwm3Regs.AQCTLA.bit.CAU=AQ_SET;

EPwm3Regs.AQCTLA.bit.PRD=AQ_CLEAR;

EPwm4Regs.AQCTLA.bit.CAU=AQ_SET;

EPwm4Regs.AQCTLA.bit.CAD=AQ_CLEAR;

EPwm5Regs.AQCTLA.bit.CAU=AQ_SET;

EPwm5Regs.AQCTLA.bit.CAD=AQ_CLEAR;

EPwm6Regs.AQCTLA.bit.CAU=AQ_SET;

EPwm6Regs.AQCTLA.bit.CAD=AQ_CLEAR;

// EPwm1Regs.AQCTLB.all=0x92;

// EPwm2Regs.AQCTLB.all=0x92;

// EPwm3Regs.AQCTLB.all=0x92;

// EPwm4Regs.AQCTLB.all=0x601;

// EPwm1Regs.AQSFRC.all=0;

// EPwm1Regs.AQCSFRC.all=0;

// EPwm2Regs.AQSFRC.all=0;

// EPwm2Regs.AQCSFRC.all=0;

// EPwm3Regs.AQSFRC.all=0;

// EPwm3Regs.AQCSFRC.all=0;

// EPwm4Regs.AQSFRC.all=0;

// EPwm4Regs.AQCSFRC.all=0;

EPwm1Regs.DBCTL.bit.OUT_MODE=DB_FULL_ENABLE;

EPwm1Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;

EPwm1Regs.DBCTL.bit.IN_MODE=DBA_ALL;

EPwm1Regs.DBRED=Dead_time;

EPwm1Regs.DBFED=Dead_time;

EPwm2Regs.DBCTL.bit.OUT_MODE=DB_FULL_ENABLE;

EPwm2Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;

EPwm2Regs.DBCTL.bit.IN_MODE=DBA_ALL;

EPwm2Regs.DBRED=Dead_time;

EPwm2Regs.DBFED=Dead_time;

EPwm3Regs.DBCTL.bit.OUT_MODE=DB_FULL_ENABLE;

EPwm3Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;

EPwm3Regs.DBCTL.bit.IN_MODE=DBA_ALL;

EPwm3Regs.DBRED=Dead_time;

EPwm3Regs.DBFED=Dead_time;

EPwm4Regs.DBCTL.bit.OUT_MODE=DB_DISABLE; //不设置死区

EPwm4Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;

EPwm4Regs.DBCTL.bit.IN_MODE=DBA_ALL;

EPwm4Regs.DBRED=Dead_time;//3us

EPwm4Regs.DBFED=Dead_time;

EPwm5Regs.DBCTL.bit.OUT_MODE=DB_DISABLE; //不设置死区

EPwm5Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;

EPwm5Regs.DBCTL.bit.IN_MODE=DBA_ALL;

EPwm5Regs.DBRED=Dead_time;//3us

EPwm5Regs.DBFED=Dead_time;

EPwm6Regs.DBCTL.bit.OUT_MODE=DB_DISABLE; //不设置死区

EPwm6Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;

EPwm6Regs.DBCTL.bit.IN_MODE=DBA_ALL;

EPwm6Regs.DBRED=Dead_time;//3us

EPwm6Regs.DBFED=Dead_time;

EPwm1Regs.TZSEL.all=0;

EPwm2Regs.TZSEL.all=0;

EPwm3Regs.TZSEL.all=0;

EPwm4Regs.TZSEL.all=0;

EPwm5Regs.TZSEL.all=0;

EPwm6Regs.TZSEL.all=0;

EPwm1Regs.TZCTL.all=0;

EPwm2Regs.TZCTL.all=0;

EPwm3Regs.TZCTL.all=0;

EPwm4Regs.TZCTL.all=0;

EPwm5Regs.TZCTL.all=0;

EPwm6Regs.TZCTL.all=0;

EPwm1Regs.TZEINT.all=0;

EPwm2Regs.TZEINT.all=0;

EPwm3Regs.TZEINT.all=0;

EPwm4Regs.TZEINT.all=0;

EPwm5Regs.TZEINT.all=0;

EPwm6Regs.TZEINT.all=0;

EPwm1Regs.TZFLG.all=0;

EPwm2Regs.TZFLG.all=0;

EPwm3Regs.TZFLG.all=0;

EPwm4Regs.TZFLG.all=0;

EPwm5Regs.TZFLG.all=0;

EPwm6Regs.TZFLG.all=0;

EPwm1Regs.TZCLR.all=0;

EPwm2Regs.TZCLR.all=0;

EPwm3Regs.TZCLR.all=0;

EPwm4Regs.TZCLR.all=0;

EPwm5Regs.TZCLR.all=0;

EPwm6Regs.TZCLR.all=0;

EPwm1Regs.TZFRC.all=0;

EPwm2Regs.TZFRC.all=0;

EPwm3Regs.TZFRC.all=0;

EPwm4Regs.TZFRC.all=0;

EPwm5Regs.TZFRC.all=0;

EPwm6Regs.TZFRC.all=0;

// EPwm2Regs.AQCTLA.all=0x61;

// EPwm3Regs.AQCTLA.all=0x61;

// EPwm4Regs.AQCTLA.all=0x61;

EPwm1Regs.AQCTLA.bit.CAU=AQ_SET;

EPwm1Regs.AQCTLA.bit.PRD=AQ_CLEAR;

EPwm2Regs.AQCTLA.bit.CAU=AQ_SET;

EPwm2Regs.AQCTLA.bit.PRD=AQ_CLEAR;

EPwm3Regs.AQCTLA.bit.CAU=AQ_SET;

EPwm3Regs.AQCTLA.bit.PRD=AQ_CLEAR;

EPwm4Regs.AQCTLA.bit.CAU=AQ_SET;

EPwm4Regs.AQCTLA.bit.CAD=AQ_CLEAR;

EPwm5Regs.AQCTLA.bit.CAU=AQ_SET;

EPwm5Regs.AQCTLA.bit.CAD=AQ_CLEAR;

EPwm6Regs.AQCTLA.bit.CAU=AQ_SET;

EPwm6Regs.AQCTLA.bit.CAD=AQ_CLEAR;

// EPwm1Regs.AQCTLB.all=0x92;

// EPwm2Regs.AQCTLB.all=0x92;

// EPwm3Regs.AQCTLB.all=0x92;

// EPwm4Regs.AQCTLB.all=0x601;

// EPwm1Regs.AQSFRC.all=0;

// EPwm1Regs.AQCSFRC.all=0;

// EPwm2Regs.AQSFRC.all=0;

// EPwm2Regs.AQCSFRC.all=0;

// EPwm3Regs.AQSFRC.all=0;

// EPwm3Regs.AQCSFRC.all=0;

// EPwm4Regs.AQSFRC.all=0;

// EPwm4Regs.AQCSFRC.all=0;

EPwm1Regs.DBCTL.bit.OUT_MODE=DB_FULL_ENABLE;

EPwm1Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;

EPwm1Regs.DBCTL.bit.IN_MODE=DBA_ALL;

EPwm1Regs.DBRED=Dead_time;

EPwm1Regs.DBFED=Dead_time;

EPwm2Regs.DBCTL.bit.OUT_MODE=DB_FULL_ENABLE;

EPwm2Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;

EPwm2Regs.DBCTL.bit.IN_MODE=DBA_ALL;

EPwm2Regs.DBRED=Dead_time;

EPwm2Regs.DBFED=Dead_time;

EPwm3Regs.DBCTL.bit.OUT_MODE=DB_FULL_ENABLE;

EPwm3Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;

EPwm3Regs.DBCTL.bit.IN_MODE=DBA_ALL;

EPwm3Regs.DBRED=Dead_time;

EPwm3Regs.DBFED=Dead_time;

EPwm4Regs.DBCTL.bit.OUT_MODE=DB_DISABLE; //不设置死区

EPwm4Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;

EPwm4Regs.DBCTL.bit.IN_MODE=DBA_ALL;

EPwm4Regs.DBRED=Dead_time;//3us

EPwm4Regs.DBFED=Dead_time;

EPwm5Regs.DBCTL.bit.OUT_MODE=DB_DISABLE; //不设置死区

EPwm5Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;

EPwm5Regs.DBCTL.bit.IN_MODE=DBA_ALL;

EPwm5Regs.DBRED=Dead_time;//3us

EPwm5Regs.DBFED=Dead_time;

EPwm6Regs.DBCTL.bit.OUT_MODE=DB_DISABLE; //不设置死区

EPwm6Regs.DBCTL.bit.POLSEL=DB_ACTV_HIC;

EPwm6Regs.DBCTL.bit.IN_MODE=DBA_ALL;

EPwm6Regs.DBRED=Dead_time;//3us

EPwm6Regs.DBFED=Dead_time;

EPwm1Regs.TZSEL.all=0;

EPwm2Regs.TZSEL.all=0;

EPwm3Regs.TZSEL.all=0;

EPwm4Regs.TZSEL.all=0;

EPwm5Regs.TZSEL.all=0;

EPwm6Regs.TZSEL.all=0;

EPwm1Regs.TZCTL.all=0;

EPwm2Regs.TZCTL.all=0;

EPwm3Regs.TZCTL.all=0;

EPwm4Regs.TZCTL.all=0;

EPwm5Regs.TZCTL.all=0;

EPwm6Regs.TZCTL.all=0;

EPwm1Regs.TZEINT.all=0;

EPwm2Regs.TZEINT.all=0;

EPwm3Regs.TZEINT.all=0;

EPwm4Regs.TZEINT.all=0;

EPwm5Regs.TZEINT.all=0;

EPwm6Regs.TZEINT.all=0;

EPwm1Regs.TZFLG.all=0;

EPwm2Regs.TZFLG.all=0;

EPwm3Regs.TZFLG.all=0;

EPwm4Regs.TZFLG.all=0;

EPwm5Regs.TZFLG.all=0;

EPwm6Regs.TZFLG.all=0;

EPwm1Regs.TZCLR.all=0;

EPwm2Regs.TZCLR.all=0;

EPwm3Regs.TZCLR.all=0;

EPwm4Regs.TZCLR.all=0;

EPwm5Regs.TZCLR.all=0;

EPwm6Regs.TZCLR.all=0;

EPwm1Regs.TZFRC.all=0;

EPwm2Regs.TZFRC.all=0;

EPwm3Regs.TZFRC.all=0;

EPwm4Regs.TZFRC.all=0;

EPwm5Regs.TZFRC.all=0;

EPwm6Regs.TZFRC.all=0;

EPwm1Regs.ETSEL.bit.SOCAEN = 1; // Enable SOC on A group ADC触发信号

EPwm1Regs.ETSEL.bit.SOCASEL = ET_CTR_PRD; // Select SOC from PRD

EPwm1Regs.ETPS.bit.SOCAPRD = ET_1ST; //一个事件触发一次ADC

EPwm2Regs.ETSEL.all=0;

EPwm3Regs.ETSEL.all=0;

EPwm4Regs.ETSEL.all=0;

EPwm5Regs.ETSEL.all=0;

EPwm6Regs.ETSEL.all=0;

EPwm1Regs.ETFLG.all=0;

EPwm2Regs.ETFLG.all=0;

EPwm3Regs.ETFLG.all=0;

EPwm4Regs.ETFLG.all=0;

EPwm5Regs.ETFLG.all=0;

EPwm6Regs.ETFLG.all=0;

EPwm1Regs.ETCLR.all=0;

EPwm2Regs.ETCLR.all=0;

EPwm3Regs.ETCLR.all=0;

EPwm4Regs.ETCLR.all=0;

EPwm5Regs.ETCLR.all=0;

EPwm6Regs.ETCLR.all=0;

EPwm1Regs.ETFRC.all=0;

EPwm2Regs.ETFRC.all=0;

EPwm3Regs.ETFRC.all=0;

EPwm4Regs.ETFRC.all=0;

EPwm5Regs.ETFRC.all=0;

EPwm6Regs.ETFRC.all=0;

EPwm1Regs.ETSEL.bit.SOCASEL = ET_CTR_PRD; // Select SOC from PRD

EPwm1Regs.ETPS.bit.SOCAPRD = ET_1ST; //一个事件触发一次ADC

EPwm2Regs.ETSEL.all=0;

EPwm3Regs.ETSEL.all=0;

EPwm4Regs.ETSEL.all=0;

EPwm5Regs.ETSEL.all=0;

EPwm6Regs.ETSEL.all=0;

EPwm1Regs.ETFLG.all=0;

EPwm2Regs.ETFLG.all=0;

EPwm3Regs.ETFLG.all=0;

EPwm4Regs.ETFLG.all=0;

EPwm5Regs.ETFLG.all=0;

EPwm6Regs.ETFLG.all=0;

EPwm1Regs.ETCLR.all=0;

EPwm2Regs.ETCLR.all=0;

EPwm3Regs.ETCLR.all=0;

EPwm4Regs.ETCLR.all=0;

EPwm5Regs.ETCLR.all=0;

EPwm6Regs.ETCLR.all=0;

EPwm1Regs.ETFRC.all=0;

EPwm2Regs.ETFRC.all=0;

EPwm3Regs.ETFRC.all=0;

EPwm4Regs.ETFRC.all=0;

EPwm5Regs.ETFRC.all=0;

EPwm6Regs.ETFRC.all=0;

EPwm1Regs.PCCTL.all=0;

EPwm2Regs.PCCTL.all=0;

EPwm3Regs.PCCTL.all=0;

EPwm4Regs.PCCTL.all=0;

EPwm5Regs.PCCTL.all=0;

EPwm6Regs.PCCTL.all=0;

EPwm2Regs.PCCTL.all=0;

EPwm3Regs.PCCTL.all=0;

EPwm4Regs.PCCTL.all=0;

EPwm5Regs.PCCTL.all=0;

EPwm6Regs.PCCTL.all=0;

// EPwm1Regs.TBCTL.all=0x0006; // Enable Timer,0012禁止相位装载->0016相位装载

// EPwm2Regs.TBCTL.all=0x0006;

// EPwm3Regs.TBCTL.all=0x0006;

// EPwm4Regs.TBCTL.all=0x0006;

// EPwm2Regs.TBCTL.all=0x0006;

// EPwm3Regs.TBCTL.all=0x0006;

// EPwm4Regs.TBCTL.all=0x0006;

EPwm1Regs.TBCTL.bit.CTRMODE=TB_COUNT_UP;//上升计数模式

EPwm1Regs.TBCTL.bit.PHSEN=TB_DISABLE;//使能相位校正功能

EPwm1Regs.TBCTL.bit.PRDLD=TB_SHADOW;//使能相位校正功能

EPwm1Regs.TBCTL.bit.SYNCOSEL=TB_CTR_ZERO;//使能相位校正功能

EPwm1Regs.TBCTL.bit.HSPCLKDIV=1;//设定TBCLK与SYSCLKOUT的关系

EPwm1Regs.TBCTL.bit.CLKDIV=0;//设定TBCLK与SYSCLKOUT的关系

EPwm2Regs.TBCTL.bit.CTRMODE=TB_COUNT_UP;//上升计数模式

EPwm2Regs.TBCTL.bit.PHSEN=TB_DISABLE;//使能相位校正功能

EPwm2Regs.TBCTL.bit.PRDLD=TB_SHADOW;//使能相位校正功能

EPwm2Regs.TBCTL.bit.SYNCOSEL=TB_SYNC_IN;//使能相位校正功能

EPwm2Regs.TBCTL.bit.HSPCLKDIV=1;//设定TBCLK与SYSCLKOUT的关系

EPwm2Regs.TBCTL.bit.CLKDIV=0;//设定TBCLK与SYSCLKOUT的关系

EPwm3Regs.TBCTL.bit.CTRMODE=TB_COUNT_UP;//上升计数模式

EPwm3Regs.TBCTL.bit.PHSEN=TB_DISABLE;//使能相位校正功能

EPwm3Regs.TBCTL.bit.PRDLD=TB_SHADOW;//使能相位校正功能

EPwm3Regs.TBCTL.bit.SYNCOSEL=TB_SYNC_IN;//使能相位校正功能

EPwm3Regs.TBCTL.bit.HSPCLKDIV=1;//设定TBCLK与SYSCLKOUT的关系

EPwm3Regs.TBCTL.bit.CLKDIV=0;//设定TBCLK与SYSCLKOUT的关系

EPwm4Regs.TBCTL.all=0x0006;

EPwm5Regs.TBCTL.all=0x0006;

EPwm6Regs.TBCTL.all=0x0006;

EPwm1Regs.TBPRD=SP;

EPwm2Regs.TBPRD=SP;

EPwm3Regs.TBPRD=SP;

EPwm4Regs.TBPRD=SP;

EPwm5Regs.TBPRD=SP;

EPwm6Regs.TBPRD=SP;

EPwm1Regs.CMPA.half.CMPA =SP;

EPwm2Regs.CMPA.half.CMPA =SP;

EPwm3Regs.CMPA.half.CMPA =SP;

EPwm4Regs.CMPA.half.CMPA =SP;

EPwm5Regs.CMPA.half.CMPA =SP;

EPwm6Regs.CMPA.half.CMPA =SP;

EPwm4Regs.CMPB=SP;

EPwm1Regs.TBCTL.bit.PHSEN=TB_DISABLE;//使能相位校正功能

EPwm1Regs.TBCTL.bit.PRDLD=TB_SHADOW;//使能相位校正功能

EPwm1Regs.TBCTL.bit.SYNCOSEL=TB_CTR_ZERO;//使能相位校正功能

EPwm1Regs.TBCTL.bit.HSPCLKDIV=1;//设定TBCLK与SYSCLKOUT的关系

EPwm1Regs.TBCTL.bit.CLKDIV=0;//设定TBCLK与SYSCLKOUT的关系

EPwm2Regs.TBCTL.bit.CTRMODE=TB_COUNT_UP;//上升计数模式

EPwm2Regs.TBCTL.bit.PHSEN=TB_DISABLE;//使能相位校正功能

EPwm2Regs.TBCTL.bit.PRDLD=TB_SHADOW;//使能相位校正功能

EPwm2Regs.TBCTL.bit.SYNCOSEL=TB_SYNC_IN;//使能相位校正功能

EPwm2Regs.TBCTL.bit.HSPCLKDIV=1;//设定TBCLK与SYSCLKOUT的关系

EPwm2Regs.TBCTL.bit.CLKDIV=0;//设定TBCLK与SYSCLKOUT的关系

EPwm3Regs.TBCTL.bit.CTRMODE=TB_COUNT_UP;//上升计数模式

EPwm3Regs.TBCTL.bit.PHSEN=TB_DISABLE;//使能相位校正功能

EPwm3Regs.TBCTL.bit.PRDLD=TB_SHADOW;//使能相位校正功能

EPwm3Regs.TBCTL.bit.SYNCOSEL=TB_SYNC_IN;//使能相位校正功能

EPwm3Regs.TBCTL.bit.HSPCLKDIV=1;//设定TBCLK与SYSCLKOUT的关系

EPwm3Regs.TBCTL.bit.CLKDIV=0;//设定TBCLK与SYSCLKOUT的关系

EPwm4Regs.TBCTL.all=0x0006;

EPwm5Regs.TBCTL.all=0x0006;

EPwm6Regs.TBCTL.all=0x0006;

EPwm1Regs.TBPRD=SP;

EPwm2Regs.TBPRD=SP;

EPwm3Regs.TBPRD=SP;

EPwm4Regs.TBPRD=SP;

EPwm5Regs.TBPRD=SP;

EPwm6Regs.TBPRD=SP;

EPwm1Regs.CMPA.half.CMPA =SP;

EPwm2Regs.CMPA.half.CMPA =SP;

EPwm3Regs.CMPA.half.CMPA =SP;

EPwm4Regs.CMPA.half.CMPA =SP;

EPwm5Regs.CMPA.half.CMPA =SP;

EPwm6Regs.CMPA.half.CMPA =SP;

EPwm4Regs.CMPB=SP;

// EPwm4Regs.CMPB=SP;

// EPwm1Regs.CMPB=SP;

// EPwm2Regs.CMPB=SP;

// EPwm3Regs.CMPB=SP;

// EPwm1Regs.CMPB=SP;

// EPwm2Regs.CMPB=SP;

// EPwm3Regs.CMPB=SP;

// EPwm1Regs.ETCLR.bit.INT=1;

// PieCtrlRegs.PIEACK.all=PIEACK_GROUP3;

#if 0

EPwm5Regs.TBSTS.all=0;

EPwm5Regs.TBPHS.half.TBPHS=0;

EPwm5Regs.TBCTR=0;

EPwm5Regs.CMPCTL.all=0x50; // Immediate mode for CMPA and CMPB

EPwm5Regs.CMPA.half.CMPA =SP*3/4;

//EPwm1Regs.CMPB=SP/2;

EPwm5Regs.AQCTLA.all=0x90; // EPWMxA = 1 when CTR=CMPA and counter inc // EPWMxA = 0 when CTR=CMPA and counter dec

// EPwm1Regs.AQCTLB.all=0x600;

// EPwm1Regs.AQCTLB.all=0;

EPwm5Regs.AQSFRC.all=0;

EPwm5Regs.AQCSFRC.all=0;

EPwm5Regs.DBCTL.bit.IN_MODE=0;

EPwm5Regs.DBCTL.bit.OUT_MODE=3;

EPwm5Regs.DBCTL.bit.POLSEL=2;

EPwm5Regs.DBFED=300;

EPwm5Regs.DBRED=300;

EPwm5Regs.TBCTL.all=0x0010+TBCTLVAL; // Enable Timer

EPwm5Regs.TBPRD=SP;

#endif

// PieCtrlRegs.PIEACK.all=PIEACK_GROUP3;

#if 0

EPwm5Regs.TBSTS.all=0;

EPwm5Regs.TBPHS.half.TBPHS=0;

EPwm5Regs.TBCTR=0;

EPwm5Regs.CMPCTL.all=0x50; // Immediate mode for CMPA and CMPB

EPwm5Regs.CMPA.half.CMPA =SP*3/4;

//EPwm1Regs.CMPB=SP/2;

EPwm5Regs.AQCTLA.all=0x90; // EPWMxA = 1 when CTR=CMPA and counter inc // EPWMxA = 0 when CTR=CMPA and counter dec

// EPwm1Regs.AQCTLB.all=0x600;

// EPwm1Regs.AQCTLB.all=0;

EPwm5Regs.AQSFRC.all=0;

EPwm5Regs.AQCSFRC.all=0;

EPwm5Regs.DBCTL.bit.IN_MODE=0;

EPwm5Regs.DBCTL.bit.OUT_MODE=3;

EPwm5Regs.DBCTL.bit.POLSEL=2;

EPwm5Regs.DBFED=300;

EPwm5Regs.DBRED=300;

EPwm5Regs.TBCTL.all=0x0010+TBCTLVAL; // Enable Timer

EPwm5Regs.TBPRD=SP;

#endif