Part Number: THS3120EVM

Other Parts Discussed in Thread: THS3120, OPA810

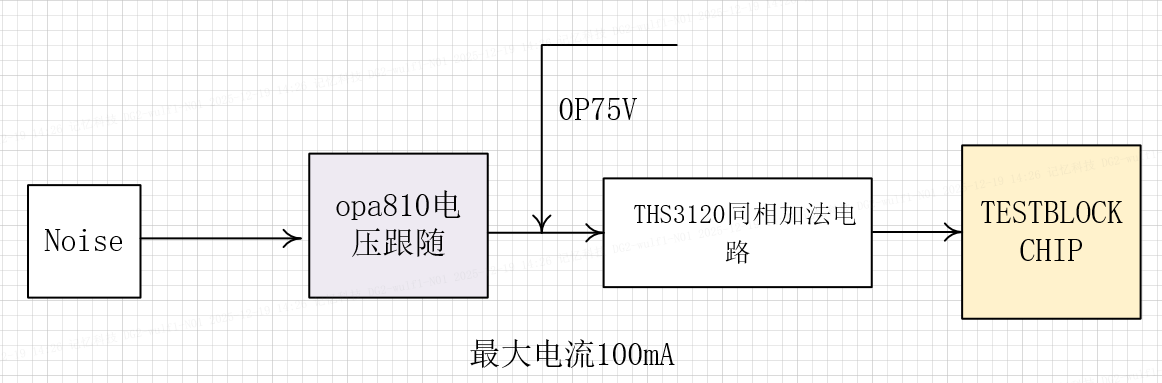

我们的设计要求是:对芯片的power PIN 输入一个叠加直流分量的噪声,从而观察芯片对噪声的抗噪声能力是怎么样的。

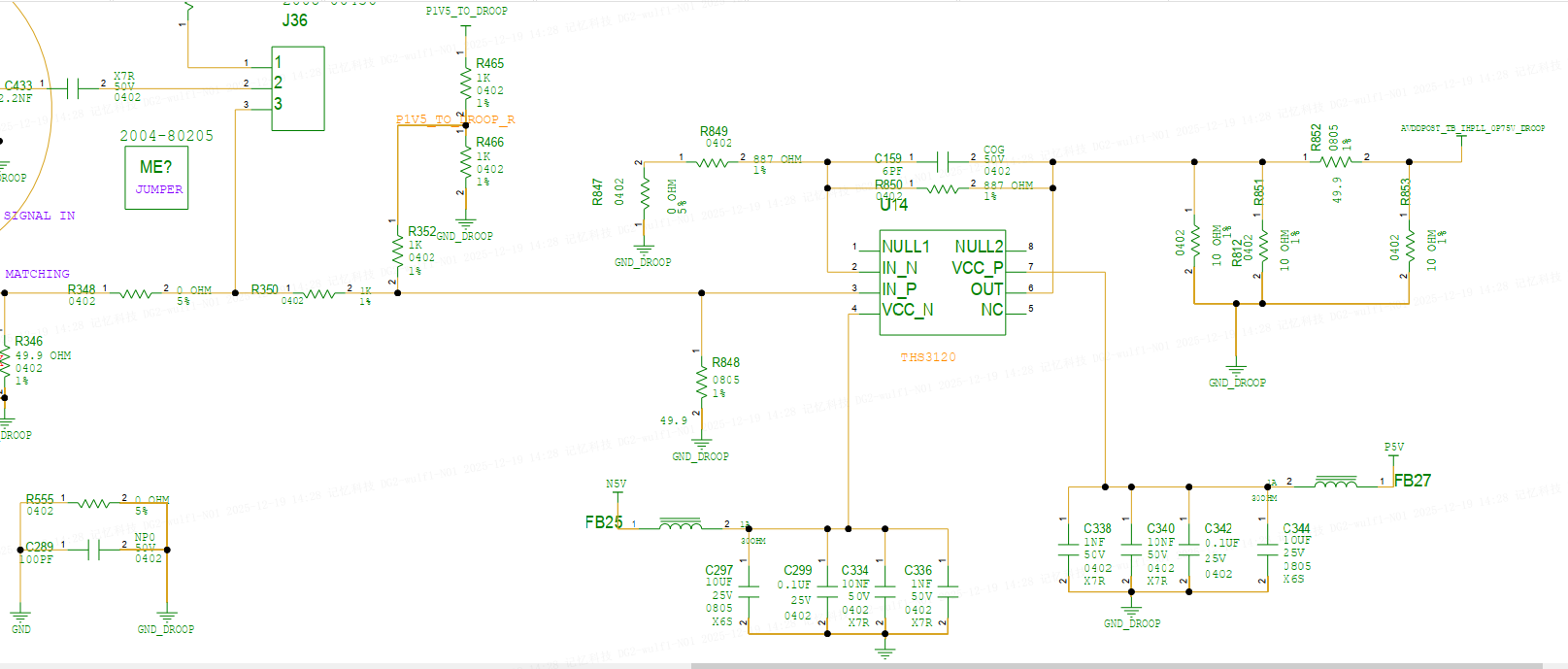

我们是先把噪声经过OPA810跟随,再和0p75V电源通过THS3120 同相加法电路,叠加输出到测试芯片的power pin上。

帮忙看看这样的方案能否直接测试芯片的power pin,对端容性负载能力是否能满足

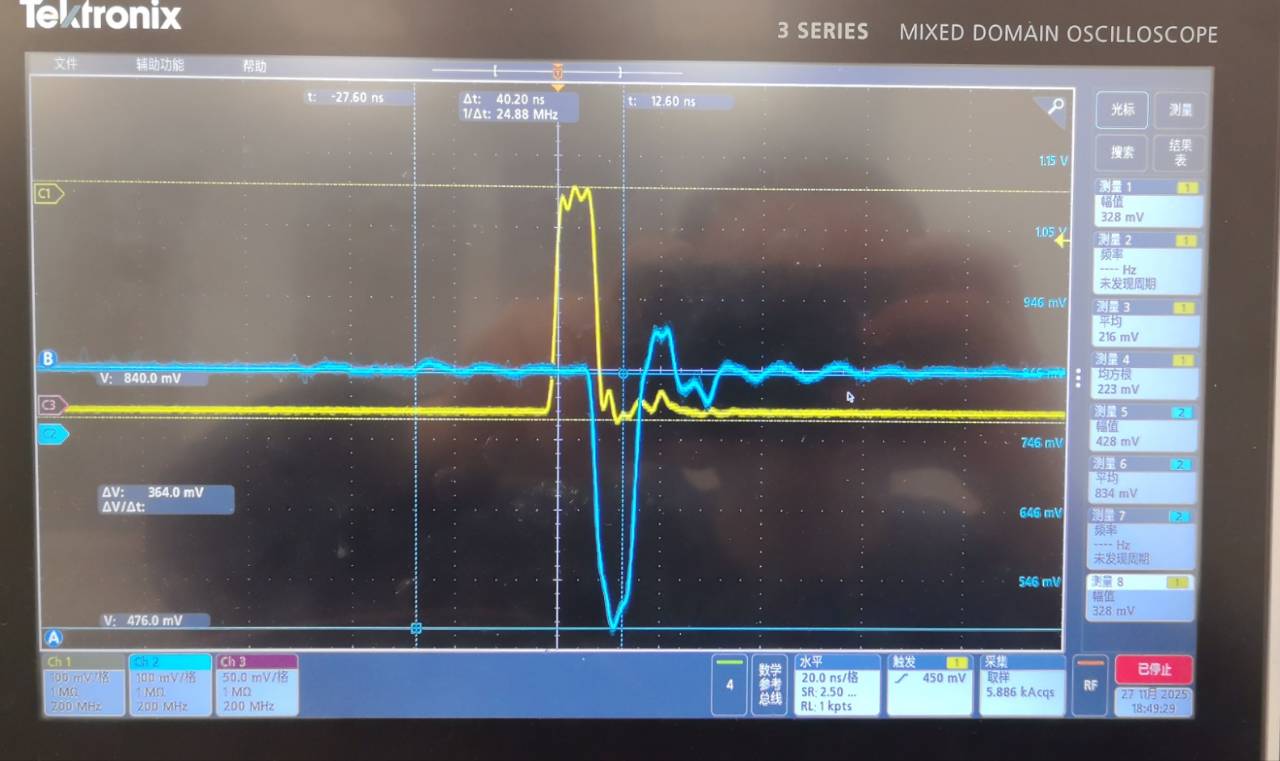

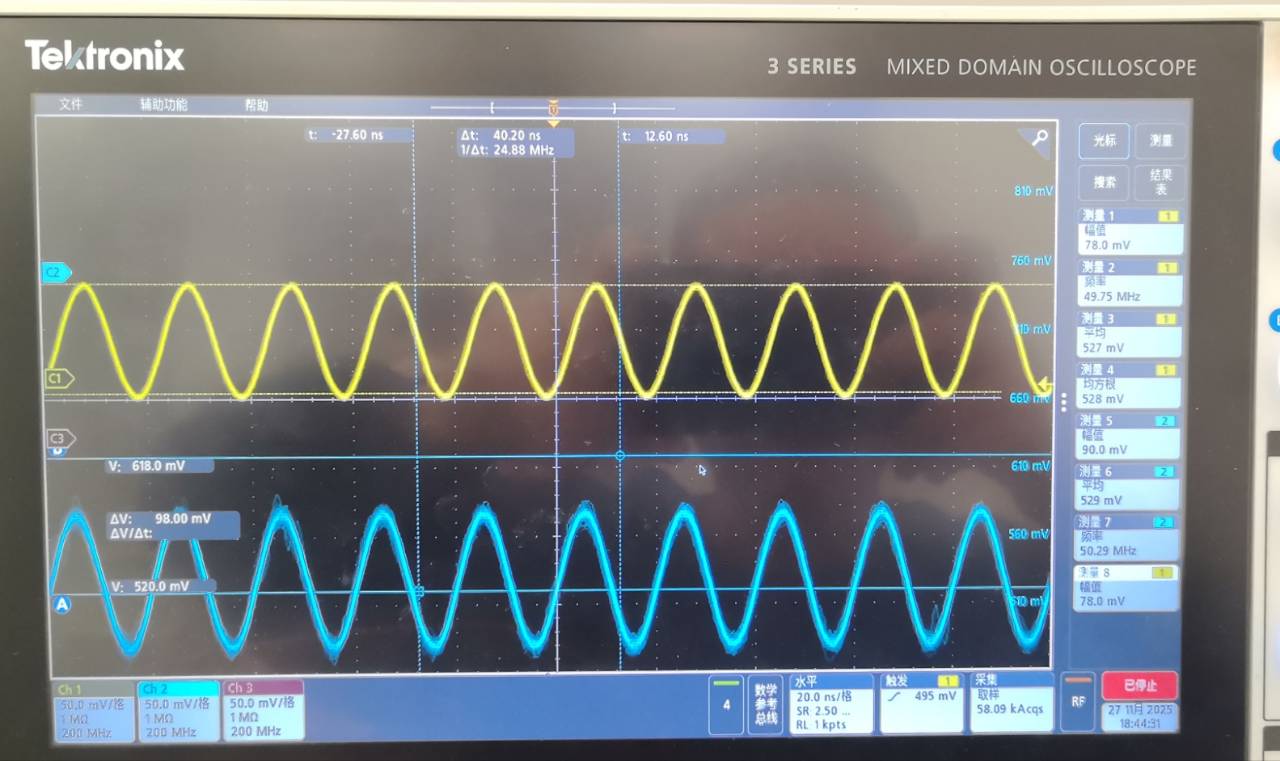

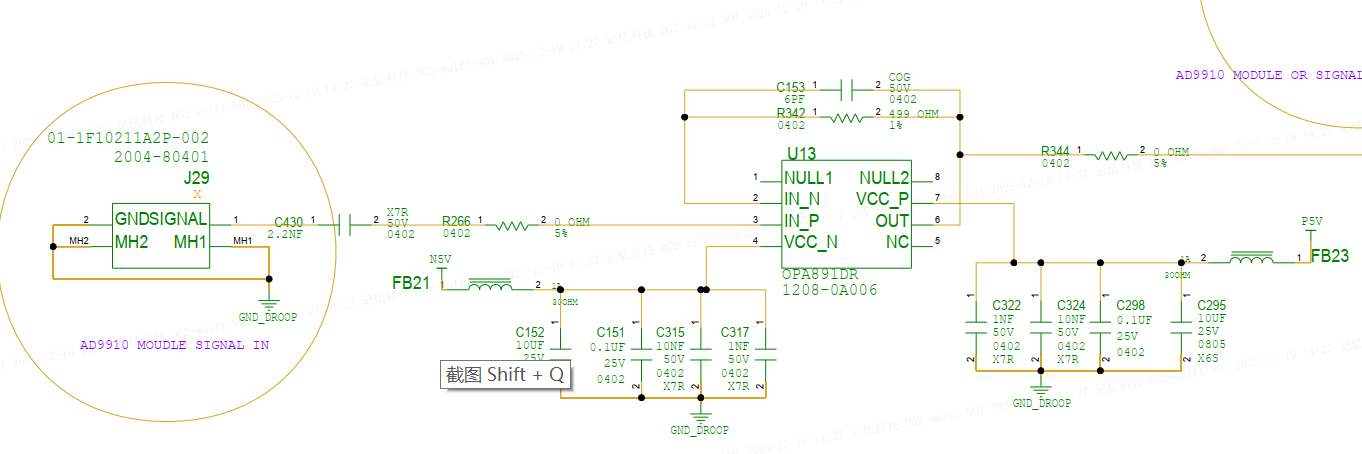

图片为我们实际的原理图和方案,还有输入的两种噪声波形。