故障样品客户反馈现象

一、客户反馈现象如下:

2.客户生产一批产品317pcs,报性能故障总共5台机器,其中1台是常温上电就报性能故障,另外4台做完50度2小时带载老化后,从高温箱里拿出来后,再次上电能故障。

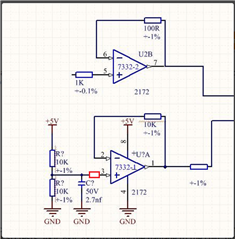

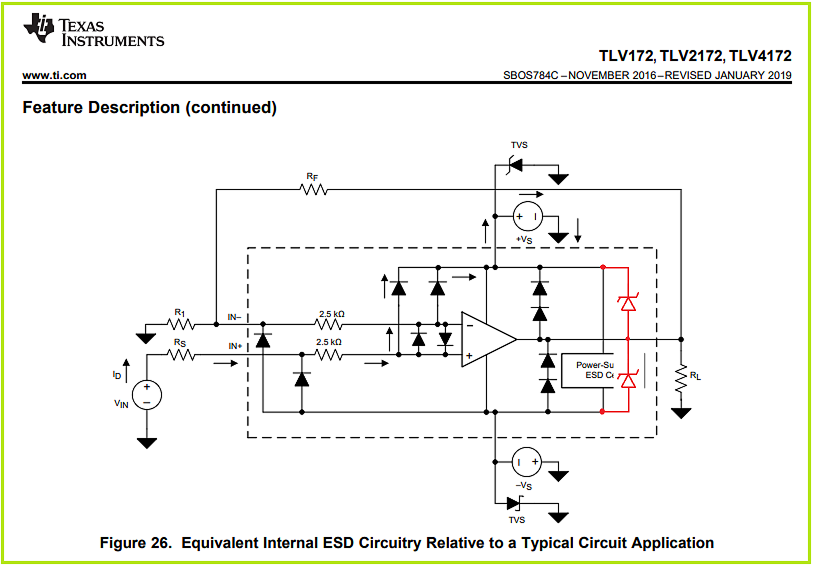

我司拆解分析是TLV2172发生故障,换上OK件TLV2172后,故障解除,功能恢复正常。

二、测试分析

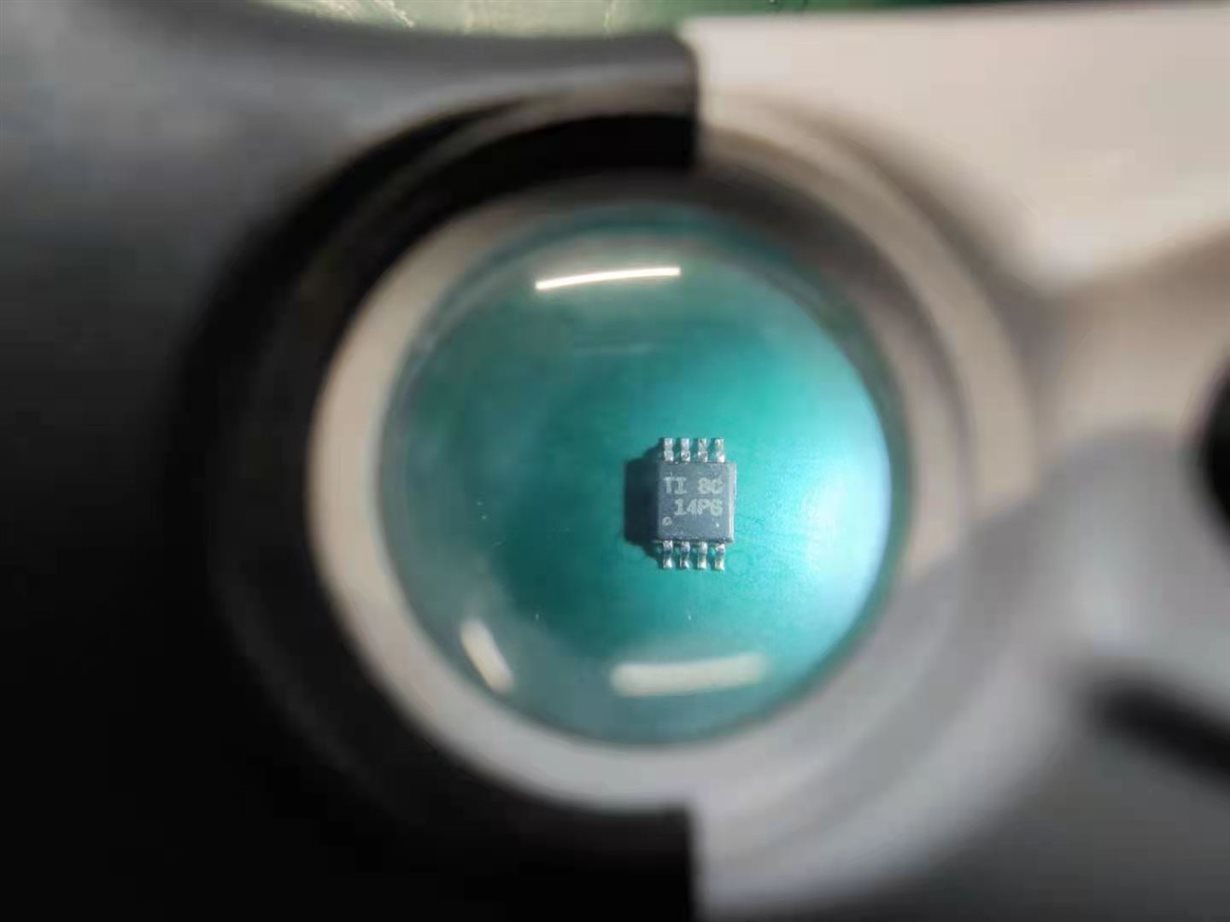

我司委托检测机构开片分析客诉品上的TLV2172。

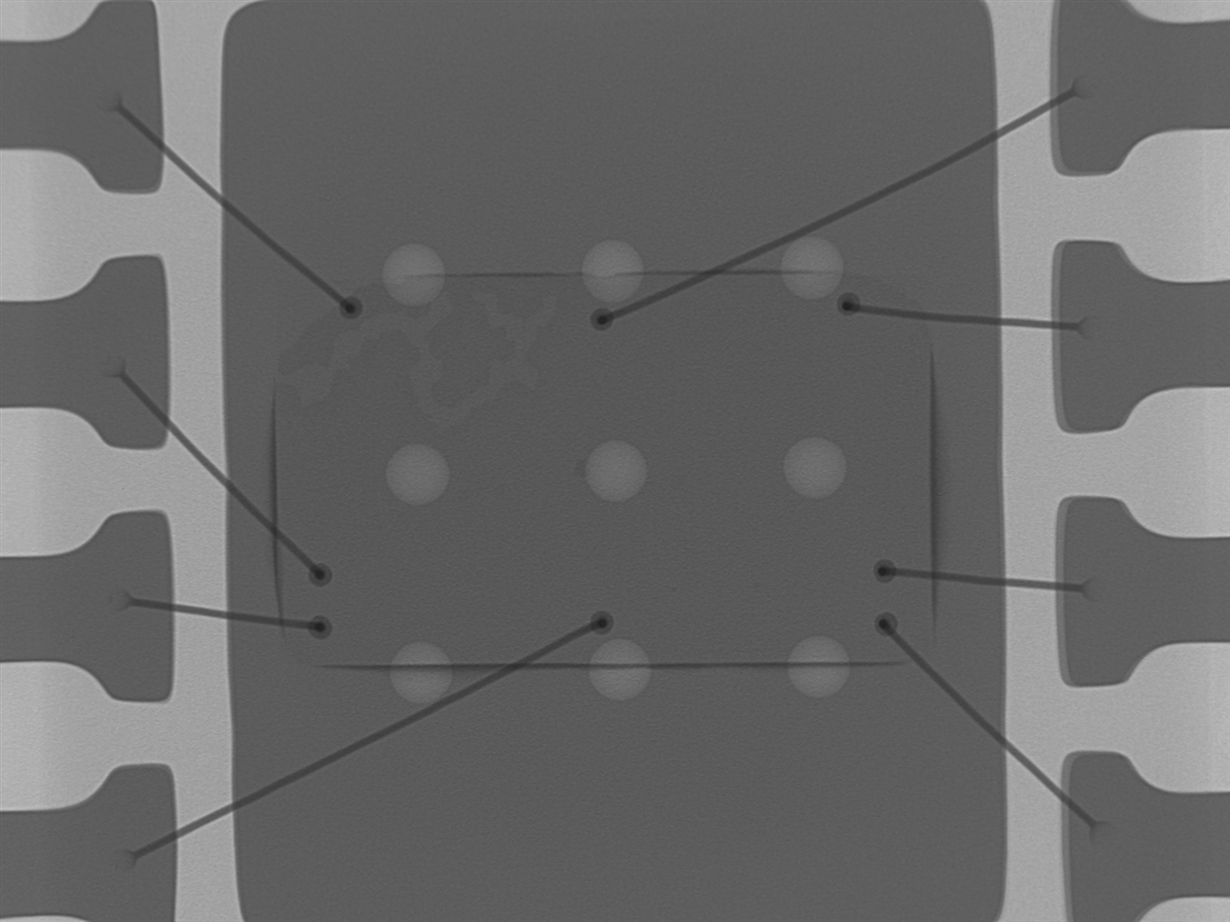

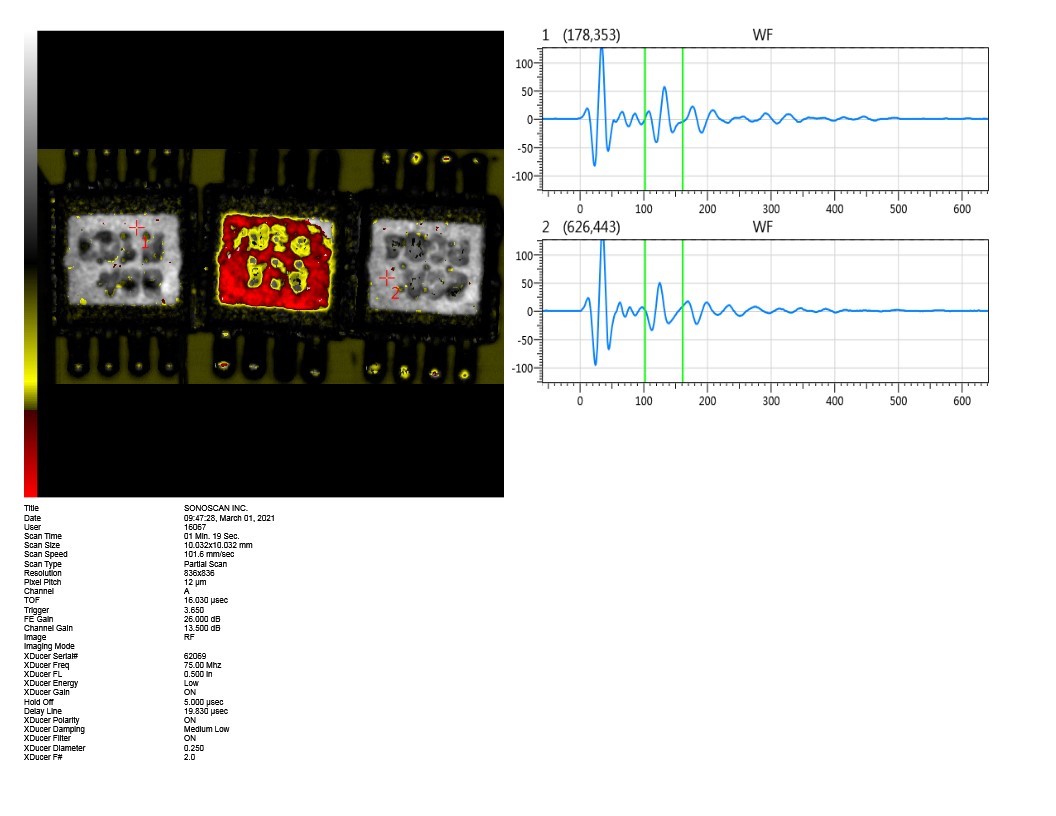

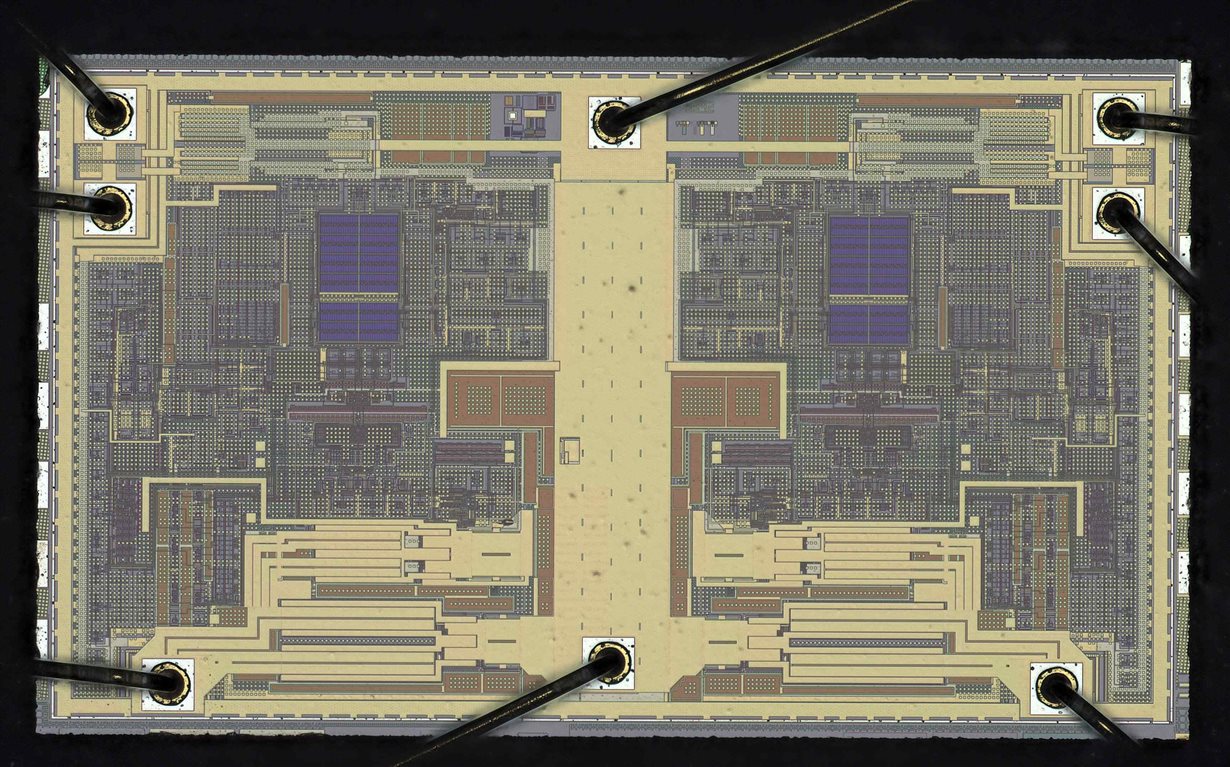

通过超声波和X-RAY分析,发现3pcs客诉品都存在以下现象:

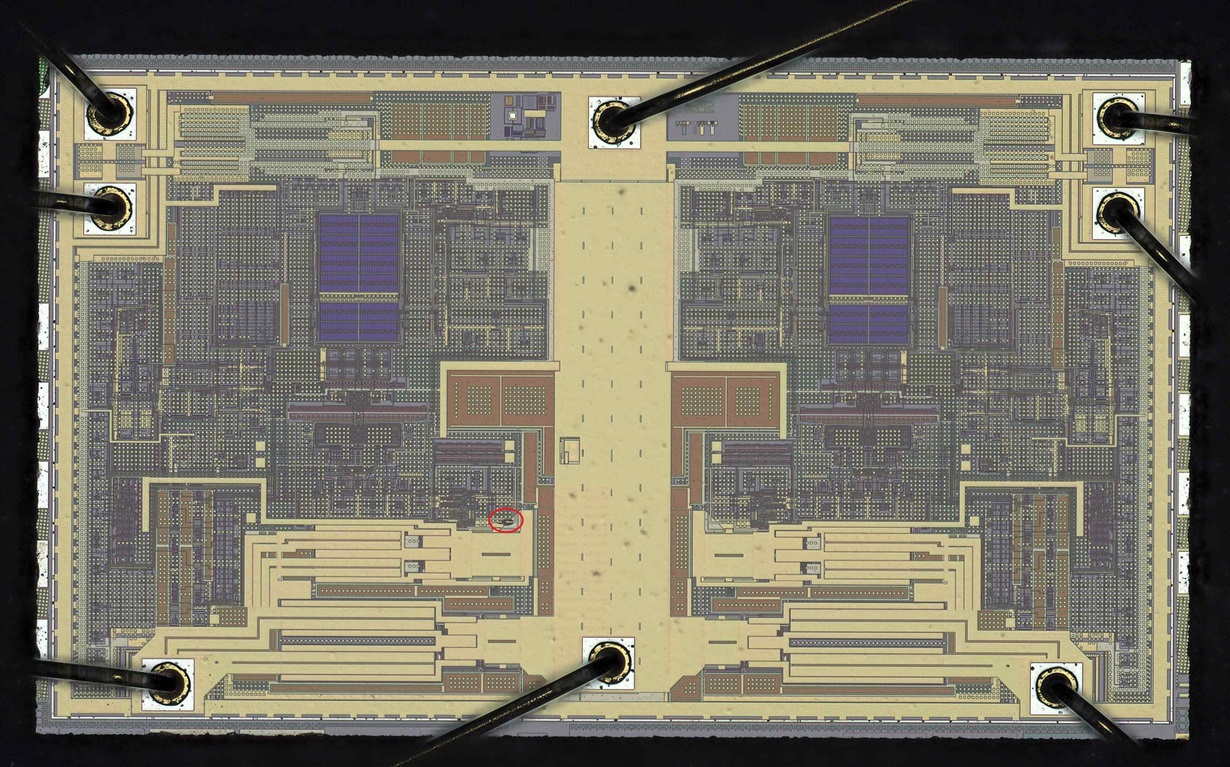

1.内层存在不明印记

2. Bottom X-ray发现分层

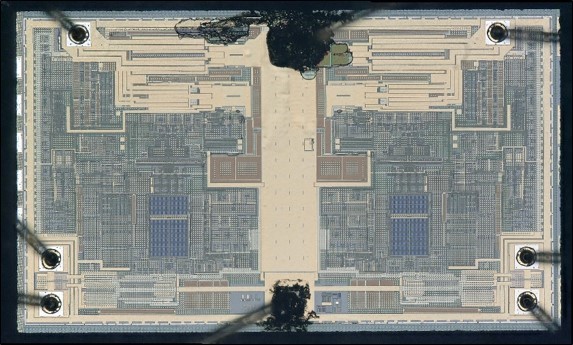

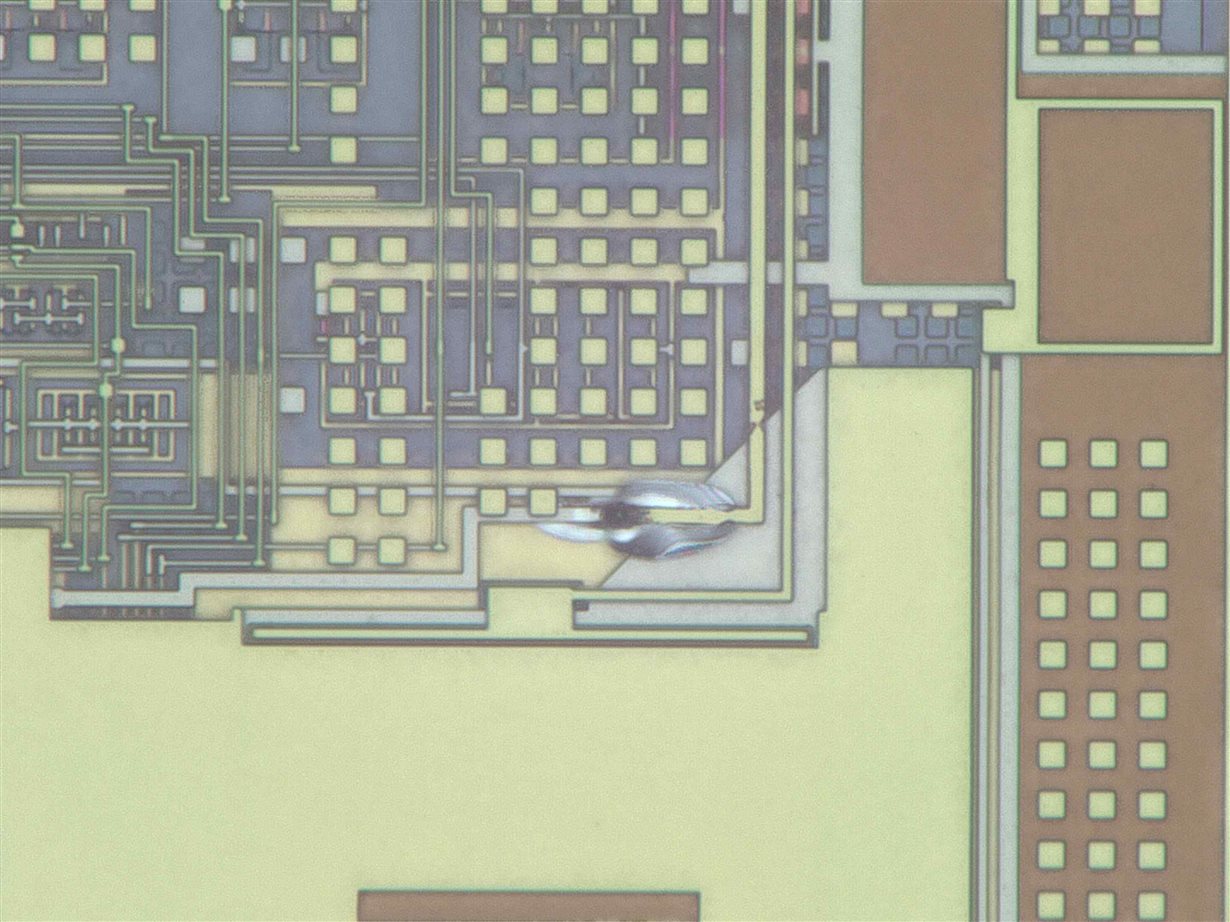

图1 是ok件,图2,图3是坏片(客诉品)

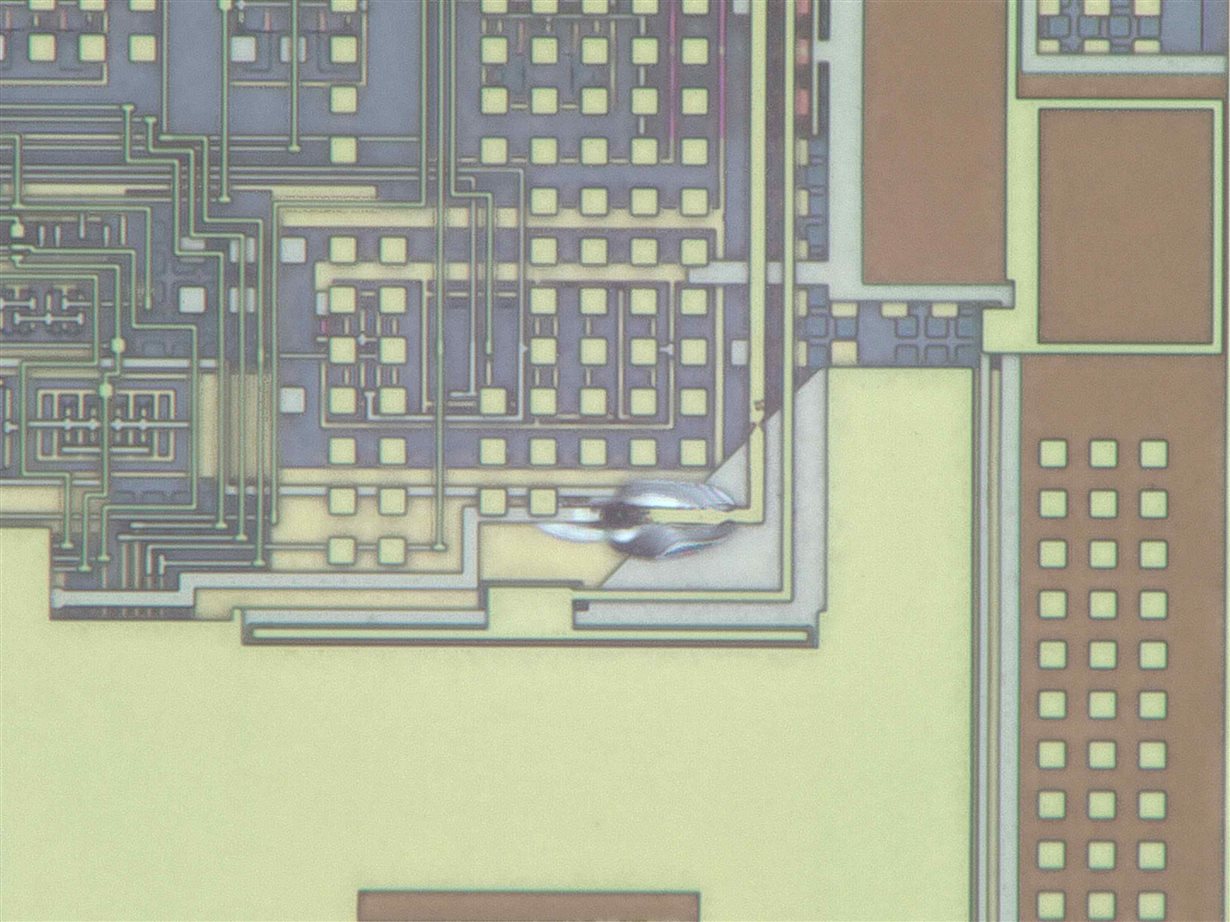

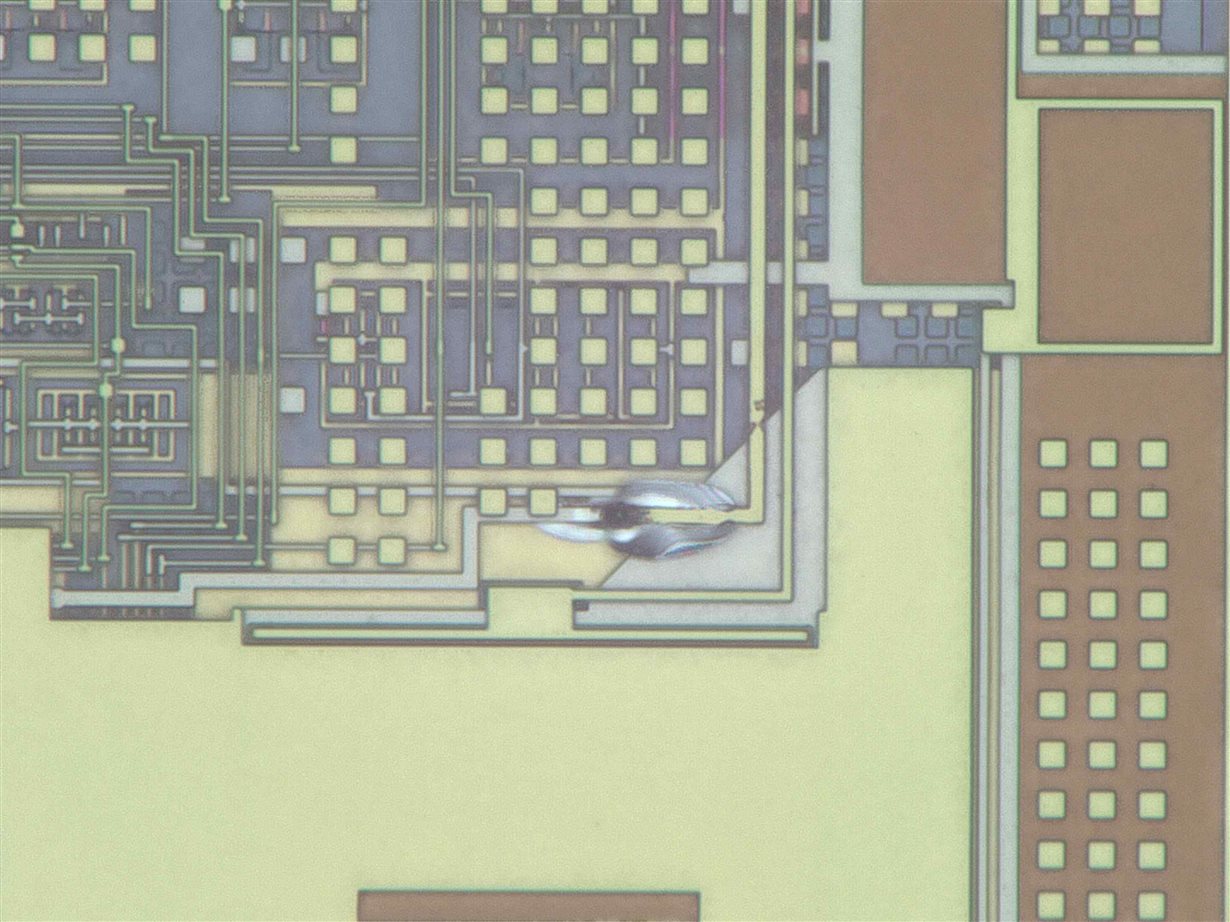

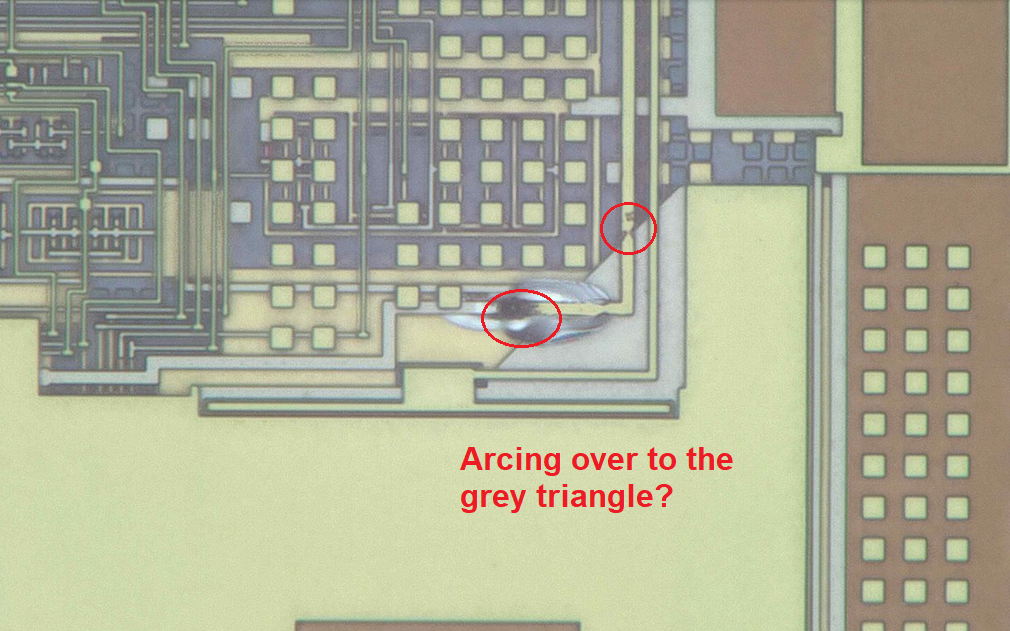

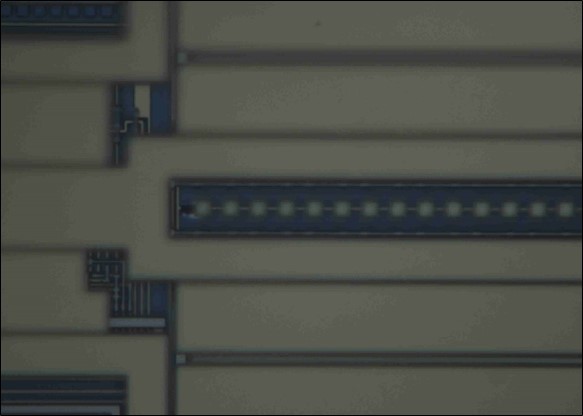

3.开片后发现筋线有腐蚀和灼烧的痕迹

4.所有开片客诉品都来自于同一批次

请协助分析导致以上结果原因,客户正在等结果,已导致延迟交货,请尽快回复。