Part Number: INA226

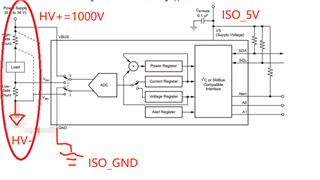

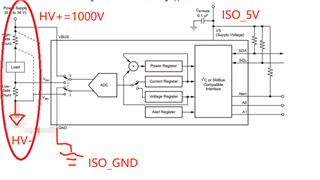

如图,系统电压等级为500--1000V电压,INA226采用隔离供电方式,INA226的芯片地与系统地不共地,VIN+/-端接在总线分流器的高端测(HIGH SIDE SHUNT),请问此种接线方式应用是否可行?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: INA226

如图,系统电压等级为500--1000V电压,INA226采用隔离供电方式,INA226的芯片地与系统地不共地,VIN+/-端接在总线分流器的高端测(HIGH SIDE SHUNT),请问此种接线方式应用是否可行?

如果您对INA226的供电隔离,同时对输入信号和输出信号也隔离,也就是对INA226整个系统都隔离起来,那么INA226系统就是浮空的,在这种情况下,我认为采用高压侧采样电流应该是没问题的,因为这样共模信号被隔离开了

如果您的输入信号没有进行隔离,同时采用高压侧采样的话,即使不共地,这应该也相当于直接对系统输入端加入了一个高压端 HV+ 的共模电压(我理解的这相当于对系统打静电)一旦系统的电荷积累到系统绝缘最薄弱处临界点,系统绝缘最薄弱处就会被击穿,发生击穿的同时会对附件器件产生损坏。同理,采用低压侧采样(不共地),这种风险小很多,因为低压侧采样,输入的共模电压很小,基本为0

以上我的分析,请仅作为参考,系统一般都是建议与被采样回路共地的。

这种情况,我认为与我说的第二种情况基本是一样的,区别仅VIN-没有接GND,即如下:

如果您的输入信号没有进行隔离,同时采用高压侧采样的话,即使不共地,这应该也相当于直接对系统输入端加入了一个高压端 HV+ 的共模电压(我理解的这相当于对系统打静电)一旦系统的电荷积累到系统绝缘最薄弱处临界点,系统绝缘最薄弱处就会被击穿,发生击穿的同时会对附件器件产生损坏。同理,采用低压侧采样(不共地),这种风险小很多,因为低压侧采样,输入的共模电压很小,基本为0

HV+端和HV-间仅串联一个很小的采样电阻,没有什么区别吧,HV+的共模电压加在INA226系统上,即使HV+电压不会击穿绝缘隔离,那么如果HV+回路上存在静电,那么这个静电在HV+的基础上又加在了INA226系统上,这样系统绝缘最薄弱处被击穿的风险就大很多

抱歉,我理解错了,我以为您说的是VIN-存在电荷累积到226电压值过高,因为VIN-和VIN+仅隔一个采样电阻,而VIN+=HV+所以VIN-约为HV+

是的,226芯片的基准地基本上就是HV+,因为INA226电源和接口都是隔离的,所以INA226整个系统的共模电压都是HV+,所以才有了我上面说的:

HV+的共模电压加在INA226系统上,即使HV+电压不会击穿绝缘隔离,那么如果HV+回路上存在静电,那么这个静电在HV+的基础上又加在了INA226系统上,这样系统绝缘最薄弱处被击穿的风险就大很多

这个共模电压不是说以INA226的地为参考点的,是以隔离侧为参考点的,虽然INA226的电源和信号是隔离的,但总的有个隔离电压,达到绝缘层的隔离电压,这个隔离层就被击穿了